White Paper

Synthetic Traffic Generator Reference Design

Overview

Supported Hardware

Our first Synthetic Traffic Generator release targets BittWare’s XUP-P3R and 250-SoC cards at 100 GbE only. We created this while we prepare for the multi-rate Ethernet hard blocks emerging from Achronix, AMD, and Intel.

Synthetic Traffic Generator is Part of Data Capture Reference Design

We are releasing the Synthetic Traffic Generator as part of our Data Capture architectural concept, starting with Data Capture release 2.0. The Traffic Generator owns the transmit side of the QSFP and Data Capture owns the receive side of the same QSFP. This allows us to put the CMAC into local loopback mode (or install a loopback cable) to use the Traffic Generator to test Data Capture. It also allows us to use a normal DAC or optical cable to send traffic to other devices.

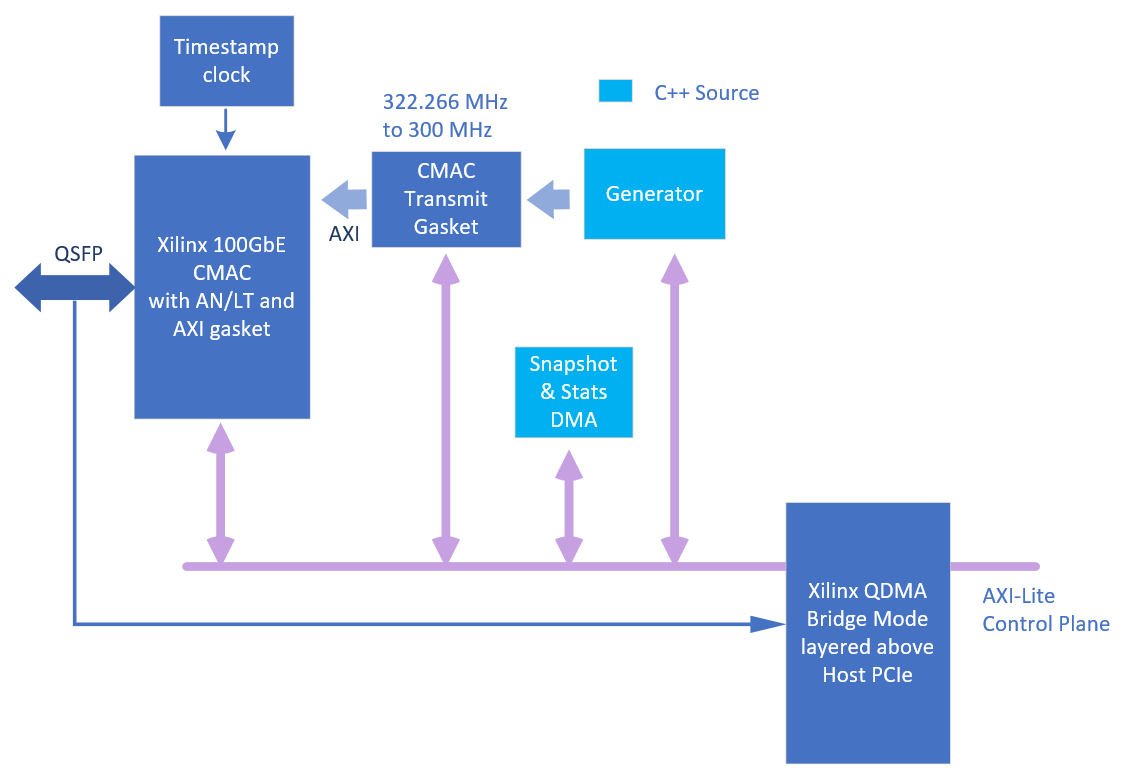

FPGA bitstream contains the pipeline diagrammed here

Functionality

BittWare’s Synthetic Traffic Generator creates Ethernet packets inside the FPGA and launches them into the attached network.

If desired, users can deploy BittWare’s separate PCIe Data Capture Reference Design to receive those packets. This, of course, assumes software configures the Traffic Generator to generate IP packets.

The basic idea is to create packets of various sizes, at line rate, for long periods of time. The packet header does not change. You can configure an increasing packet serial number inside the payload.

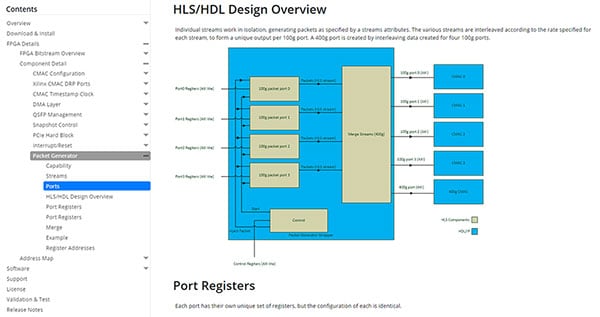

You can interleave up to 32 of these “packet streams” which means you can have up to 32 different packet headers. We need this functionality to test targets that divide received packet streams into multiple “queues” for processing using multiple host CPU cores.

You can configure random size packets but at BittWare we instead tend to sweep a design at line rate, starting with an endless series of tiny packets to verify no drops, then adding a byte to the payload, and continuing to test until we reach the biggest payload that a target design allows.

We also allow users to insert a single instance of any packet they want into an ongoing stream. This is useful for inserting an error to see what happens.

Packet streams are not required to launch at line rate as we can define a longer interpacket gap, thus reducing the packet rate. Finally, payload data can be zeros, random numbers, a repeating 64 byte pattern, or an increasing sequence (i.e. 0123456789101112…).

Hardware

This Synthetic Traffic Generator was created and tested on a BittWare XUP-P3R card containing an AMD VU9P chip, speed grade 2. The Traffic Generator does not use any external memory. The Design should port into any BittWare card with an AMD UltraScale+ chip containing a CMAC, as we demonstrated by porting the combination of Data Capture and Traffic Generator into the 250-SoC.

Resource Utilization

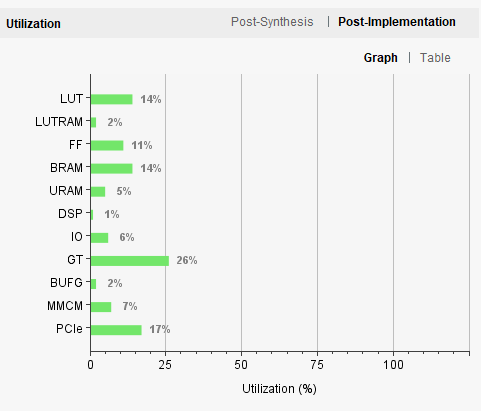

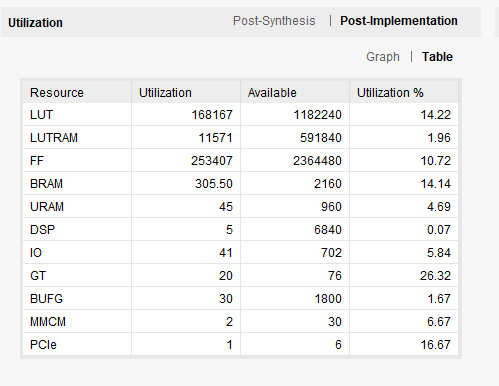

These diagrams show the FPGA resource utilization for a candidate 2.0.0 release of the Data Capture reference design (February 2021). This is likely very close to, if not exactly the version we ultimately released.

Note this bitfile includes both reference designs Traffic Generator and Data Capture.

Related Projects/Solutions

The Synthetic Traffic Generator incorporates the same DAC cable functionality demonstrated by BittWare’s simpler Loopback Example.

Another related project, StreamSurge, does not generate traffic. Instead, it sends packets out of a local memory buffer. Those packets come from the host computer, making StreamSurge a more general-purpose tool. There are two notable limits with StreamSurge. First, its memory-based design requires specialized hardware at 400 GbE. Specifically, it requires a card with both 400 GbE and HBM. Secondly, building the StreamSurge source requires licensing a third party DPDK IP block.

For full-function traffic generators, we expect to switch to Siama PROVA-C appliances as they are a great value and use BittWare hardware at 100 GbE.

Conclusion and Requesting the App Note

BittWare’s Data Capture reference design includes use of this Synthetic Traffic Generator, currently for 100 Gb/s. We wanted to share its capabilities including being able to generate proprietary sensor traffic.

To learn more, we would encourage you to request the App Note, which is the documentation for the Traffic Generator, using the form below.

There's More to Read: Get the Synthetic Traffic Generator App Note

Request PDF Download

What you see on this page is the introduction to BittWare’s Synthetic Traffic Generator. There’s a lot more detail in the full App Note! Fill in the form to request access to a PDF version of the full App Note.

"*" indicates required fields