백서

합성 트래픽 발생기 레퍼런스 디자인

개요

지원되는 하드웨어

첫 번째 합성 트래픽 생성기 릴리스는 100GbE에서 BittWare의 XUP-P3R 및 250-SoC 카드만을 대상으로 합니다. Achronix, AMD, Intel에서 출시될 멀티 레이트 이더넷 하드 블록을 준비하면서 이 제품을 만들었습니다.

합성 트래픽 생성기는 데이터 캡처 레퍼런스 디자인의 일부입니다.

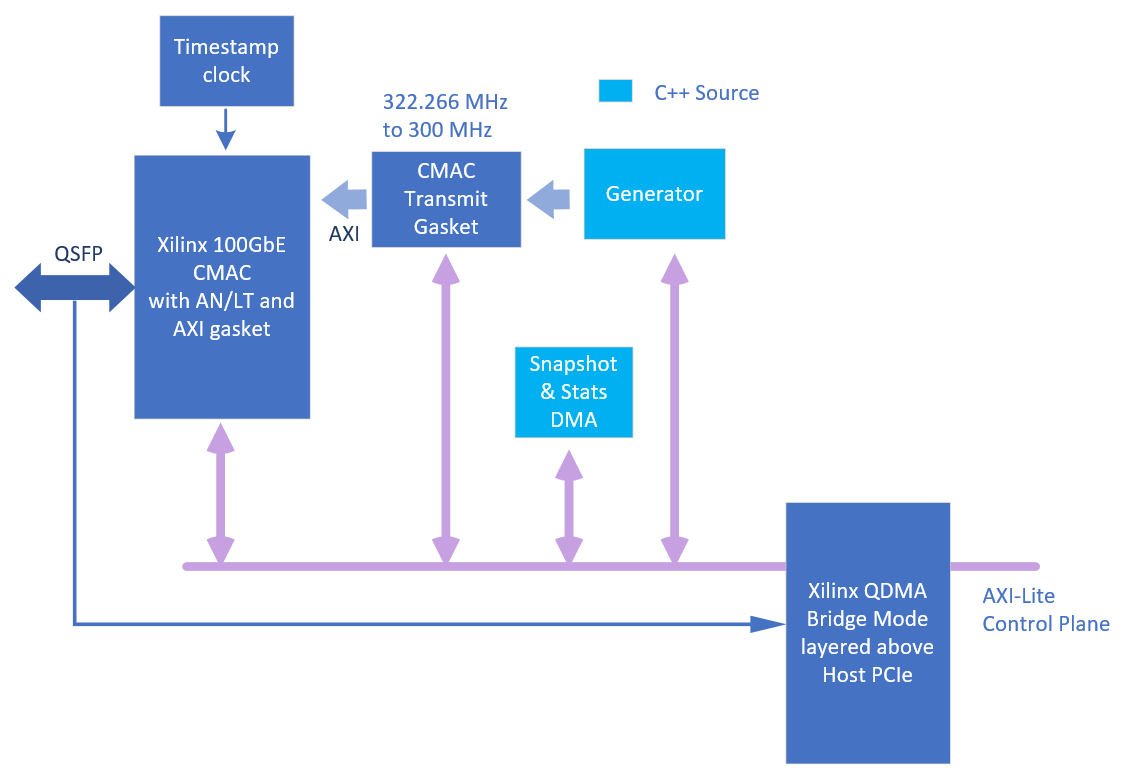

데이터 캡처 릴리스 2.0부터 데이터 캡처 아키텍처 개념의 일부로 합성 트래픽 생성기를 출시합니다. 트래픽 생성기는 QSFP의 송신 측을 소유하고, 데이터 캡처는 동일한 QSFP의 수신 측을 소유합니다. 따라서 CMAC를 로컬 루프백 모드로 전환하거나 루프백 케이블을 설치하여 트래픽 생성기를 사용하여 데이터 캡처를 테스트할 수 있습니다. 또한 일반 DAC 또는 광 케이블을 사용하여 다른 장치로 트래픽을 전송할 수 있습니다.

FPGA 비트 스트림에는 다음과 같은 파이프라인이 포함되어 있습니다.

기능

비트웨어의 합성 트래픽 생성기는 FPGA 내부에서 이더넷 패킷을 생성하여 연결된 네트워크로 전송합니다.

원하는 경우, 사용자는 BittWare의 별도의 PCIe 데이터 캡처 레퍼런스 디자인을 배포하여 해당 패킷을 수신할 수 있습니다. 물론 여기에는 소프트웨어가 IP 패킷을 생성하도록 트래픽 생성기를 구성한다는 가정이 전제됩니다.

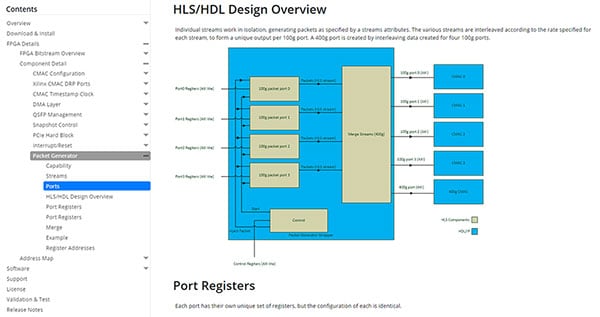

기본 아이디어는 장시간 동안 다양한 크기의 패킷을 회선 속도로 생성하는 것입니다. 패킷 헤더는 변경되지 않습니다. 페이로드 내에서 패킷 일련 번호를 늘리도록 구성할 수 있습니다.

이러한 "패킷 스트림"을 최대 32개까지 인터리빙할 수 있으므로 최대 32개의 서로 다른 패킷 헤더를 가질 수 있습니다. 수신된 패킷 스트림을 여러 호스트 CPU 코어를 사용하여 처리하기 위해 여러 "대기열"로 나누는 타깃을 테스트하려면 이 기능이 필요합니다.

임의의 크기의 패킷을 구성할 수도 있지만, BittWare에서는 대신 라인 속도로 디자인을 스윕하여 작은 패킷의 끝없는 연속으로 시작하여 드롭이 없는지 확인한 다음 페이로드에 바이트를 추가하고 목표 디자인이 허용하는 최대 페이로드에 도달할 때까지 계속 테스트하는 경향이 있습니다.

또한 사용자가 원하는 패킷의 단일 인스턴스를 진행 중인 스트림에 삽입할 수 있도록 허용합니다. 이는 오류를 삽입하여 어떤 일이 발생하는지 확인할 때 유용합니다.

패킷 스트림은 패킷 간 간격을 길게 정의하여 패킷 속도를 줄일 수 있으므로 회선 속도로 시작할 필요가 없습니다. 마지막으로 페이로드 데이터는 0, 난수, 반복되는 64바이트 패턴 또는 증가하는 시퀀스(예: 0123456789101112...)가 될 수 있습니다.

하드웨어

이 합성 트래픽 생성기는 속도 등급 2의 AMD VU9P 칩이 포함된 BittWare XUP-P3R 카드에서 생성 및 테스트되었습니다. 트래픽 생성기는 외부 메모리를 사용하지 않습니다. 데이터 캡처와 트래픽 생성기의 조합을 250-SoC에 포팅하여 시연했듯이 이 설계는 CMAC가 포함된 AMD UltraScale+ 칩이 있는 모든 BittWare 카드에 포팅할 수 있습니다.

리소스 활용

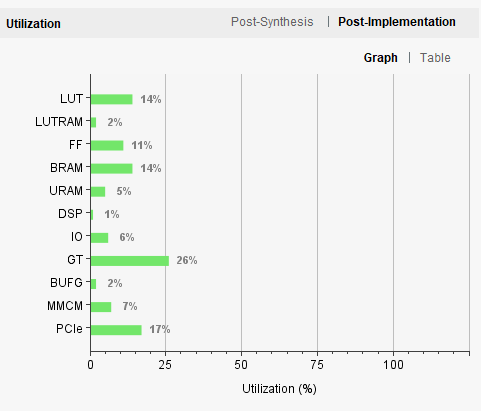

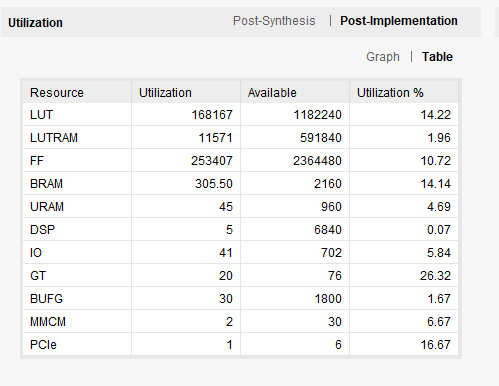

이 다이어그램은 데이터 캡처 레퍼런스 디자인 후보 2.0.0 릴리스(2021년 2월)의 FPGA 리소스 사용량을 보여줍니다. 이는 최종적으로 출시되는 버전과 정확히 일치하지는 않더라도 매우 근접할 가능성이 높습니다.

이 비트파일에는 레퍼런스 디자인 트래픽 생성기와 데이터 캡처가 모두 포함되어 있습니다.

관련 프로젝트/솔루션

합성 트래픽 생성기에는 비트웨어의 더 간단한 루프백 예시에서 보여준 것과 동일한 DAC 케이블 기능이 통합되어 있습니다.

또 다른 관련 프로젝트인 StreamSurge는 트래픽을 생성하지 않습니다. 대신 로컬 메모리 버퍼에서 패킷을 전송합니다. 이러한 패킷은 호스트 컴퓨터에서 전송되므로 StreamSurge는 보다 범용적인 도구입니다. StreamSurge에는 두 가지 주목할 만한 한계가 있습니다. 첫째, 메모리 기반 설계로 인해 400GbE의 특수 하드웨어가 필요합니다. 즉, 400GbE와 HBM을 모두 갖춘 카드가 필요합니다. 둘째, StreamSurge 소스를 구축하려면 타사 DPDK IP 블록 라이선스가 필요합니다.

모든 기능을 갖춘 트래픽 발생기의 경우, 100GbE에서 BittWare 하드웨어를 사용하는 Siama PROVA-C 어플라이언스로 전환할 것으로 예상됩니다.

결론 및 앱 노트 요청하기

비트웨어의 데이터 캡처 레퍼런스 디자인에는 현재 100Gb/s용 합성 트래픽 생성기 사용이 포함되어 있습니다. 독점적인 센서 트래픽을 생성할 수 있는 기능을 포함하여 이 기능을 공유하고자 했습니다.

자세한 내용은 아래 양식을 사용하여 트래픽 생성기 관련 문서인 앱 노트를 요청하는 것이 좋습니다.

더 읽어볼 내용이 있습니다: 합성 트래픽 생성기 앱 노트 받기

PDF 다운로드 요청

이 페이지에 표시된 내용은 BittWare의 합성 트래픽 생성기에 대한 소개입니다. 더 자세한 내용은 앱 노트 전문에서 확인할 수 있습니다! 양식을 작성하여 전체 앱 노트의 PDF 버전에 대한 액세스를 요청하세요.

"*"는 필수 필드를 나타냅니다.