인텔® oneAPI™

높은 수준의 FPGA 개발

메뉴

Deprecation Notice:

oneAPI for FPGAs is deprecated. Please reference the oneAPI page on Intel’s website for details. The previous content on this page remains but note it will be subject to out-of-date information.

oneAPI가 나에게 적합할까요?

특히 알테라 FPGA에서 하드웨어 가속기를 더 빠르고 쉽게 개발할 수 있는 방법으로 oneAPI™를 이미 알고 계실 것입니다. 하지만 모든 애플리케이션에 적합한 것은 아니며, 기준 성능을 설정하기 위해 초기 개발이 필요한 경우가 많습니다.

그렇다면 어디서부터 시작해야 할까요?

귀하의 애플리케이션이 oneAPI™의 이점을 누릴 수 있나요?

엔터프라이즈급 액셀러레이터 카드로 시작하는 것은 탁월한 선택입니다. 아래에 oneAPI를 지원하는 카드와 시작하는 데 도움이 되는 세부 정보가 나와 있습니다.

oneAPI에 대해 더 자세히 알고 싶으신가요? oneAPI에 대한 자세한 정보 섹션으로 이동하세요.

하드웨어를 구매할 준비가 되었거나 궁금한 점이 있으신가요? 구매처 및 문의처 섹션으로 이동하세요.

고성능 고급 도구의 역사

수십 년 동안 고급 FPGA 툴을 공급해 온 경험을 바탕으로 고객이 처음부터 무엇을 필요로 하는지, 즉 설계에서 F-max와 같은 주요 성능 메트릭을 평가할 수 있는 빠른 진입로가 필요한지 잘 알고 있습니다. 그렇기 때문에 표준 가속기 지원 패키지(ASP)는 고성능 컴퓨팅에 최적화되어 있습니다. oneAPI를 지원하는 BittWare 가속기 카드를 선택하면 다음과 같은 몇 가지 주요 이점을 누릴 수 있습니다:

- F-Max와 같은 핵심 성과 지표를 우선순위로 파악하세요.

- 큰 실리콘 리소스 공간에서 시작하지 말고 커스터마이징을 통해 필요한 기능만 추가하세요.

- 배포를 진행하면서 변경할 필요가 없는 배포 가능한 엔터프라이즈급 하드웨어로 시작하게 됩니다.

oneAPI를 사용한 2D FFT 데모

이 소프트웨어 지향 도구 흐름에서 더 빠르게 개발하고 코드를 재사용하세요.

HBM2가 탑재된 520N-MX 카드가 아닌 2D FFT 데모로 oneAPI를 사용해 보세요. 페이지 하단에서 코드 다운로드를 요청하세요!

oneAPI 개발을 위한 권장 카드

이 카드들은 최신 툴을 지원하고 ASP(HPC 중심)를 지원하며 각각 고성능 Altera FPGA를 탑재하고 있기 때문에 oneAPI용으로 권장합니다.

다른 비트웨어 카드도 작동하나요?

알테라 애질렉스 디바이스가 탑재된 가속기 카드는 모두 oneAPI 지원 후보이지만, 권장 카드를 선택하지 않으면 성능 평가를 위한 ASP를 구축하는 것이 중요한 개발 프로젝트가 될 것입니다.

그렇기 때문에 HPC에 최적화된 ASP가 준비된 이 카드부터 시작하는 것이 좋습니다. 대량 배포를 위한 다른 플랫폼에 대해서는 논의할 수 있습니다.

출시 예정: Agilex™ M-시리즈

oneAPI 애플리케이션을 위해 HBM2 메모리의 성능이 필요하신가요? IA-860m이 oneAPI 개발을 위한 권장 카드에 추가될 예정입니다. 준비가 되면 업데이트 소식을 받아보세요.

액셀러레이터 지원 패키지(ASP)

oneAPI 용어로 ASP(이전에는 보드 지원 패키지 또는 BSP라고 함)는 SYCL 코드와 카드의 하드웨어를 연결하는 내부 링입니다. 이 링은 기능을 활성화하고 칩의 물리적 위치(플로어 플랜)를 정의하며 특정 가속기의 범위 내에서 성능 잠재력을 결정짓는 요소입니다.

알고 계셨나요?

성능은 ASP에 따라 다릅니다.

The Accelerator Support Package (ASP) plays a big role in performance.

보드 공급업체의 특정 oneAPI 구현인 ASP는 칩과 카드 수준 모두에서 oneAPI 코드가 하드웨어 리소스와 인터페이스하는 방법을 정의합니다. 성능, 실리콘 리소스 사용량, 사용 가능한 I/O 기능에 영향을 줄 수 있는 많은 변수가 있습니다.

올바른 FPGA를 선택하는 것만큼이나 보드 공급업체를 고려하는 것도 중요합니다. 그렇기 때문에 비트웨어는 필요에 따라 기능만 추가하는 고성능 oneAPI ASP 개발을 기본으로 삼고 있습니다. 성능이 낮은(기능이 더 많을 수도 있지만) ASP로 시작하면 이상적인 결과가 나오지 않을 수 있으며, 이는 oneAPI의 실제 성능을 가릴 수 있습니다.

BittWare ASP

맞춤화를 위한 설계

고객은 필요에 따라 더 많은 기능을 사용자 지정할 수 있습니다.

ASP가 제공하는 것보다 더 많은 기능이 필요한 경우, 이미 추가 I/O를 활성화할 수 있는 엔터프라이즈급 하드웨어를 사용하고 있는 것입니다. 이러한 리소스를 oneAPI로 활성화하려면 자체 팀과 함께 수행하거나 더 많은 사용자 지정 옵션에 대해 문의하세요.

ASP 사용자 지정이 필요하신가요?

프로젝트 요구 사항을 충족하는 맞춤형 ASP를 받기 위한 견적 또는 추천을 받으려면 문의하세요.

이 용어들은 어떤 관련이 있나요?

OFS, FIM, AFU 및 ASP

관련 용어: OFS, FIM, AFU ASP가 함께 작동하는 방식

oneAPI, 오픈 FPGA 스택(OFS) 및 FPGA 인터페이스 관리자(FIM), 가속기 기능 단위(AFU)와 관련된 몇 가지 용어를 더 들어보셨을 것입니다. 이 용어들은 가속기 지원 패키지(ASP)와 어떤 관련이 있을까요? 때때로 보드 지원 패키지(BSP)에 대한 참조가 표시되는 이유는 무엇인가요?

OFS는 최상위 구성 요소이지만 하나의 API가 OFS가 제공하는 모든 것을 포함한다고 생각하지 않는 것이 중요합니다. 이러한 구현은 리소스 효율적이지 않고 유지 관리가 어렵습니다. OFS를 광범위한 기능 라이브러리로 간주하는 것이 좋으며, 특정 oneAPI 구현은 이러한 기능의 하위 집합을 제공하는 것으로 간주하는 것이 좋습니다.

그렇기 때문에 다양한 "지원 OFS" 보드를 비교할 때 어떤 기능, 성능 또는 리소스 사용량이 구현되는지에 대한 정보가 많이 제공되지 않습니다. ASP(이전의 BSP)가 어떻게 구현되는지더 자세히 살펴봐야 합니다.

다음 '레벨 다운'은 FIM, 즉 FPGA 인터페이스 관리자로 구성됩니다. 이는 FPGA 자체 및 oneAPI 소프트웨어를 포함한 하드웨어 기능에 대한 특정 인터페이스를 정의합니다. FIM은 OFS 기반 셸이라고 생각하면 됩니다. RTL 프로그래밍 리소스가 있는 경우 FIM에서 기능을 추가/제거할 수 있습니다.

FIM의 '내부'에서 작동하는 것은 가속을 제공하는 실제 알고리즘 또는 처리 장치인 AFU입니다. 소프트웨어 도구를 사용하여 개발하지만 하드웨어 인스턴스화의 이점이 있는 사용자 애플리케이션 공간이라고 생각하면 됩니다.

마지막으로 ASP는 하드웨어 인터페이스와 oneAPI 코드와의 상호 작용 방식, 개발을 위한 쿼터스 같은 호스트 소프트웨어 도구 등 이러한 구성 요소를 한데 모았습니다. BSP(보드 지원 패키지)와 oneAPI에 대한 언급을 볼 수 있는데, 이는 ASP와 비슷한 용어입니다. ASP를 가장 잘 이해하는 방법은 FIM(사용자 애플리케이션 AFU 영역 포함)을 oneAPI의 대상으로 전환하는 구성 요소라고 생각하면 됩니다.

요약: 시작하기

다음 단계는 무엇인가요? 개발에서 배포까지 일반적인 흐름은 무엇인가요?

평가

양질의 ASP를 제공하는 적합한 카드를 선택하세요.

"oneAPI"로 광고되는 모든 카드가 평가에 적합한 것은 아닙니다. 저희는 Altera F-시리즈, I-시리즈, 그리고 곧 출시될 M-시리즈 Agilex FPGA가 장착된 카드에 ASP를 구현하기로 결정했습니다. 권장 가속기 보드 목록을 확인하고 어떤 것이 가장 적합한지 논의할 준비가 되셨나요?

기본 사항을 알아보세요.

하드웨어가 준비되면 Altera 쿼터스 디자인 소프트웨어(별도 판매)와 oneAPI 툴을 사용하게 됩니다. BittWare를 사용하면 가속기 보드 구매 시 개발자 사이트에서 안내를 받을 수 있습니다.

개발

oneAPI로 더 빠르게 개발하세요.

네이티브 RTL 개발에 익숙하다면 전체 컴파일 실행이 줄어든 oneAPI가 반갑게 느껴질 것입니다. 테스트 벤치 에뮬레이션과 보고서 덕분에 이러한 단계를 몇 초/몇 분 안에 완료할 수 있습니다. 전체 컴파일로 넘어가면 Vtune을 사용하여 프로젝트를 더욱 세분화할 수 있습니다.

배포

비트웨어 액셀러레이터로 시작했다면 희소식입니다.

비트웨어 액셀러레이터로 시작하면 개발에 사용하던 것과 동일한 카드에 배포할 수 있습니다! 필요에 따라 필요한 용량에 대해 문의하세요.

oneAPI™에 대해 자세히 알아보기

oneAPI란 무엇인가요?

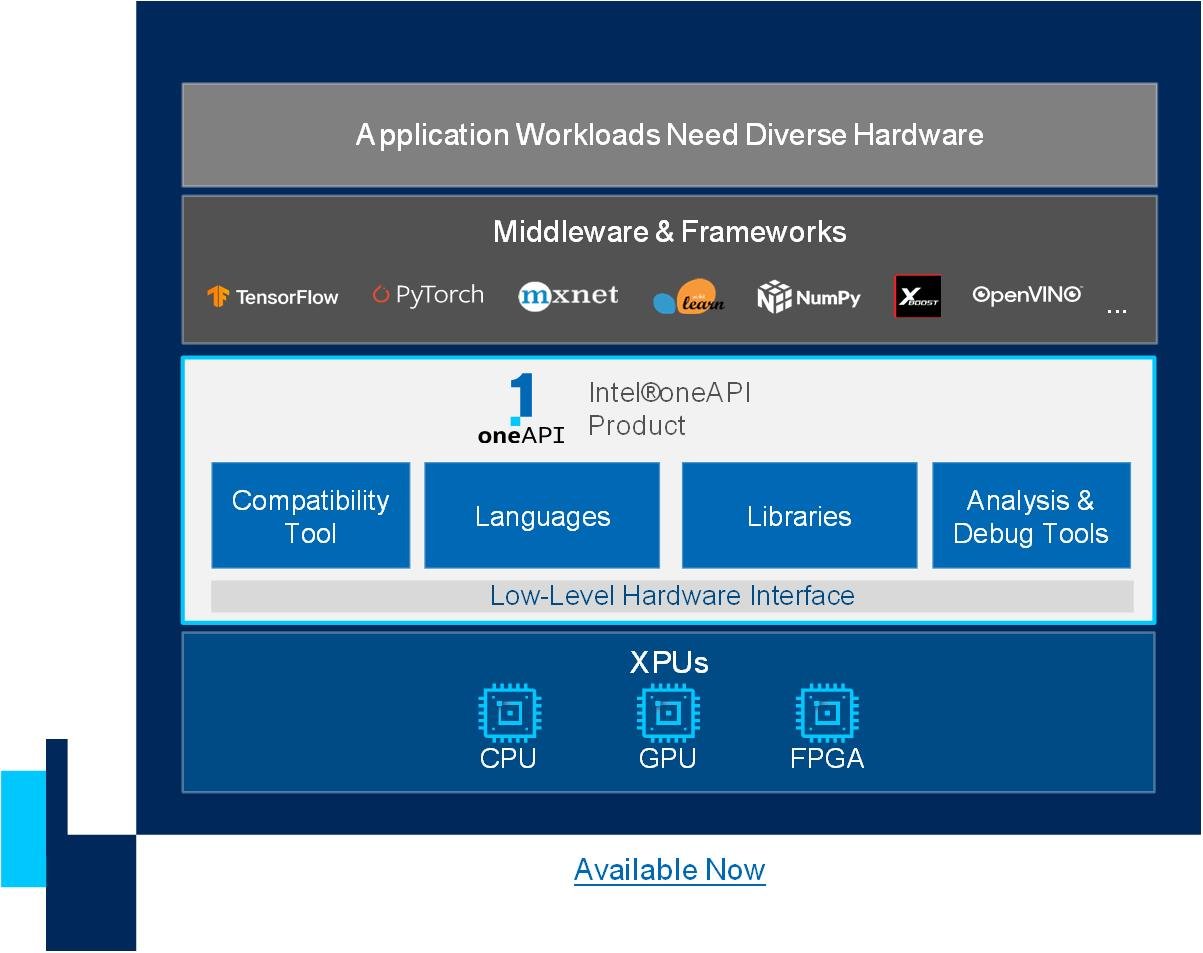

oneAPI는 업계 전반의 개방형 표준 기반 통합 프로그래밍 모델로, 가속기 아키텍처 전반에 걸쳐 공통된 개발자 경험을 제공하여 애플리케이션 성능, 생산성, 혁신성을 향상시킵니다. oneAPI 업계 이니셔티브는 생태계 전반에서 oneAPI 사양과 호환 가능한 oneAPI 구현에 대한 협업을 장려합니다.

라이브러리

oneAPI는 컴퓨팅 및 데이터 집약적인 도메인을 위한 라이브러리를 제공합니다. 여기에는 딥 러닝, 과학 컴퓨팅, 비디오 분석, 미디어 처리 등이 포함됩니다.

하드웨어 추상화 계층

사양

oneAPI 사양은 기존 개발자 프로그래밍 모델을 확장하여 크로스 아키텍처 프로그래밍을 지원하는 언어, 라이브러리 API 세트, 로우레벨 하드웨어 인터페이스를 통해 다양한 하드웨어를 사용할 수 있도록 합니다. 호환성을 촉진하고 개발자의 생산성과 혁신을 지원하기 위해 oneAPI 사양은 업계 표준을 기반으로 하며 개방형 크로스 플랫폼 개발자 스택을 제공합니다.

프로그래밍 과제

여러 아키텍처의 경우

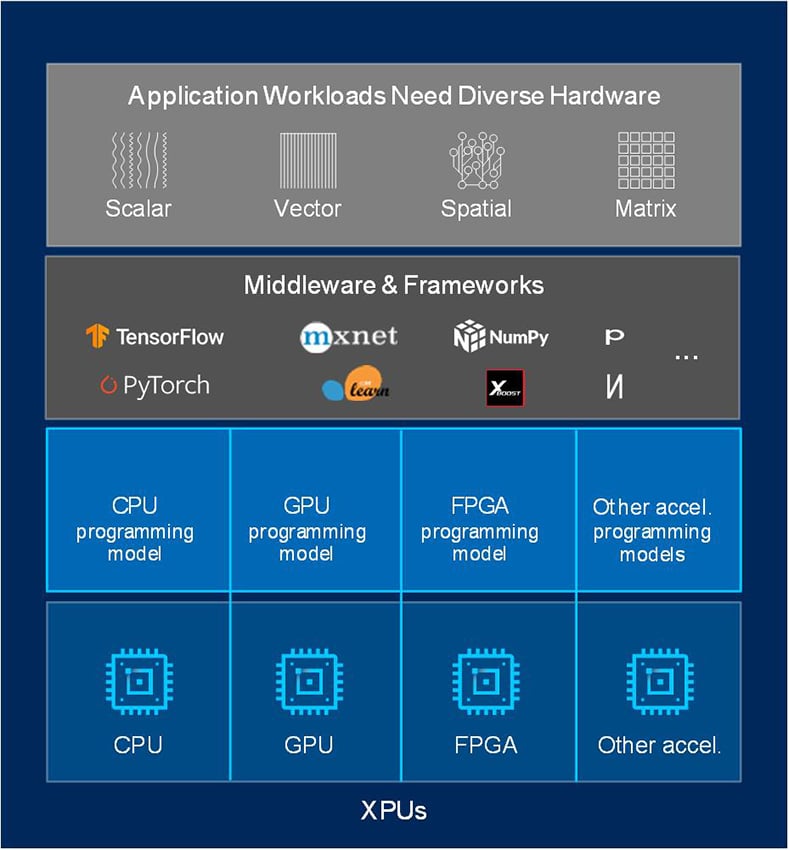

오늘날의 HPC 환경에서는 워크로드를 실행하는 데 CPU, GPU, FPGA, 전문 가속기 등 여러 하드웨어 아키텍처를 사용할 수 있습니다. 모든 워크로드에 가장 적합한 단일 아키텍처는 없으므로 여러 아키텍처를 혼합하여 사용하면 대부분의 시나리오에서 최상의 성능을 얻을 수 있습니다. 하지만 이러한 아키텍처의 다양성은 몇 가지 과제로 이어집니다:

각 아키텍처에는 별도의 프로그래밍 모델과 툴체인이 필요합니다:

- 필요한 교육 및 라이선스 - 컴파일러, IDE, 디버거, 분석/모니터링 도구, 배포 도구 - 아키텍처별

- 교차 아키텍처 소스 코드 디버그, 모니터링 및 유지 관리의 어려움

- 독점 IP 및 아키텍처 간 통합이 어렵고 코드 재사용이 불가능합니다.

소프트웨어 개발의 복잡성은 아키텍처 선택의 자유를 제한합니다.

- 진입 장벽을 극복하기 위한 기술 전문성에 필요한 단독 투자

oneAPI의 지원 방법

OneAPI는 다양한 아키텍처에서 개발을 간소화하는 통합 프로그래밍 모델을 제공합니다. oneAPI 프로그래밍 모델을 사용하면 개발자는 동일한 언어와 라이브러리를 사용하여 다양한 하드웨어 플랫폼을 타겟팅할 수 있으며, 동일한 디버그 및 성능 분석 도구 세트를 사용하여 다양한 플랫폼에서 코드를 개발하고 최적화할 수 있습니다(예: Vtune 프로파일러를 통해 호스트 및 가속기에서 런타임 데이터를 가져오는 것).

여러 플랫폼과 하드웨어 아키텍처에서 동일한 언어를 사용하면 소스 코드를 더 쉽게 재사용할 수 있으며, 코드를 다른 하드웨어 아키텍처로 옮길 때 플랫폼별 최적화가 여전히 필요한 경우에도 더 이상 코드 번역이 필요하지 않습니다. 또한 공통 언어와 도구 세트를 사용하면 신규 개발자를 더 빠르게 교육하고, 디버그를 더 빠르게 수행하며, 생산성을 높일 수 있습니다.

- 에뮬레이션 및 보고서를 통한 성능 튜닝 및 타이밍 종료

- VTune™ 프로파일러를 통한 런타임 분석

- 매크로, 프래그마, 헤더 등 기본 제공 언어 기능을 통해 구현되는 복잡한 하드웨어 패턴

- 아키텍처 및 공급업체 간 코드 재사용

- 기존 고성능 언어와 호환

- 익숙한 순차적 프로그래밍 언어 활용: 램프업 및 디버그 시간 개선

- IDE 통합: 이클립스, VS, VS 코드

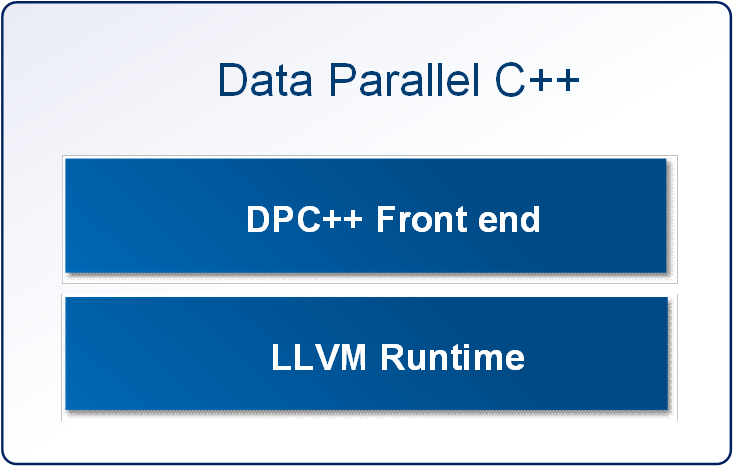

데이터 병렬 C++

표준 기반 교차 아키텍처 언어

oneAPI 언어는 병렬 프로그래밍 생산성을 위해 설계된 고급 언어이자 광범위한 호환성을 위해 C++ 언어에 기반한 데이터 병렬 C++입니다. DPC++는 독점 언어가 아니며, 개방형 업계 간 이니셔티브에 의해 개발되고 있습니다.

CPU와 가속기 전반에서 탁월한 병렬 프로그래밍 생산성과 성능을 제공하는 언어입니다:

- 특정 가속기에 대한 커스텀 튜닝을 허용하면서 하드웨어 대상에서 코드 재사용을 허용합니다.

- 단일 아키텍처 독점 언어를 대체하는 개방형, 업계 전반의 대안

C++ 기반:

- 일반적이고 친숙한 C 및 C++ 구조를 사용하여 C++ 생산성 이점 제공

- 데이터 병렬 처리 및 이기종 프로그래밍을 지원하기 위해 크로노스 그룹의 SYCL*을 통합합니다.

언어 개선을 위한 커뮤니티 프로젝트:

- 데이터 병렬 프로그래밍을 간소화하는 확장 기능

- 지속적인 진화를 위한 개방적이고 협력적인 개발

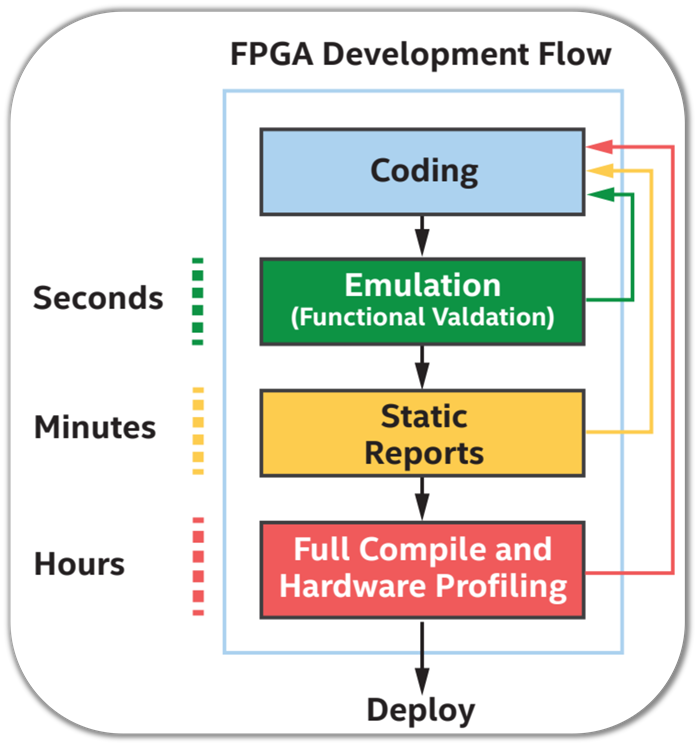

oneAPI용 FPGA 개발 흐름

FPGA용 코드를 컴파일할 때 가장 큰 문제 중 하나는 컴파일 시간입니다. DPC++ 코드를 해당 코드에 지정된 하드웨어 아키텍처를 구현하는 타이밍 폐쇄형 FPGA 디자인으로 변환하는 데 필요한 백엔드 컴파일 프로세스는 완료하는 데 몇 시간이 걸릴 수 있습니다. 따라서 FPGA 개발 흐름은 전체 컴파일 실행을 최소화하도록 조정되었습니다.

- 첫 번째 단계는 기능 검증으로, 테스트 벤치를 사용하여 코드의 정확성을 검사합니다. 이 단계는 개발 플랫폼에서 에뮬레이션을 사용하여 이루어지며, 여기서 FPGA를 대상으로 하는 코드가 CPU에서 컴파일되고 실행됩니다. 따라서 버그를 발견하고 수정해야 할 때 훨씬 더 빠른 처리 시간을 확보할 수 있습니다. 이를 위해 표준 CPU 디버거(예: GDB용 인텔® 디스트리뷰션)를 사용할 수 있습니다.

- 기능 검증이 완료되면 컴파일러에서 생성된 보고서를 통해 정적 성능 분석이 수행됩니다. 보고서에는 설계의 메모리, 성능, 데이터 흐름 병목 현상을 식별하는 데 필요한 모든 정보와 병목 현상을 해결하기 위한 최적화 기법에 대한 제안이 포함됩니다. 또한 대상 FPGA에 대한 설계의 면적 및 타이밍 추정치도 제공합니다.

- 정적 분석 결과가 만족스러우면 전체 컴파일이 수행됩니다. 컴파일러는 생성된 하드웨어에 요청 시 프로파일링 로직을 삽입할 수 있으며, 프로파일링 로직은 메모리 및 파이프 액세스에 대한 동적 프로파일링 데이터를 생성하여 나중에 다른 방법으로는 발견할 수 없는 데이터 패턴 의존적 병목 현상을 식별하는 데 Vtune 성능 분석기에서 사용할 수 있습니다.

가격이나 자세한 정보가 궁금하신가요?

기술 영업팀에서 가용성 및 구성 정보를 제공하거나 기술 관련 질문에 답변해 드립니다.

"*"는 필수 필드를 나타냅니다.