英特尔® oneAPI™

高级 FPGA 开发

菜单

Deprecation Notice:

oneAPI for FPGAs is deprecated. Please reference the oneAPI page on Intel’s website for details. The previous content on this page remains but note it will be subject to out-of-date information.

oneAPI 是否适合您?

您可能已经知道 oneAPI™ 是一种更快、更简单的硬件加速器开发方法,尤其是在 Altera FPGA 上。但是,并不是每种应用都适合,通常需要进行一些初始开发以建立基准性能。

那么,从哪里开始呢?

您的应用程序能否受益于 oneAPI™?

使用我们的企业级加速卡是一个很好的选择。以下是我们支持 oneAPI 的加速卡,以及帮助您开始使用的详细信息。

想了解有关 oneAPI 的更多详情? 跳转到我们的 "更多关于 oneAPI "部分。

准备购买硬件或有疑问? 跳转到我们的购买地点和联系方式部分。

高性能高级工具的历史

凭借数十年提供高级 FPGA 工具的经验,我们从一开始就了解客户的需求:快速上马,评估设计的 F-max 等关键性能指标。因此,我们的标准加速器支持包(ASP)针对高性能计算进行了优化。选择支持 oneAPI 的 BittWare 加速器卡作为起点的一些主要优势:

- 优先了解 F-Max 等关键性能指标。

- 避免一开始就占用大量硅资源;只通过定制增加所需的功能。

- 您使用的是可部署的企业级硬件,在部署过程中无需更换。

使用oneAPI的二维FFT演示

在这个以软件为导向的工具流程中,开发速度更快+重复使用代码

通过我们的2D FFT演示探索使用oneAPI,没有采用HBM2的520N-MX卡。请务必在页面底部申请代码下载!

我们推荐的 oneAPI 开发卡

我们推荐这些卡用于 oneAPI,因为我们有最新的工具支持、ASP(专注于高性能计算),而且每个卡都有一个高性能的 Altera FPGA。

其他 BittWare 卡也能使用吗?

我们采用 Altera Agilex 设备的加速卡都可以支持 oneAPI,但如果不选择推荐的加速卡,建立 ASP 以评估性能将是一个重大的开发项目。

因此,我们建议您从这些卡开始,因为它们已经为您准备好了经过 HPC 优化的 ASP。我们可以讨论用于批量部署的其他平台。

即将推出:Agilex™ M 系列

您的 oneAPI 应用程序需要强大的 HBM2 内存?我们的IA-860m将添加到 oneAPI 开发的推荐板卡中。请与我们联系,以便获得最新信息。

加速器支持包 (ASP)

在 oneAPI 术语中,ASP(以前称为板卡支持包或 BSP)是连接 SYCL 代码和板卡硬件的内环。它实现了各种功能,定义了 oneAPI 在芯片上的物理位置(平面图),是特定加速器性能潜力的决定性因素。

你知道吗?

性能取决于 ASP

The Accelerator Support Package (ASP) plays a big role in performance.

ASP - 电路板供应商特定的 oneAPI 实现 - 定义了 oneAPI 代码与芯片和板卡级硬件资源的接口方式。这其中存在许多变量,可能导致性能的高低、芯片资源使用的多寡以及可用的 I/O 功能。

考虑电路板供应商与选择合适的 FPGA 同样重要。这就是为什么 BittWare 将高性能 oneAPI ASP 开发作为基线,只根据需要添加功能。从性能较低的 ASP(尽管可能具有更多功能)开始可能会导致不理想的结果,从而掩盖 oneAPI 的实际性能。

BittWare ASP

专为定制而设计

客户可根据需要定制更多功能。

如果您需要的功能多于我们的 ASP 所提供的功能,您已经在使用企业级硬件,这些硬件具有可启用的额外 I/O。使用 oneAPI 启用这些资源可以由您自己的团队完成,也可以与我们讨论更多定制选项。

需要定制 ASP?

请联系我们,获取报价或建议,以获得符合您项目需求的定制 ASP。

这些术语有什么关系?

OFS、FIM、AFU 和 ASP

相关术语:OFS、FIM、AFU ASP 如何协同工作

您可能还听说过一些与 oneAPI、开放 FPGA 堆栈(OFS)和 FPGA 接口管理器(FIM)、加速器功能单元(AFU)相关的术语。这些术语与加速器支持包(ASP)有什么关系?为什么有时会提到电路板支持包 (BSP)?

OFS 是最高级别的组件,但重要的是不要认为一个应用程序接口(oneAPI)就包含了 OFS 的所有功能。这样的实现既不节约资源,又难以维护。最好将 OFS 视为一个广泛的功能库,由特定的 oneAPI 实现提供其中的一个子集。

这就是为什么在比较各种 "支持 OFS "的板卡时,并不能提供太多关于实现了 哪些功能、性能或资源使用 情况的信息。 你必须进一步 了解 ASP(以前称为 BSP)是如何实现的。

下一个 "层级 "由 FIM(FPGA 接口管理器)组成。它定义了与硬件功能(包括 FPGA 本身的功能)和 oneAPI 软件的特定接口。您可以将 FIM 视为基于 OFS 的外壳。如果您拥有 RTL 编程资源,就可以从 FIM 中添加/删除功能。

在 FIM "内部 "工作的是 AFU,即提供加速的实际算法或处理单元。您可以将其视为用户应用空间,使用软件工具进行开发,但具有硬件实例化的优势。

最后,ASP 汇集了这些组件:硬件接口及其与 oneAPI 代码的交互方式,以及用于开发的 Quartus 等主机软件工具。您会看到 BSP(电路板支持包)和 oneAPI 的提法;这是 ASP 的类似术语。将 ASP 视为将 FIM(及其用户应用程序 AFU 区域)转化为 oneAPI 目标的组件的最佳方式。

摘要:入门

下一步是什么?从开发到部署的典型流程是什么?

评估

开发

使用 oneAPI 加快开发速度。

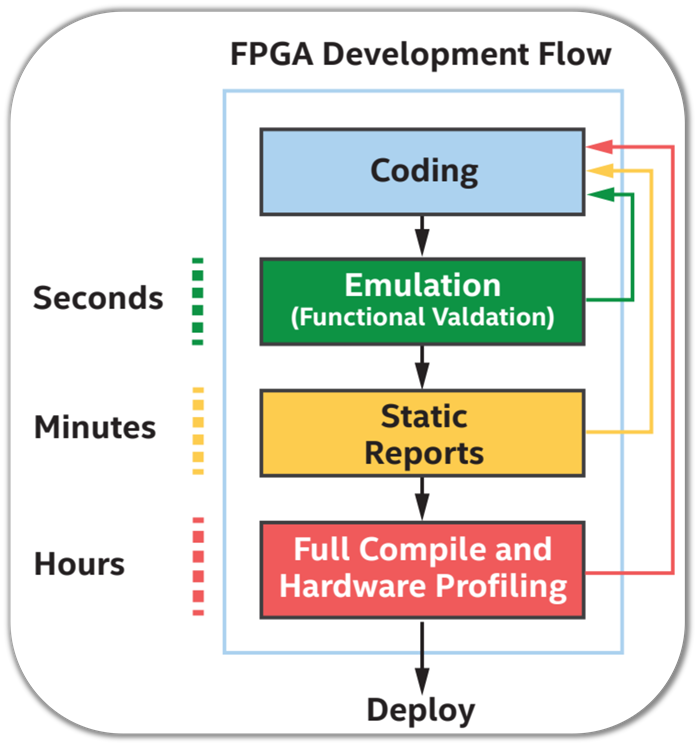

如果您习惯于本地 RTL 开发,那么 oneAPI 将是一个值得欢迎的改进,因为它可以减少完整的编译运行。借助测试台仿真和报告,这些步骤可在几秒/几分钟内完成。进入全面编译后,您可以使用 Vtune 进一步完善您的项目。

部署

如果您使用的是 BittWare 加速器,那么这将是个好消息。

从 BittWare 加速器开始,您可以在开发过程中使用的相同板卡上进行部署!请根据您的需求向我们咨询容量要求。

进一步了解 oneAPI™

什么是oneAPI?

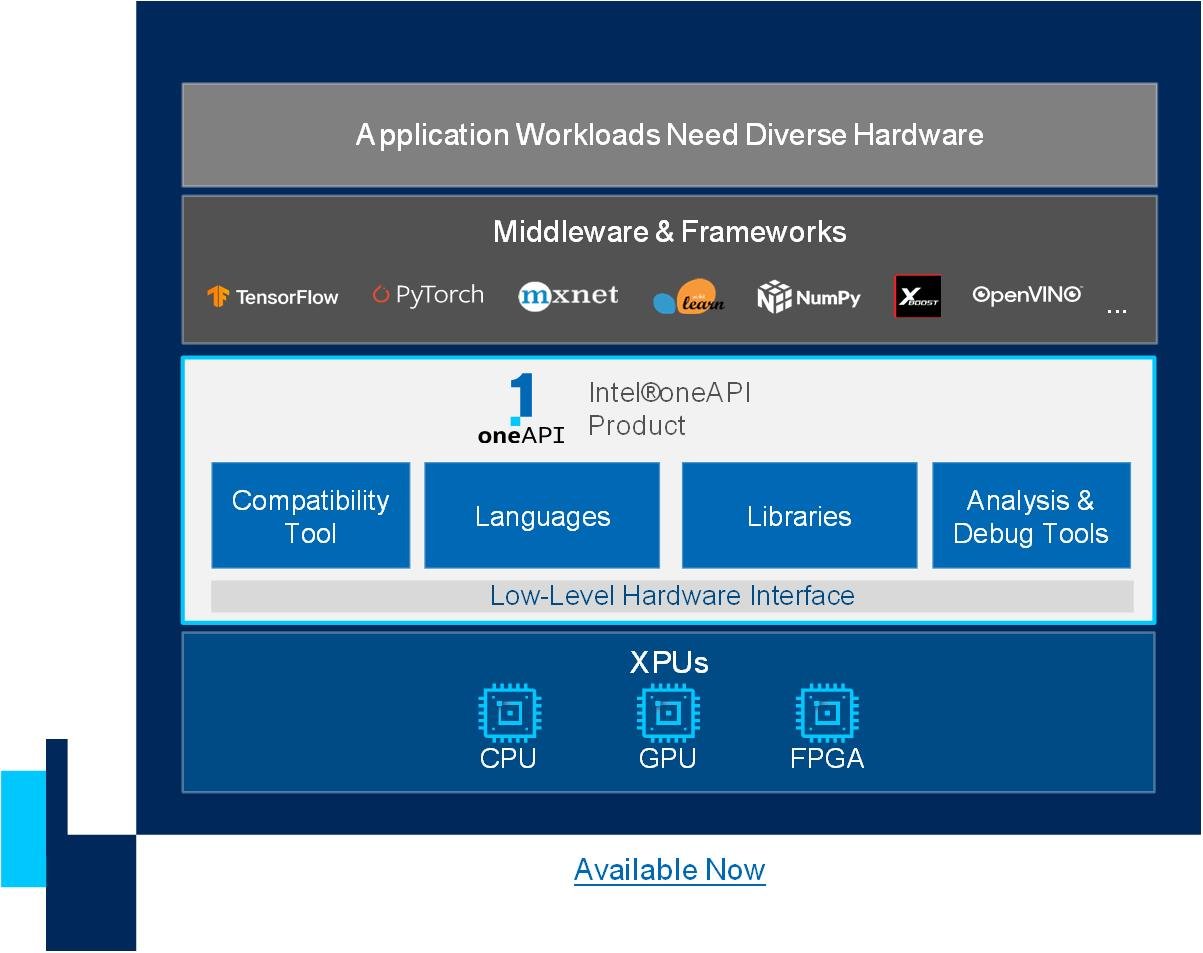

oneAPI是一个跨行业的、开放的、基于标准的统一编程模型,提供跨加速器架构的共同开发者体验--更快的应用性能、更多的生产力和更大的创新。oneAPI行业倡议鼓励在整个生态系统中就oneAPI规范和兼容的oneAPI实施进行合作。

图书馆

oneAPI为计算和数据密集型领域提供库。它们包括深度学习、科学计算、视频分析和媒体处理。

硬件抽象层

规格

oneAPI规范扩展了现有的开发者编程模型,通过语言、一套库API和一个低级硬件接口来支持跨架构编程,从而实现多样化的硬件。为了促进兼容性并使开发者的生产力和创新,oneAPI规范建立在行业标准的基础上,并提供一个开放的、跨平台的开发者堆栈。

编程挑战

适用于多种架构

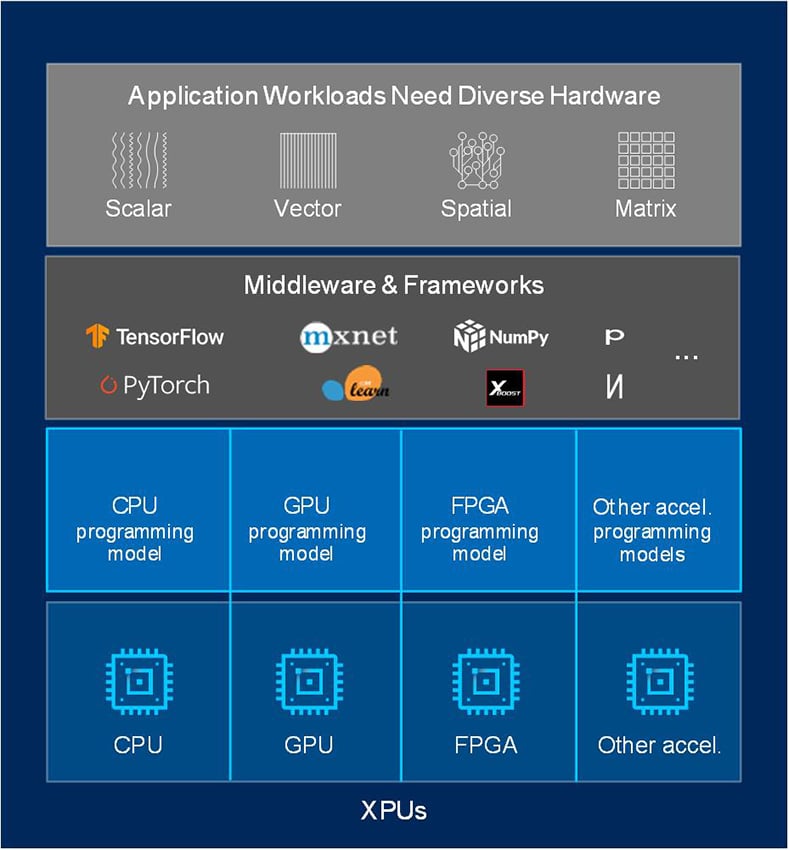

在今天的HPC领域,有几种硬件架构可用于运行工作负载--CPU、GPU、FPGA和专用加速器。没有一个架构是最适合每一个工作负载的,因此,使用混合架构可以在大多数情况下获得最佳性能。然而,这种架构的多样性导致了一些挑战:

每个架构都需要单独的编程模型和工具链:

- 所需的培训和许可 - 编译器、IDE、调试器、分析/监测工具、部署工具 - 每个架构都需要

- 调试、监控和维护跨架构的源代码,这很有挑战性

- 难以跨越专有IP和架构进行整合,没有代码重用

软件开发的复杂性限制了架构选择的自由。

- 为克服进入壁垒,需要对技术专长进行孤立的投资

oneAPI如何提供帮助

OneAPI提供了一个统一的编程模型,简化了不同架构的开发。通过oneAPI编程模型,开发人员可以用相同的语言和库瞄准不同的硬件平台,并可以使用同一套调试和性能分析工具在不同的平台上开发和优化代码--例如,通过Vtune剖析器获得跨越其主机和加速器的运行时间数据。

在不同的平台和硬件架构上使用相同的语言,使得源代码更容易被重用;即使在代码被转移到不同的硬件架构上时,仍然需要进行平台特定的优化,也不再需要进行代码翻译。而且,使用共同的语言和工具集会使新的开发人员的培训更快,调试更快,生产率更高。

- 通过仿真和报告进行性能调优和时间封闭

- 通过VTune™ Profiler进行运行时分析

- 通过内置的语言功能实现复杂的硬件模式:宏、语义、标头

- 跨架构和供应商的代码重用

- 与现有的高性能语言兼容

- 充分利用熟悉的顺序编程语言:改善提升和调试时间

- IDE整合:Eclipse,VS,VS Code

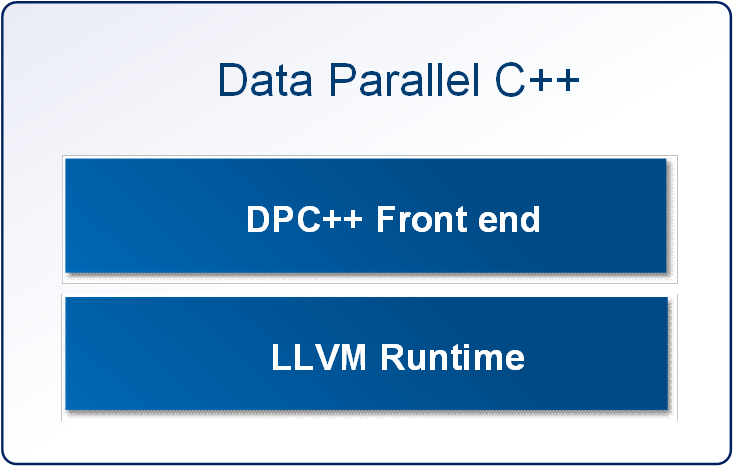

数据并行C++

基于标准的跨架构语言

oneAPI语言是数据并行C++,这是一种为并行编程生产力而设计的高级语言,基于C++语言以获得广泛的兼容性。DPC++不是一种专有的语言;它的发展是由一个开放的跨行业倡议所驱动的。

语言,在CPU和加速器上提供不折不扣的并行编程生产力和性能:

- 允许跨硬件目标的代码重用,同时允许为特定的加速器进行定制调整

- 开放的、跨行业的、替代单一架构的专有语言

以C++为基础:

- 使用常见和熟悉的C和C++结构,提供了C++的生产力优势

- 纳入了Khronos集团的SYCL*,支持数据并行和异构编程

社区项目,以推动语言的提升:

- 简化数据并行编程的扩展

- 开放和合作的发展促进持续发展

oneAPI的FPGA开发流程

为FPGA编译代码时的主要问题之一是编译时间--将DPC++代码转化为实现该代码指定的硬件结构的时序封闭的FPGA设计所需的后端编译过程可能需要几个小时才能完成。因此,FPGA的开发流程已经被定制,以尽量减少完整的编译运行。

- 第一步是功能验证,即使用测试台检查代码的正确性。这是在开发平台上使用仿真进行的--针对FPGA的代码在CPU上被编译和执行。当发现错误并需要修复时,这可以使周转时间快得多。为此可以使用标准的CPU调试器(如Intel® Distribution for GDB)。

- 一旦功能验证完成,静态性能分析将通过编译器生成的报告进行。报告包括识别设计中的内存、性能、数据流瓶颈所需的所有信息,以及解决瓶颈的优化技术建议。它们还提供了目标FPGA设计的面积和时间估计。

- 在静态分析的结果令人满意后,会进行全面的编译。编译器可以根据要求在生成的硬件中插入剖析逻辑;剖析逻辑产生内存和管道访问的动态剖析数据,随后可以被Vtune性能分析器用来识别无法以任何其他方式发现的依赖数据模式的瓶颈。

对价格或更多信息感兴趣?

我们的技术销售团队随时准备提供可用性和配置信息,或回答您的技术问题。

"*"表示必填项目