白皮书

二进制加权神经网络推理的FPGA加速

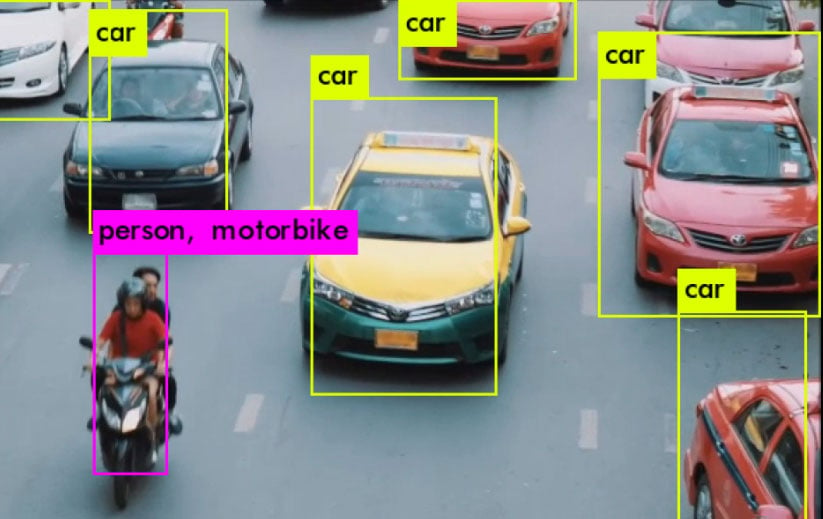

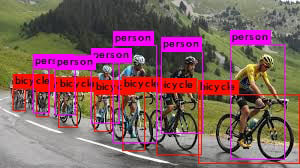

YOLOv3的特点之一是在一张图像中识别多个物体。我们使用这个网络是因为它是一个更复杂、更精密的方法,将挑战适应有限边缘环境的能力。

今天的FPGA在数据中心和边缘环境中的需求正在迅速增长。这是由于性能的进步,使用更容易的FPGA开发工具,以及对根据特定应用定制硬件加速的灵活性的需求不断增加。FPGA加速器解决方案通常与CPU一起工作,是异质计算方法的一部分,侧重于灵活的应用性能,适合最终用户的要求。

在这篇白皮书中,我们解释了这样一个应用:使用最近的基于机器学习的图像识别系统(YOLOv3)进行交通监控,该系统使用OpenCL适应BittWare 520N加速器板和Intel Stratix 10 FPGA。我们研究了提到的作为FPGA关键驱动因素的三个方面:相对于CPU的性能,使用OpenCL而不是HDL的开发便利性,以及定制应用的灵活性(在这个可变的计算精度中包括单比特二进制权重),以使用最小的功率/资源。

对机器学习的需求不断增长

直到十年前,人工智能几乎只停留在学术界、研究机构和科幻小说的领域。最近,人们意识到机器学习(ML)技术可以实际地、经济地、大规模地应用于解决现实世界的应用问题,从而形成了一个充满活力的市场参与者的生态体系。

然而,任何关于机器学习突破的消息都要与这样一个现实相权衡,即这是一种非常重计算的解决问题的方法,无论是在数据集的训练阶段还是所谓的推理阶段--即未知输入转化为推理输出的 "运行时间"。虽然机器学习应用的训练阶段只需要在数据中心发生一次,而且时间段不受限制,往往延长到几小时或几天,但实时推理必须在系统边缘的受限硬件平台上,在几分之一秒内发生。

本白皮书的PDF版本

为了使机器学习的采用率增长,必须开发推理解决方案,能够在硬件中快速实现最新的机器学习库,并能根据应用需求进行定制。

灵活的FPGA

减少机器学习推理所需的硅片数量(因此是功率)的一个方法是减少计算的动态范围。例如,从32位减少到16位的浮点运算,只是稍微降低了识别精度的应用性能,却可以大大降低硬件要求。

如果我们走得更远呢?这就是FPGA的优势所在,因为随着所需位数的减少,甚至减少到一个二进制位,硬件结构会适应,只使用需要的部分。我们也可以在项目中使用可变精度,包括在需要时使用Stratix 10 FPGA上的硬化浮点DSP逻辑块。FPGA允许设计者拥有一系列的工具,以最佳方式使硬件满足应用要求。

事实上,我们的研究重点是只使用二进制权重进行机器学习:权重被二进制化,只有两个值:+1和-1。虽然许多基于图像的机器学习应用使用一系列卷积运算,统称为卷积神经网络(CNN),但这种新的CNN变体被更具体地称为二进制加权神经网络(BWNN)。它将卷积层和全连接层中的所有定点乘法操作减少为整数加法。

关于作者

Richard Chamberlain是BittWare的系统架构师。Richard负责处理OpenCL开发项目,在FPGA的高级编程方面有丰富的工作经验。他经常就新设计的最佳硬件和开发方法向客户提供建议,或围绕其他系统类型(如CPU或GPU)调整设计。

空标题

这项研究的另一个关键部分是利用520N的OpenCL支持,将硬件开发过程抽象为类似软件的工具流程。这使得最新的应用库可以作为硬件加速的基础--减少了使用传统HDL方法针对特定设备和ML库所需的数月或更长时间(在此期间可能会发布更新的、性能更好的ML库)。例如,这篇白皮书源于我们在基于BittWare Arria 10的电路板385A-SoC上为OPERA项目做的工作。我们的开发团队迅速将OpenCL代码从该设备转移到更大更快的Stratix 10结构上。

可变精度,使用DSP进行浮点运算,以及使用OpenCL进行开发,这些都是为应用量身定做的硬件解决方案,但具有类似软件的开发速度。

二进制神经网络

在CNN网络中处理卷积需要存储和处理数百万的系数。传统上,这些系数中的每一个都是以完整的单精度表示来存储的。研究人员已经证明,系数可以被降低到半精度,而不会对整体精度有任何明显的改变,同时减少所需的存储量和内存带宽要求。目前,大多数预训练的CNN模型都使用了部分降低精度。

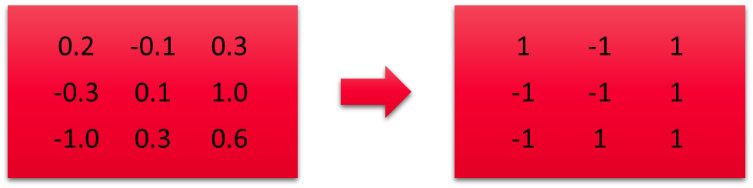

然而,通过使用不同的方法来训练这些系数,位精度可以减少到一个位,再加上一个缩放系数(参考)。在训练过程中,浮点系数被转换为二进制值,代表一个值是否大于或小于所有输入系数的平均值。这可以表示为二进制符号中的1,0(图1)。然后,卷积的输出被乘以平均值。

图1:将权重转换为二进制(平均值=0.12)。

FPGA优化

首先,权重的二进制化将外部存储器的带宽和存储要求降低了32倍。FPGA结构可以利用这种二进制化,因为每个内部存储器块可以被配置为具有1到32位的端口宽度。因此,用于存储权重的FPGA内部资源大大减少,为任务的并行化提供了更多空间。

网络的二进制化也允许CNN卷积被表示为输入激活的一系列加减法。如果权重是二进制的0,输入就会从结果中减去;如果权重是二进制的1,就会加到结果中。FPGA中的每个逻辑元件都有额外的携带链逻辑,可以有效地执行几乎任何比特长度的整数加法。有效利用这些元件可以使一个FPGA执行数以万计的并行加法。要做到这一点,浮点输入激活必须被转换为固定精度。利用FPGA结构的灵活性,我们可以调整固定加法所使用的比特数,以满足CNN的要求。对各种CNN中激活的动态范围的分析表明,只需要少量的比特,通常是8比特,就可以将精度保持在浮点等效设计的1%以内。位的数量可以增加,以获得更多的精度。

有许多不同的网络可以用于研究BNN的应用,从许多较简单的网络中挑选一个,如AlexNet,是很有诱惑力的。然而,为了真正了解FPGA对BWNN处理的有效性,最好使用最先进的网络,如YOLOv3。这是一个具有许多卷积层的大型卷积网络。

YOLOv3是一个深度网络,由于定点取整而引入的误差比AlexNet等较小的网络需要更多的位数来进行每次加法。FPGA技术的优势在于能够修改所需的精确比特数。在我们的设计中,我们用16位来表示层间传输的数据。

将卷积转换为定点,并通过二进制化消除对乘法的需求,大大减少了FPGA内所需的逻辑资源。因此,与单精度或半精度实现相比,在相同的FPGA中可以进行更多的处理,或者将FPGA逻辑释放出来用于其他处理。

有针对性的网络培训

YOLOv3网络是一个有106层的大型卷积网络,它不仅可以识别物体,还可以在这些物体周围放置边界框。它在需要跟踪物体的应用中特别有用。

如果经过适当的训练,二进制加权网络仅会略微降低YOLOv3网络的准确性。下表说明了重新训练的YOLOv3网络获得的结果。

在这张图片上,自行车的平均置信度为76%,人的平均置信度为82%。与同一图像上的浮点法相比,它对自行车的平均准确度为92%(好16%),对人的平均准确度为88%(好6%)。

为了实现FPGA的最佳性能,将目标放在最适合FPGA的网络特征上是有帮助的。在这种情况下,不仅对网络进行了二进制权重训练,还选择了适当的激活类型,以有效地映射到FPGA逻辑。

空标题

为Stratix 10设计

OpenCL是一种流行的语言,用于表达CPU、GPGPU和FPGA中的并行性。在这里,英特尔FPGA OpenCL编译器被用来对针对英特尔Stratix 10设备的加速器进行编程。本白皮书的目标FPGA加速器是BittWare 520N板。

FPGA设计的性能取决于许多因素,包括但不限于::

- 设备速度等级

- 设计中组合逻辑的深度

- 设计的扇形(多个点之间共享的信号的数量)

- 由于设备人数过多而造成的路由拥堵

- 全局内存带宽

Stratix 10设备非常大,比以前的设备更容易受到这些问题的影响。下面几段将更详细地讨论这些问题。

图2:BittWare 520N FPGA加速器板

组合逻辑深度:英特尔OpenCL工具会在可能的情况下自动进行流水线设计,插入所需的注册,以便在Stratix 10上实现最佳性能。但是,如果设计中存在反馈,则不一定能进行注册。这通常发生在创建具有自我依赖性的复杂索引要求时。因此,有必要在可能的情况下构建代码,以避免任何这样的流水线依赖;否则,设计的时钟频率会被这些路径所支配。

扇出:扇出指的是有一个单一来源但有多个端点的信号。这可能会给路由工具带来问题,因为设备上可使用的网路数量有限。这些路由的拥堵要求一些信号绕过拥堵点,导致路径变长,最终导致时钟频率变慢。通过在编码时意识到在设计的多个部分之间共享变量的影响,可以减少扇出。

过度拥挤:有一种将尽可能多的逻辑塞进设计中的诱惑;然而,随着器件的大量填充,设计时钟频率将开始降低。这是由于大量的信号试图在FPGA周围寻找路线而导致的路由拥堵。为了使大型设计达到较高的时钟频率,它们必须进行大量的流水线,并避免高扇出。

存储器带宽:在本地FPGA存储器中并不总是能够存储足够的数据,数据必须从外部深层存储器中写入或读取。520N有4组DDR4存储器,总的存储器带宽约为98GBytes/Sec。考虑到S10器件的大小,这个带宽不足以让所有的神经网络层都有数据;因此必须尽可能地重复使用输入数据。幸运的是,CNN代码允许大量的数据重复使用。使用HBM2版本的Stratix 10,例如BittWare的520N-MX板,可以在一定程度上缓解这个问题。

最终,大多数设计都是上述内容的折中,这里描述的BNN设计也不例外。

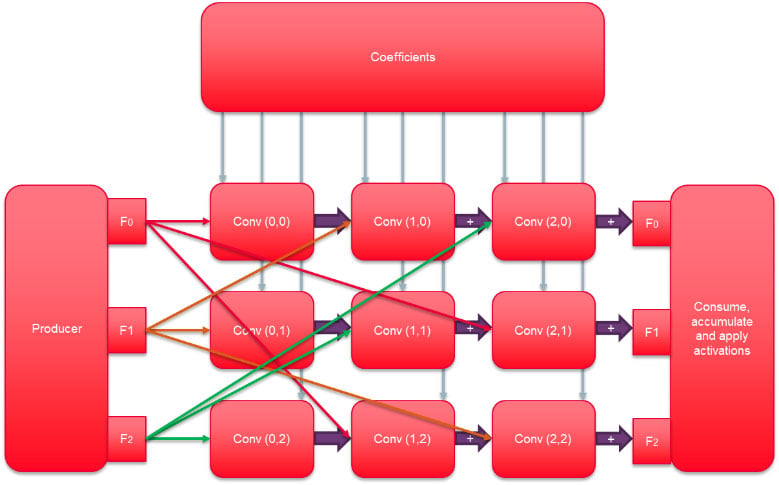

图3显示了设计的主要处理元素,即卷积路径。在可能的情况下,数据已被流水线输送到3个累积路径。每个卷积块执行一个32×32的二进制权重卷积块,其中32个输入中的每一个都由所有32个输出共享。这当然会造成高扇出,但减少了对外部存储器带宽的压力。通过将本来是96×96的卷积细分为32×32的多个块,扇出路由被限制在每个块内,减少了设计的整体扇出。输入数据通过OpenCL管道传递给每个卷积块,允许编译器在需要时插入额外的注册。

图3所示的 "生产者"、"消费者 "和 "系数 "内核将数据从全局存储器传递给不同的卷积块。消费者块也对输出进行浮点激活函数。

表1列出了执行1024次16位累积所需的资源,这些累积代表了每个32×32的卷积。

储存所有输入和输出特征数据所需的存储量超过了FPGA器件上的可用容量,即使是在使用16位数据时也是如此。因此,数据需要从附加的全局存储器中分批复制到本地FPGA存储器中,一旦并行卷积的数量增加到超过全局存储器所能支持的程度,这最终会支配性能。

| ALMs | 登记册 | 行动 |

|---|---|---|

| 35305 (2%) | 41601 (2%) | 2048 |

表1:32×32卷积矩阵的Stratix 10资源

| (ALMs) | 兆赫 | 峰值托普 | 与 OpenMP 32线程的速度比较 (Xeon CPU D-1587 1.7 GHz) |

|---|---|---|---|

| 536,122 (57%) | 300 | 5.5 | 50x |

储存所有输入和输出特征数据所需的存储量超过了FPGA器件上的可用容量,即使是在使用16位数据时也是如此。因此,数据需要从附加的全局存储器中分批复制到本地FPGA存储器中,一旦并行卷积的数量增加到超过全局存储器所能支持的程度,这最终会支配性能。

表2提供了最终编译的设计的一些统计数据。请注意,Logic还包括通过PCIe和全局内存接口进行主机通信所需的板卡支持包资源。

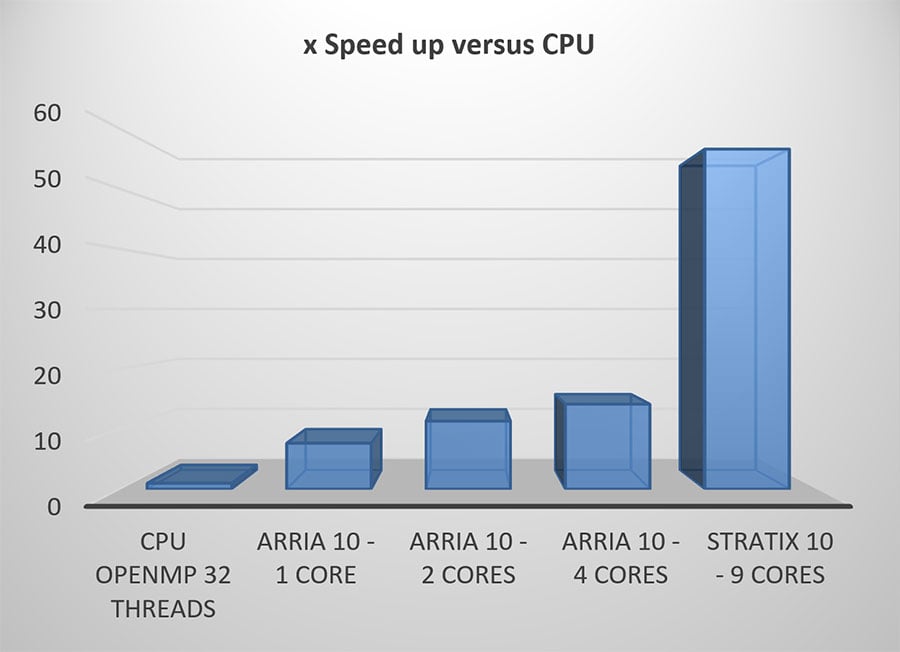

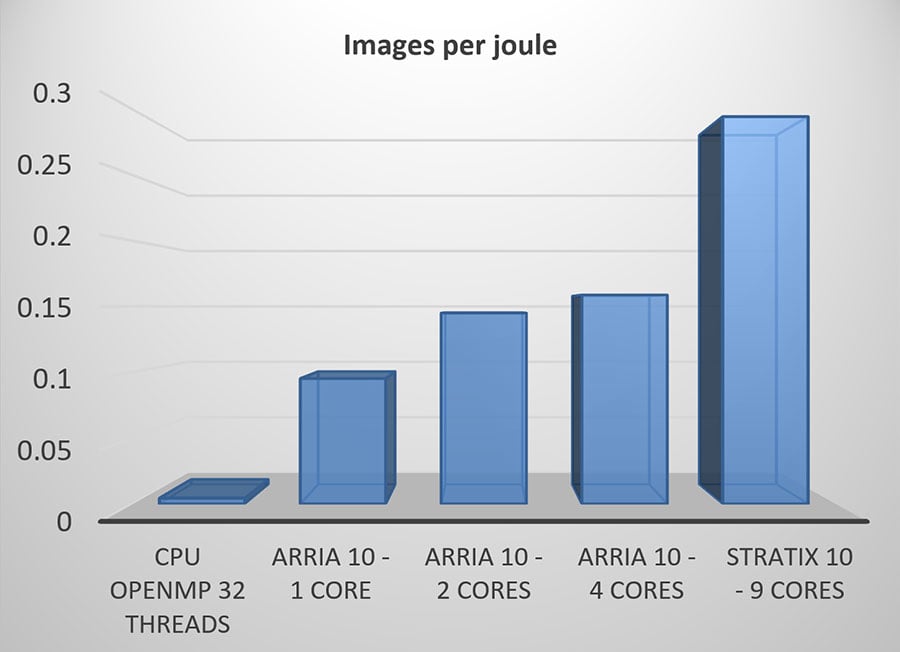

接下来的数字提供了与Arria 10和Xeon CPU相比,在速度和单位能耗方面的性能比较。请注意,对于Stratix 10,甚至可以利用更多的内核来进一步提高速度。

Stratix 10 MX上的HBM2

新的BittWare 520N-MX板采用了Intel Stratix 10 MX器件。该FPGA具有3D堆叠的高带宽存储器2(HBM2),有32个用户端口,提供高达512 GB/s的综合存储器带宽。这种额外的带宽允许采用不同的架构,可以帮助减少设计中的高扇出量,并减少对外部存储器的内部缓冲的需要。MX器件应通过简化内存仲裁网络释放更多的用户逻辑用于处理,该网络对于内存密集型算法来说可能变得复杂,并允许为CNN提供以前不可能提供的新的带宽有限的解决方案。

总结

FPGA的灵活性为每个单独的网络提供了CNN优化的机会,这在其他技术上很难实现,甚至不可能实现。随着工业界开始认识到神经网络的好处和推理应用的数量增加,对为不同的数据集、准确性和功率而定制的网络的要求也将增加。

充分实现未来广泛的应用将不可避免地需要通用API无法完全满足的拓扑结构,特别是在边缘计算方面。BittWare的各种FPGA解决方案,结合CNN FPGA的优化技术,在帮助业界实现FPGA在CNN上的潜力方面具有独特的优势。