白皮书

合成流量发生器参考设计

概述

支持的硬件

我们首次发布的合成流量发生器仅针对BittWare 的 XUP-P3R和250-SoC卡的100 GbE。 我们在为 Achronix、AMD 和英特尔推出的多速率以太网硬块做准备的同时,创建了这一版本。

合成流量发生器是数据采集参考设计的一部分

我们正在发布合成流量发生器,作为我们数据采集架构概念的一部分,从数据采集2.0版开始。流量发生器拥有QSFP的发送端,而数据采集拥有同一QSFP的接收端。这使我们能够将CMAC放入本地环回模式(或安装环回电缆),以使用流量发生器来测试数据采集。它还允许我们使用普通的DAC或光缆来发送流量到其他设备。

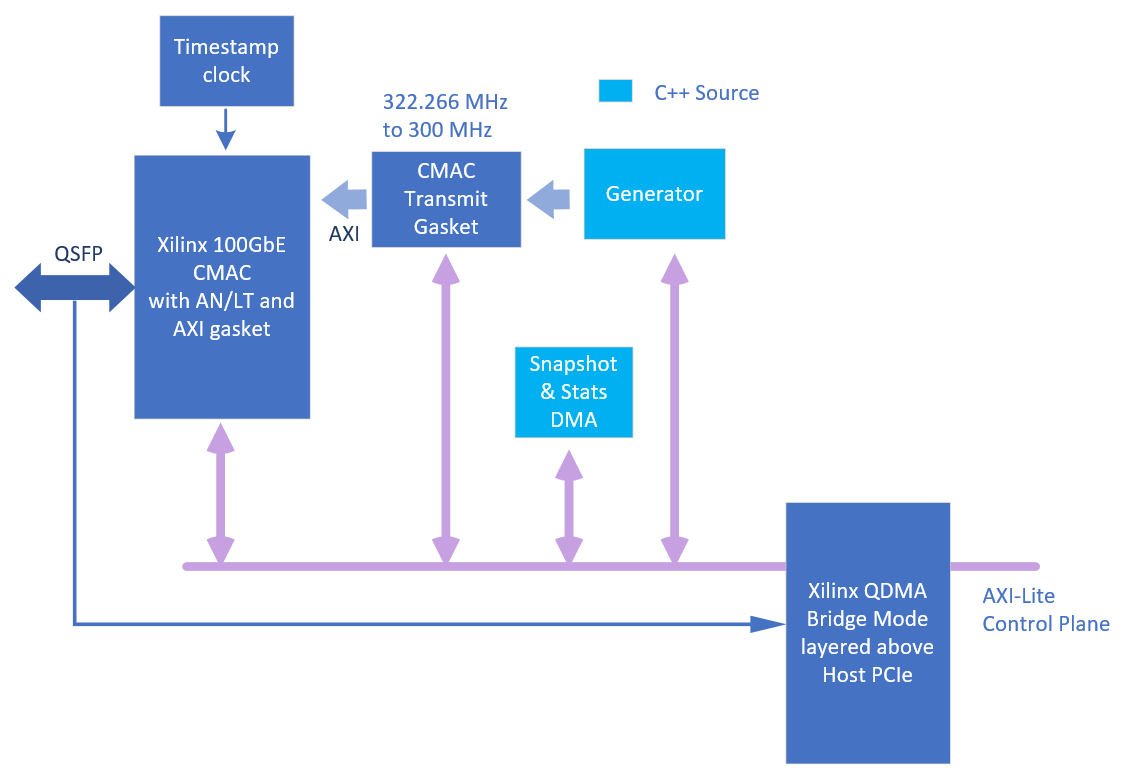

FPGA位流包含这里的管道图示

功能性

BittWare的合成流量发生器在FPGA内创建以太网数据包,并将它们发射到连接的网络中。

如果需要,用户可以部署BittWare单独的PCIe数据采集参考设计来接收这些数据包。当然,这是以软件配置流量发生器以生成IP数据包为前提的。

其基本思想是以线速度创建各种大小的数据包,持续时间长。数据包头不会改变。你可以在有效载荷内配置一个增加的数据包序号。

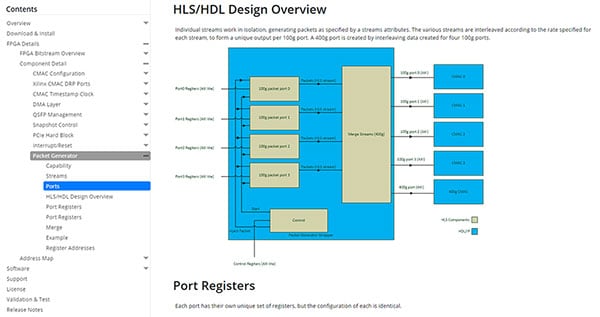

你最多可以交织32个这样的 "数据包流",这意味着你最多可以有32个不同的数据包头。我们需要这个功能来测试那些将收到的数据包流分成多个 "队列",以便使用多个主机CPU核心进行处理的目标。

你可以配置随机大小的数据包,但在BittWare,我们倾向于以线速度扫描设计,从一系列无休止的小数据包开始,以验证没有掉线,然后在有效载荷上增加一个字节,并继续测试,直到达到目标设计允许的最大有效载荷。

我们还允许用户在一个正在进行的数据流中插入他们想要的任何数据包的单一实例。这对于插入一个错误,看看会发生什么很有用。

数据包流不需要以线速发射,因为我们可以定义一个较长的包间间隔,从而降低数据包速率。最后,有效载荷数据可以是零、随机数、一个重复的64字节模式或一个增加的序列(即0123456789101112...)。

硬件设施

本合成流量生成器是在BittWare XUP-P3R 卡上创建和测试的,该卡包含 AMD VU9P 芯片,速度等级为 2。流量发生器不使用任何外部存储器。正如我们将数据捕获和流量发生器组合移植到 250-SoC 所演示的那样,该设计可以移植到任何带有 AMD UltraScale+ 芯片(包含 CMAC)的 BittWare 卡中。

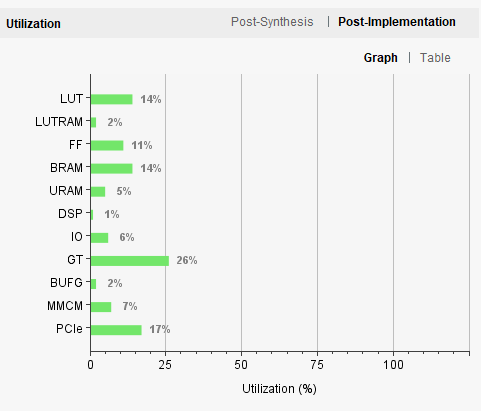

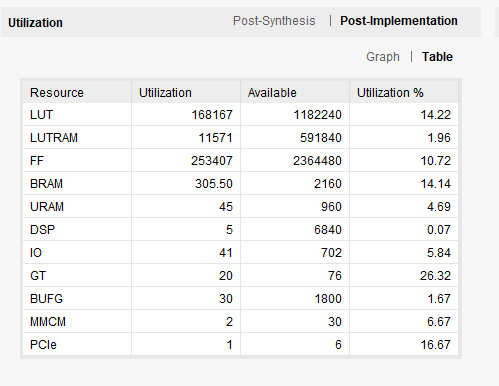

资源利用

这些图显示了数据采集参考设计的候选2.0.0版本(2021年2月)的FPGA资源利用率。这可能与我们最终发布的版本非常接近,甚至完全相同。

注意这个比特文件包括参考设计流量发生器和数据采集。

相关项目/解决方案

合成流量生成器结合了BittWare的较简单的环回实例所展示的相同的DAC电缆功能。

另一个相关的项目,StreamSurge,并不产生流量。相反,它从一个本地内存缓冲区中发送数据包。这些数据包来自于主机,使StreamSurge成为一个更加通用的工具。StreamSurge有两个值得注意的限制。首先,其基于内存的设计需要400GbE的专门硬件。具体来说,它需要一块同时具备400GbE和HBM的卡。其次,构建StreamSurge源需要授权第三方DPDK IP块。

对于全功能的流量生成器,我们希望转向Siama PROVA-C设备,因为它们非常有价值,并使用100GbE的BittWare硬件。

结论和要求应用说明

BittWare的数据捕获参考设计包括使用这个合成流量发生器,目前是100Gb/s。我们想分享它的功能,包括能够生成专有的传感器流量。

要了解更多信息,我们鼓励你使用下面的表格索取App Note,也就是流量生成器的文档。

还有更多内容要读:获取合成流量生成器应用说明

要求下载PDF文件

你在这个页面上看到的是BittWare的合成流量生成器的介绍。在完整的应用说明中还有很多细节!请填写表格,要求获得PDF版本的完整应用说明。

"*"表示必填项目