架构

低延迟开发框架

The Exegy (Enyx) Development Framework (nxFramework) is a hardware and software development environment designed to efficiently build and maintain ultra-low latency FPGA applications for the financial industry. Based on 10 years of research and development, nxFramework is the foundation for all Enyx off-the-shelf solutions and provides clients with the toolchain to manage a large portfolio of applications.

nxFramework是为构建内部高性能交易引擎、订单执行系统、交易前风险检查网关和定制项目而开发的--任何熟练的FPGA开发人员在开始一个新的低延迟项目、维护一个现有项目或寻求改变平台时,都可以利用nxFramework立即缩短生产时间。

10G MAC/PCS @

29ns RTT

10G TCP @

53ns RTT

60+ 实用程序库

内核

特点

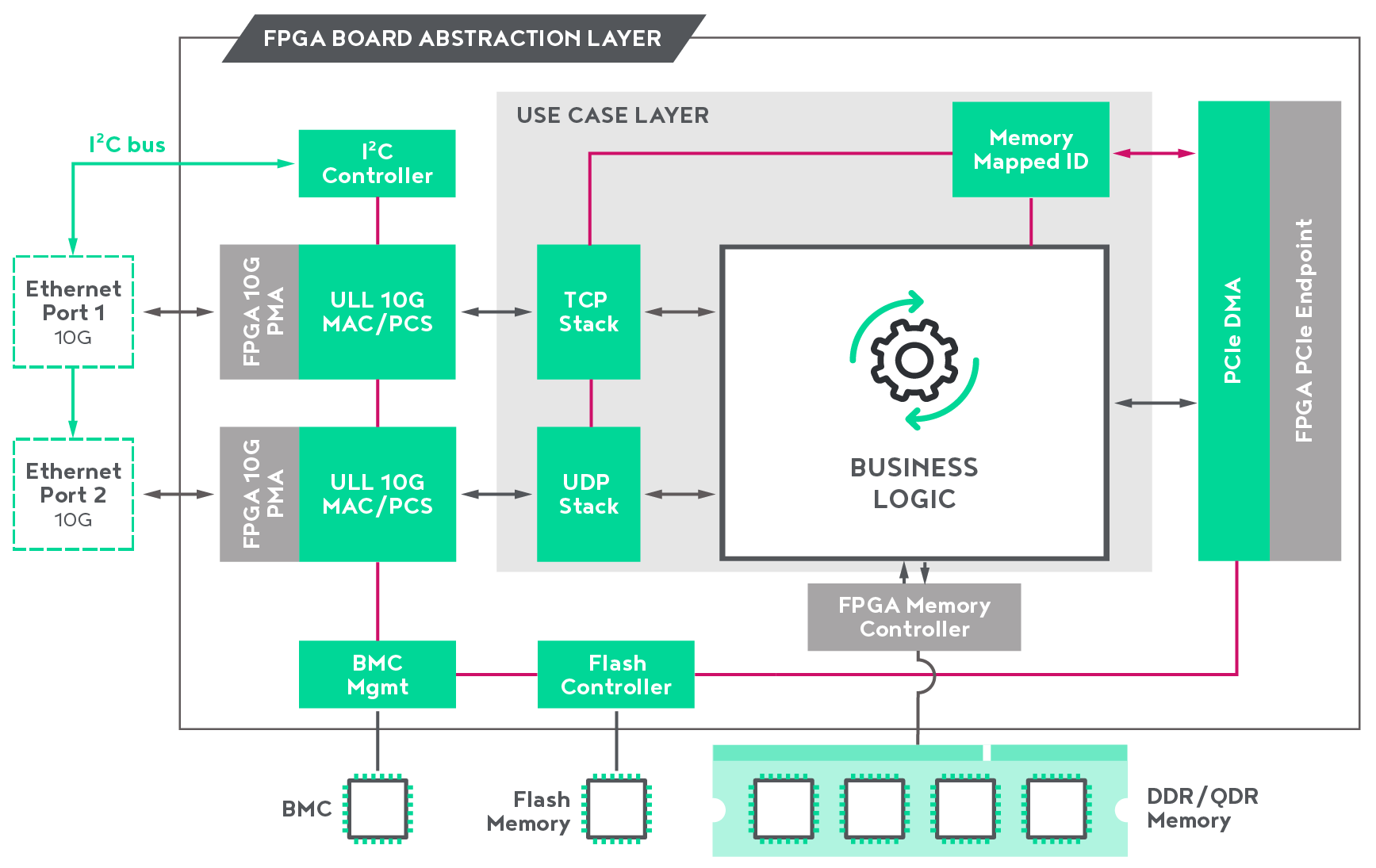

超低延迟的连接核心

- 10G MAC/PCS - 29ns RTT - SOP to SOF @ 322MHz

- 40G MAC/PCS - 55ns RTT - SOP to SOF @ 322MHz

- 10G TCP堆栈 - 53ns RTT @ 322MHz

- 10G UDP堆栈 - 43ns RTT @ 322MHz

- PCIe流媒体DMA - 790ns RTT @ 250MHz

60多个实用核心的资料库

- MMIO核心库

- 分组流核心库

- 内存管理核心库

- 数学核心库

- 统计学核心库

- 仿真帮助器库

nxFramework Overview

NVMe桥接平台IP核心事实

提供与核心

- 文档:全面的用户文档

- 设计文件格式: 加密的Verilog

- 约束文件:每个FPGA提供的

- 验证:ModelSim验证模型

- 实例化模板:Verilog (可使用VHDL包装器)

- 参考设计和应用说明: 合成以及放置和路由脚本

- 附加项目:参考设计

使用的仿真工具:

QuestaSim (联系IntelliProp以了解支持的最新版本)

支持:

从交付日期起的6个月内,将为完全授权的内核提供电话和电子邮件支持。

注:

其他模拟器也可提供。请联系IntelliProp公司了解更多信息。

方框图、数据表和产品细节

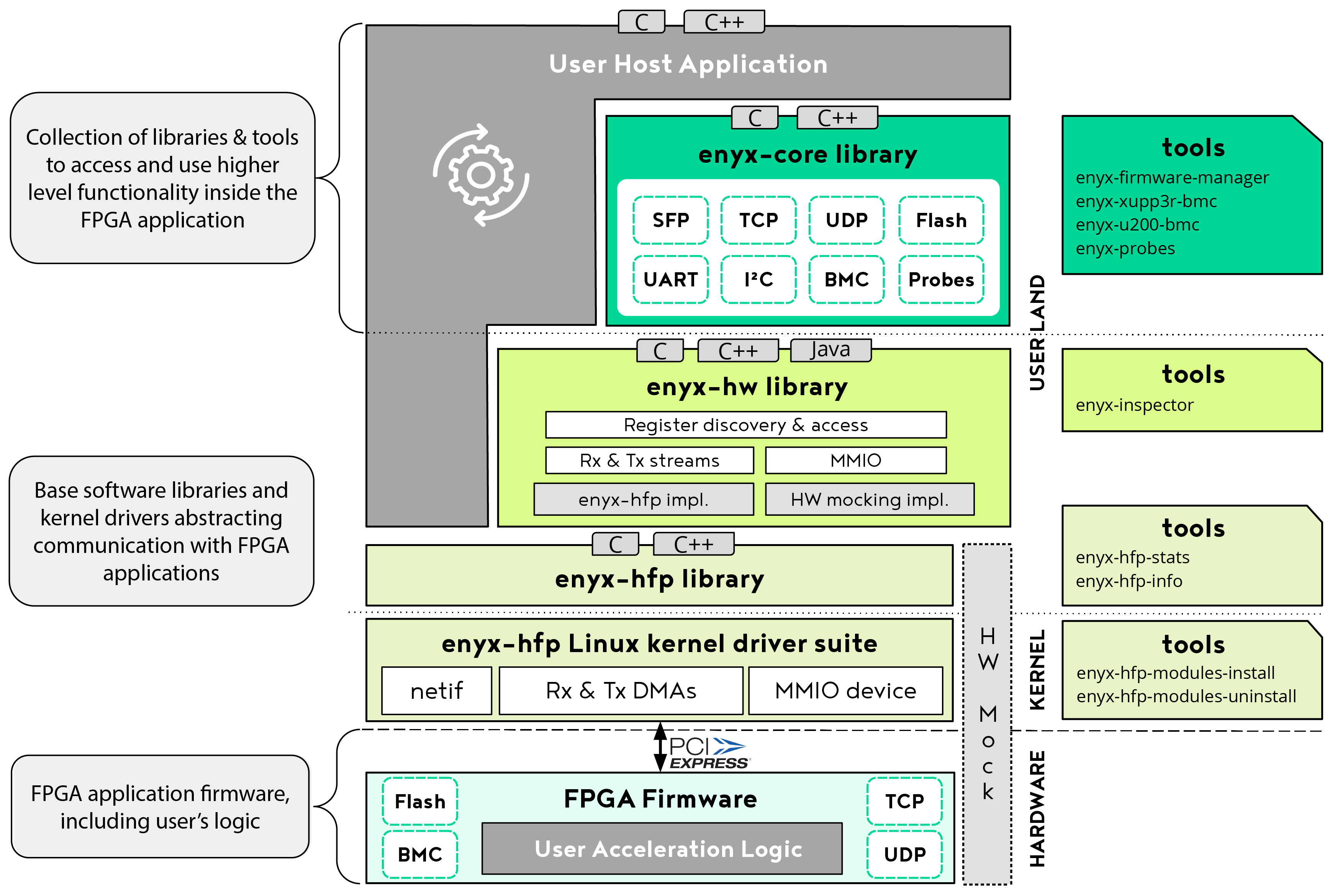

Enyx运行时软件栈

Enyx运行时软件栈

能够简单地配置和监测Enyx连接性和实用核心,包括通过我们的C/C++库与FPGA应用互动。

空标题

空空如也

硬件开发环境

一个Python脚本开发环境,使用户能够简化他们的开发周期,加速他们的生产时间。

空标题

空头

Enyx检查器:高效的调试

配备了一个基于网络的GUI,可以在运行时配置和监控FPGA,允许快速部署和调试。

空标题

空头

详细功能列表

- 所有可用的Enyx连接性和实用性核心

- 董事会管理核心:

- 闪存控制器对FPGA位流的支持

- 用于SFP/QSFP通信的I²C总线控制器

- 可配置的内存控制器实例化(DDR4、QDR II+)。

- 其他内容包括:

- Enyx检查器:一个基于网络的调试工具

- Linux驱动和配置/通信库

- 现成的、可配置的参考设计

- 支持在金融领域广泛使用的FPGA系列

参考实例/使用案例

ULL Tick-to-trade平台

- 用于ULL tick-to-trade FPGA交易策略的标准参考设计

- nxFramework提供了所有必要的硬件和软件模块来协助开发。

- 低于100纳秒的RTT延时

交易前的风险检查 途径

- 风险检查网关加速的标准参考设计

- 两个不同的TCP堆栈分别连接到用户和交易所

- 低于1µs的RTT延时

兼容的FPGA卡

对价格或更多信息感兴趣?

我们的技术销售团队随时准备提供可用性和配置信息,或回答您的技术问题。

"*"表示必填项目