刚玉

开源的100G网卡IP核

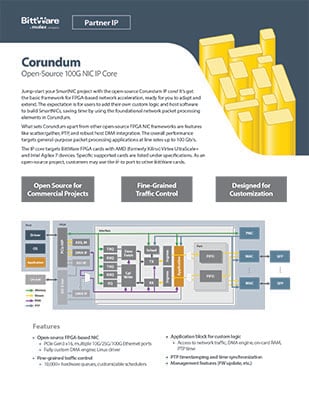

用开源的Corundum IP核来启动你的SmartNIC项目吧!它有基于FPGA的网络加速的基本框架,你可以随时扩展!它为基于FPGA的网络加速提供了基本框架,您可以随时调整和扩展。我们希望用户能够添加自己的定制逻辑和主机软件来构建SmartNIC,通过使用Corundum中的基础网络包处理元素来节省时间。一个用户应用区允许更容易地针对多种卡类型。

Corundum与其他开源FPGA网卡框架不同的是,它具有散射/聚集、PTP和强大的主机DMA集成等功能。整体性能针对线速高达100Gb/s的通用数据包处理应用。

该 IP 核针对带有 AMD Virtex UltraScale+ 和 Altera Agilex 7 器件的 BittWare FPGA 卡。具体支持的板卡列在规格项下。作为一个开源项目,客户可以使用该 IP 移植到其他 BittWare 卡。

开放源代码用于 商业项目

细致的 交通控制

设计用于 定制化

产品介绍

特点

- 基于FPGA的开源网卡

- PCIe Gen3 x16,多个10G/25G/100G以太网端口

- 完全定制的DMA引擎;Linux驱动

- 细致的交通控制

- 10,000多个硬件队列,可定制的调度器

- 用于自定义逻辑的应用块

- 访问网络流量、DMA引擎、卡上RAM、PTP时间

- PTP时间标记和时间同步

- 管理功能(固件更新等)。

数据表和产品细节

应用

- 卸载特定应用的处理

- 新型发送调度器的数据路径

- 用于性能测量的仪器刚玉

- 直接访问收发器允许物理层测量和开发新的线路协议

- 在更大的系统中使用核心逻辑作为数据包DMA引擎

详细功能列表

细致的交通控制

- 10,000多个传输队列

- 每个队列是SW和HW之间的一个独立通道

- 在SW中分类,在HW中控制

- 细粒度的、按流量或按目的地的控制

- 128位/队列 -> US+上2个URAM中的4096个队列

- 发送调度器

- 决定从哪个队列传输

- 默认的调度程序是轮流进行

- 可用于实现流量整形、速率限制等。

开放源码

- 刚玉的核心逻辑是100%开源的Verilog

- 包括10G/25G MACs、PCIe DMA、AXI、AXI流等。

- 用于接口的设备硬IP - PCIe、100G MAC、serdes

- 仿真使用开放源码工具

- Cocotb + Icarus Verilog/Verilator

- 用于AXI、以太网和PCIe的Cocotb扩展

- Tox + pytest用于CI

- 用于构建自动化的Makefiles

端口和接口

- 对多条上行链路的硬件支持

- 多个物理端口作为单一的操作系统级接口出现

- 端口有独立的调度器

- 通过改变调度器设置来迁移或剥离各端口的流量

传统的网卡:软件中的分配

刚玉网卡:硬件上的分配

模块化的DMA引擎

- DMA引擎在接口和客户端模块之间分割

- 接口连接到主机 - PCIe、AXI等。

- 客户端模块形成内部端口 - AXI流,内存映射的AXI

- 连接到具有双端口RAM的接口的客户

- 用相同的核心逻辑支持服务器(PCIe)和SoC(AXI)。

刚玉

关于该项目

Corundum是一个开源的基于FPGA的网卡和网络内计算平台。

对价格或更多信息感兴趣?

我们的技术销售团队随时准备提供可用性和配置信息,或回答您的技术问题。

"*"表示必填项目