PCIe FPGA Card

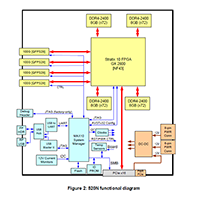

520N

Stratix 10 FPGA PCIe Board

4x QSFPs and 32 GBytes DDR4

Obsolete Product Notice:

This is an obsolete product and is no longer available for purchase. Contact BittWare for a recommended newer product.

Overview

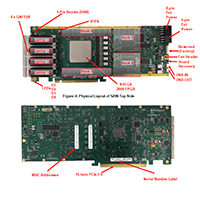

Introducing ground-breaking single precision floating point performance of up to 10 TFLOPS, the 520N is a PCIe board featuring an Intel Stratix 10 FPGA, along with four banks of DDR4 external memory.

Four network ports enable dramatic FPGA-to-FPGA scaling independent of the PCIe bus, plus support for an array of serial I/O protocols operating up at 10/25/40/100GbE.

Both traditional HDL and higher abstraction C, C++ and OpenCL-based tool flows are supported. Deliverables include an optimized board support package (BSP) for the Intel OpenCL SDK.

Key Features

4x QSFP28s for 400Gbps

OpenCL BSP

Intel Stratix 10 GX 2800

Get to Market Faster With IP & Solutions from BittWare Partners

Block Diagram, Data Sheet and Specifications

Want More Details?

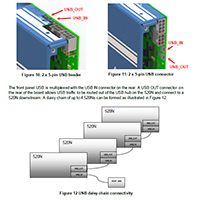

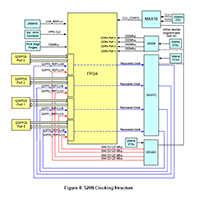

Request the Hardware Reference Guide (HRG)

The HRG gives you much more detail about the card such as block diagrams, tables and descriptions.

Specifications

FPGA

- Intel Stratix 10 GX

- GX2800 in an F1760 package

- L-tile with up to 26Gbps SerDes I/O

- H-tile with up to 28Gbps SerDes I/O

- Core speed grade -2: I/O speed grade -2

- Contact BittWare for other Stratix 10 GX options

On-board Flash

- 2Gbit Flash memory for booting FPGA

External memory

- Four banks of DDR4 SDRAM x 72 bits

- 8GB per bank (32GB total / 64GB version also available)

- Transfer Rate: 2400 MT/s

Host interface

- x16 Gen3 interface direct to FPGA, connected to PCIe hard IP

QSFP cages

- 4 QSFP28 cages on front panel connected directly to FPGA via 16 transceivers

- L-Tile: up to 2 100Gbps network ports

- H-Tile: up to 4 100Gbps network ports

- User programmable low jitter clocking supporting 10/25/40/100GbE

- Each QSFP28 can be independently clocked

- Jitter cleaner for network recovered clocking

- 2 QSFP28s have available 100GbE MAC hard IP

System manager

- On-board Intel USB Blaster

- Power and temperature monitoring

- Fault condition reporting to FPGA

Cooling

- Standard: double-width active heatsink (with fan)

- Optional: double-width passive heatsink

Electrical

- On-board power derived from 12V PCIe slot & two AUX connectors (one 8-pin, one 6-pin)

- Power dissipation is application dependent

- Typical max power consumption 225W

Environmental

- Operating temperature: 5°C to 35°C

Quality

- Manufactured to IPC-A-610-Class 2

- RoHS compliant

- CE, FCC & ICES approvals

Form factor

- Standard-height PCIe dual-slot board

- 4.376 x 10.5 inches (111 x 266.7 mm)

Development Tools

- FPGA development BIST - Built-In Self-Test for CentOS 7 provided with source code (pinout, gateware, PCIe driver & host test application)

- Application development Supported design flows - Intel FPGA OpenCL SDK, Intel High-Level Synthesis (C/C++) & Quartus Prime Pro (HDL, Verilog, VHDL, etc.)

Deliverables

- 520N FPGA board

- USB cable (front panel access)

- Built-In Self-Test (BIST)

- OpenCL HPC Board Support Package (BSP)

- 1-year access to online Developer Site

- 1-year hardware warranty

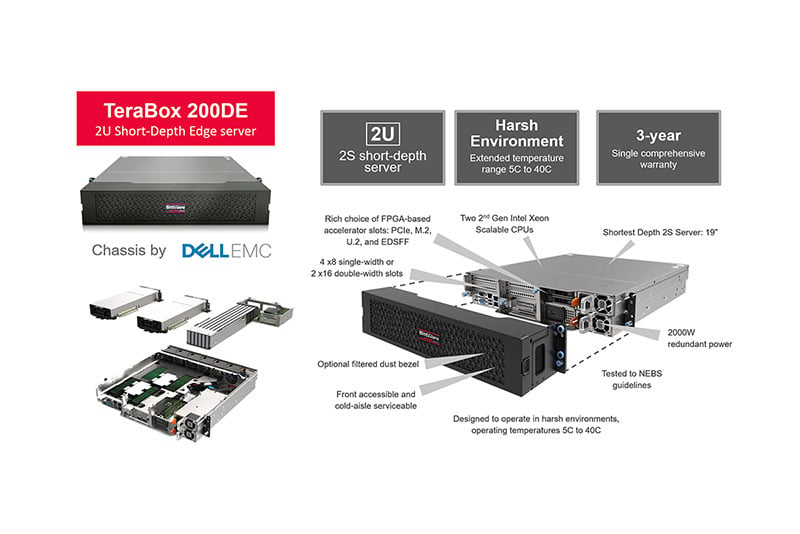

Order Your Cards in a TeraBox™ FPGA Server

Get extended warranty support and save time with a pre-integrated solution!

Ready to Buy?

This product is available for quick online ordering from Mouser Electronics. Check stock at Mouser’s website:

Interested in Pricing or More Information?

Our technical sales team is ready to provide availability and configuration information, or answer your technical questions.

"*" indicates required fields