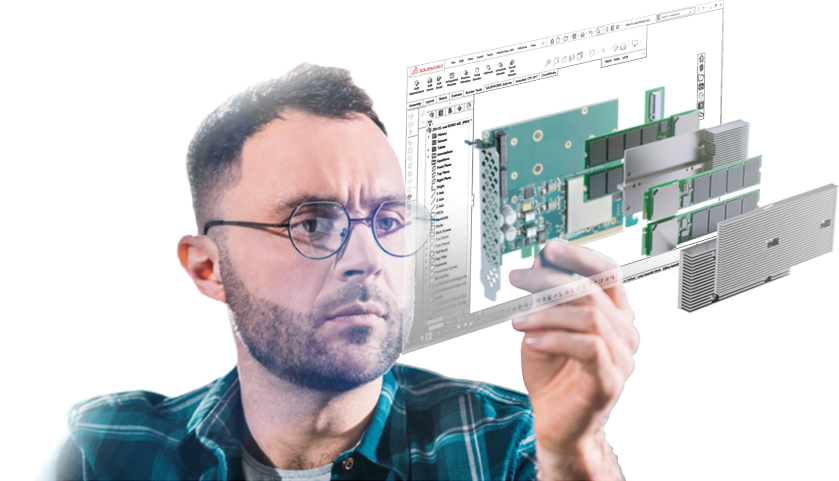

PCIe FPGA Card

520N-MX

Stratix 10 FPGA Board with 16GB HBM2

Powerful solution for accelerating memory-bound applications

Legacy Notice and Recommendation

This is a legacy product and is not recommended for new designs. It is still available for purchase, but development tools and software are no longer maintained for compatibility with the latest FPGA tools and operating systems. Minimum order quantities (MOQs) may apply.

Our recommended product for consideration is the IA-860m.

Need a Price Quote?

Overview

Designed for compute acceleration, the 520N-MX is a PCIe board featuring Intel’s Stratix 10 MX2100 FPGA with integrated HBM2 memory. The size and speed of HBM2 (16GB at up to 512GB/s) enables acceleration of memory-bound applications. The board’s 100G QSFP28s are ideal for clustering, and OCuLink connectors allow expansion.

Key Features

Intel Stratix 10 MX2100

16GB HBM2 up to 512 GB/s

OpenCL BSP

Need a Customized Variant?

I/O interfaces on this card not exactly what you're looking for? Talk to us about your exact needs as we can quickly build additional variants.

Get to Market Faster With IP & Solutions from BittWare Partners

Block Diagram, Data Sheet and Specifications

Want More Details?

Request the Hardware Reference Guide (HRG)

The HRG gives you much more detail about the card such as block diagrams, tables and descriptions.

Specifications

FPGA

- Intel Stratix 10 MX

- MX2100 in an F2597 package

- 16GBytes on-chip High Bandwidth Memory (HBM2) DRAM, 410 GB/s (speed grade 2)

- Core speed grade -2: I/O speed grade -2

- Contact BittWare for other Stratix 10 MX options

On-board Flash

- 2Gbit Flash memory for booting FPGA

External memory

- 2x 288-pin DIMM slots each fitted with 16GB modules by default, i.e., 32GB total on board (options up to 256GB total)

Host interface

- x16 Gen3 interface direct to FPGA, connected to PCIe hard IP

QSFP cages

- 4 QSFP28 cages on front panel connected directly to FPGA via 16 transceivers

- User programmable low jitter clocking supporting 10/25/40/100GbE

- Each QSFP28 can be independently clocked

- Jitter cleaner for network recovered clocking

- 2 QSFP28s have available 100GbE MAC hard IP

OCuLink

- 2x edge connectors (A, B) @ 12.5G per lane (default); each supports PCIe Gen 3 x8 hard IP, GPIO, and PCIe master and optional input clocking

- 2x inner connectors (C, D) @ 25G per lane (optional); 1x 100GbE MAC hard IP per OCuLink

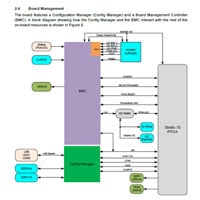

Board Management Controller

- Voltage, current, temperature monitoring

- Power sequencing and reset

- Field upgrades

- FPGA configuration and control

- Clock configuration

- Low bandwidth BMC-FPGA comms with SPI link

- USB 2.0

- PLDM support

- Voltage overrides

Cooling

- Standard: double-width active heatsink (with fan)

- Optional: double-width passive heatsink

- Optional: double-width liquid cooling

Electrical

- On-board power derived from 12V PCIe slot & two AUX connectors (one 8-pin, one 6-pin)

- Power dissipation is application dependent

- Typical max power consumption 225W

Environmental

- Operating temperature: 5°C to 35°C

Quality

- Manufactured to IPC-A-610-Class 2

- RoHS compliant

- CE, FCC, UKCA & ICES approvals

Form factor

- Standard-height PCIe dual-slot board

- 4.376 x 10.5 inches (111 x 266.7 mm)

Development Tools

- FPGA development BIST - Built-In Self-Test for CentOS 7 provided with source code (pinout, gateware, PCIe driver & host test application)

- Application development Supported design flows - Intel FPGA OpenCL SDK, Intel High-Level Synthesis (C/C++) & Quartus Prime Pro (HDL, Verilog, VHDL, etc.)

Deliverables

- 520N-MX FPGA board

- USB cable (front panel access)

- Built-In Self-Test (BIST)

- OpenCL HPC Board Support Package (BSP)

- 1-year access to online Developer Site

- 1-year hardware warranty

r3 v0

Order Your Cards in a TeraBox™ FPGA Server

Get extended warranty support and save time with a pre-integrated solution!

Ready to Buy?

Product availability for online ordering from Mouser Electronics:

Interested in Pricing or More Information?

Our technical sales team is ready to provide availability and configuration information, or answer your technical questions.

"*" indicates required fields