PCIe FPGA Card

S7t-VG6

VectorPath Accelerator Card

Achronix Speedster7t FPGA board with GDDR6 and QSFP-DD

Overview

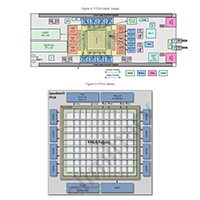

The S7t-VG6 VectorPath accelerator card offers a 7nm Achronix FPGA that is optimized for high-speed networking and fast, high-capacity memory access. Featuring a QSFP-DD (double-density) cage, the board supports up to 1x 400GbE or 4x 100GbE using the 56G PAM4-enabled Speedster®7t device. An additional QSFP port supports 2x 100GbE, and a 4x MCIO connector for expansion. Sixteen channels of GDDR6 graphics DRAM handle high-bandwidth memory requirements, providing up to 448GB/s.

The FPGA offers large logic and memory resources—up to 692K 6-input lookup tables (LUTs), and 189 Mb embedded RAM. It also provides 2,560 MLPs (machine-learning blocks).

Key Features

QSFPs for 1x 400G or 6x 100G

16GB GDDR6 up to 448GB/s

7nm FPGA with 56Gbps SERDES

Video

Craig Petrie gives a detailed explanation of the card's key features.

Generation 5.0

Double the Bandwidth!

The S7t-VG6 is ready for Gen5 for twice the bandwidth per lane of Gen4.

Block Diagram, Data Sheet and Specifications

Want More Details?

Request the Hardware Reference Guide (HRG)

The HRG gives you much more detail about the card such as block diagrams, tables and descriptions.

Specifications

FPGA

- Achronix Speedster AC7t1500

- 52.5 x52.5 package

- 692K 6-input lookup tables (LUTs)

- 189 Mb embedded RAM

- 2,560 MLPs

On-board Memory

- 16 GBytes GDDR6: 8 banks (2 independent 16-bit, 14 Gbps channels per bank), 3.5 Tbps aggregate bandwidth

- One bank DDR4-2666 with ECC, up to 4 GBytes (x72)

- Flash memory for booting FPGA

Host interface

- PCI-SIG certified to support PCIe Gen5 x16 host interface

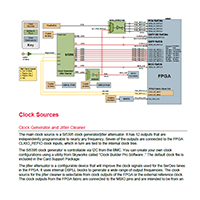

External clocking

- 1 PPS and 10MHz ref clk front panel inputs

USB

- USB port for access to BMC, USB-JTAG, USB-UART

- Second USB port for daisy chain

MCIO

- MCIO connected to FPGA via 4x transceivers

- PCIe Gen5 Hard IP

GPIO

- 8 GPIO pins, 3.3V, single ended, direction (Tx, Rx) independently settable by FPGA per GPIO, buffers rated to 200Mbps

QSFP cages

- QSFP-DD cage on front panel

- 56G PAM4 transceivers

- 400/200/100/50/25/10GbE

- Hard MAC and FEC for every speed

- QSFP56 cage on front panel

- 56G PAM4 transceivers

- 200/100/50/25/10GbE

- Hard MAC and FEC for every speed

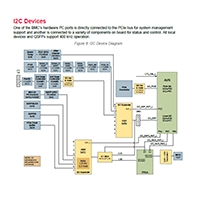

Board management controller

- Voltage, current, temperature monitoring

- Power sequencing and reset

- Field upgrades

- FPGA configuration and control

- Clock configuration

- I2C bus access

- USB 2.0

- Voltage overrides

Cooling

- Standard: dual-width passive heatsink

- Optional: dual-width active heatsink

- Optional: dual-width liquid cooling

Electrical

- On-board power from two AUX connectors (8 pin)

- Power dissipation is application dependent

- Typical max power consumption 225W

Environmental

- Operating temperature 5°C to 35°C

- Airfow requirements: 800 LFM

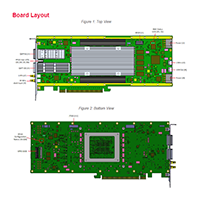

Form factor

- Standard-height PCIe dual-width board

- Size: 111.15mm x 266.70mm (4.376in x 10.500in)

Development Tools

System development

- Software development toolkit including PCIe driver, libraries and board monitoring utilities

FPGA development

- Achronix tools—ACE Design Tools

- FPGA example projects

r4 v2

Interested in Pricing or More Information?

Our technical sales team is ready to provide availability and configuration information, or answer your technical questions.

"*" indicates required fields