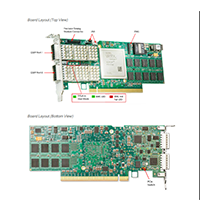

PCIe FPGA Card

XUP-PL4

UltraScale+ FPGA Low-Profile PCIe Card

Dual QSFP28s and DDR4

Need a Price Quote?

Legacy Product Notice:

This is a legacy product and is not recommended for new designs. It is still available for purchase, but development tools and software are no longer maintained for compatibility with the latest FPGA tools and operating systems. Minimum order quantities (MOQs) may apply. Contact BittWare for details.

Overview

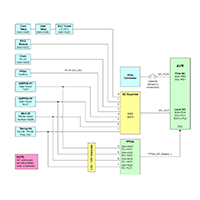

BittWare’s XUP-PL4 is a low-profile PCIe x16 card based on the AMD Virtex UltraScale+ FPGA. The UltraScale+ devices deliver high-performance, high-bandwidth, and reduced latency for systems demanding massive data flow and packet processing. The board offers up to 32 GBytes of memory, sophisticated clocking and timing options, and two front panel QSFP cages, each supporting up to 100 Gbps (4×25) – including 100GbE.

The XUP-PL4 also incorporates a Board Management Controller (BMC) for advanced system monitoring, which greatly simplifies platform integration and management. All of these features combine to make the XUP-PL4 ideal for a wide range of data center applications, including network processing and security, acceleration, storage, broadcast, and SigInt.

Key Features

2x 100GbE via 2 QSFP28

Up to 32 GBytes DDR4

Precision clocking and timing options

Precision Clocking and Timing

The XUP-PL4 is available with an optional add-on module that provides precision timestamping capabilities. Contact your BittWare Sales representative to learn more.

Block Diagram, Data Sheet and Specifications

Want More Details?

Request the Hardware Reference Guide (HRG)

The HRG gives you much more detail about the card such as block diagrams, tables and descriptions.

Specifications

FPGA

- Virtex UltraScale+

- VU3P in C1517 package

- Core speed grade - 2

- Contact BittWare for VU3P FPGA options

On-board memory

- Flash memory for booting FPGA

- Two banks of up to 16 GB DDR4 (x72)

Host interface

- x16 Gen3 interface direct to FPGA

Utility header

- Micro USB for BMC access and programming Flash

Timestamping (optional)

- 1 PPS input/output

- Reference clock input/output

QSFP cages

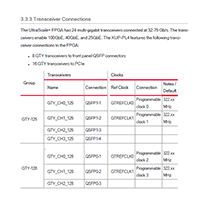

- 2 QSFP28 (zQSFP) cages on front panel connected directly to FPGA via 8 transceivers

- Each supports 100GbE, 40GbE, 4x 25GbE, or 4x 10GbE and can be combined for 400GbE

Board Management Controller

- Voltage, current, temperature monitoring

- Power sequencing and reset

- Field upgrades

- FPGA configuration and control

- Clock configuration

- I2C bus access

- USB 2.0

- Voltage overrides

Cooling

- Standard: single-width active heatsink

Electrical

- On-board power derived from 12V PCIe slot

- Power dissipation is application dependent

Environmental

- Operating temperature 5°C to 35°C

Form factor

- Low profile (half-height, half-length) PCIe slot board

- 6.6 x 3.85 inches

Development Tools

System development

- BittWorks II Toolkit - host, command, and debug tools for BittWare hardware

FPGA development

- FPGA Examples - example Vivado projects

- AMD Tools - Vivado® Design Suite

Order Your Cards in a TeraBox™ FPGA Server

Get extended warranty support and save time with a pre-integrated solution!

Ready to Buy?

This product is available for quick online ordering from Mouser Electronics. Check stock at Mouser’s website:

Interested in Pricing or More Information?

Our technical sales team is ready to provide availability and configuration information, or answer your technical questions.

"*" indicates required fields