AV-870p

高速I/OとPCIe Gen5

パートナーシップ

AMDの次世代プログラマブル・ハードウエア

AMD Versal Adaptive SoCは、最も困難なコンピュートおよびネットワーキング・アプリケーション向けに、ネットワーク化され、消費電力が最適化されたコアを適応可能なプラットフォーム上に統合しています。

- 7nmアーキテクチャ:Versal Premiumアーキテクチャは、高い帯域幅と計算密度を、適応性の高いプラットフォームで組み合わせたものです。

- PCIe Gen5対応:Gen4より2倍速いデータ転送速度、CPUとワークロードアクセラレータ間の高速インターフェイス。

7nm アーキテクチャ

最新世代の7nmアーキテクチャは、適応性の高いコンピュート・エンジンと、広範なハード化されたメモリおよびインターフェイス技術を組み合わせ、競合する10nm FPGAよりも優れた性能/ワット数を実現しています。

PCIe Gen5対応

PCIe Gen5は、PCIe Gen4の2倍のデータ転送速度をサポートし、PCインターコネクト、グラフィックアダプタ、チップレベル通信の開発者に、より高いパフォーマンス能力を提供します。

価格見積もりは必要ですか?

Ethernet Hard IP Conceptual Guide

Diagrams below show the basics of Hard IP blocks available for Ethernet. These diagrams are intended only to give a high-level understanding of possible configurations of network ports.

Contact us for specific capability questions at BittWare.com/contact.

Transceiver lane speed options for Ethernet

GTM

Each GTM: 4x lanes at 10G NRZ, 25G NRZ or PAM4, or 50G PAM4 (other non-Ethernet rates available)

GTYP

Each GTYP: 4x lanes at 10G or 25G NRZ (other non-Ethernet rates available)

Typical features driving chip/mezzanine options

Your particular needs will drive which is the best combination of chip and mezzanine:

Versal VP1402 + Standard QSFP-DD Mezzanine

(more using select TeraBox chassis)

Versal VP1502 + Standard QSFP-DD Mezzanine

Balance of network ports and chip resources

Versal VP1552 + Standard QSFP-DD Mezzanine

Maximize GTYPs for low latency and sub-10G (non-Ethernet) rates

Port Locations Map

For this guide, each ARC6 and QSFP-DD port is numbered as shown. Always defer to the HRG for port addressing from a development standpoint.

Using the dual ARC6 interfaces

One way to utilize the ARC6 connectors is as part of select TeraBox systems with front-panel QSFP-DDs that internally route to the card’s transceivers throught the ARC6 interfaces.

Options for card and server configurations vary. We recommend contacting us for more details at BittWare.com/contact.

Options using Versal VP1402 and Standard QSFP-DD Mezzanine

Options using Versal VP1502 and Standard QSFP-DD Mezzanine

Options using Versal VP1552 and Standard QSFP-DD Mezzanine

Options using Versal VP1552 and GTYP QSFP-DD Mezzanine

Alternative to the default mezzanine provides all-GTYP transceiver connections. Advantages include lower latency than GTMs and lower minimum (non-Ethernet) data rates to 1.25 Gb/s.

Example uses for specific Ethernet rates

Below are examples of how specific desired Ethernet rates can be achieved. Many more configurations are possible based on chip features, mezzanine options, user routing logic, and transceiver configuation. Specific Ethernet modules/cables required will also vary based on configuration, and often require breakout cables.

Example 1

4x 400 GbE

This first example pairs the Versal 1402 with the standard QSFP-DD mezzanine for 4x 400 GbE ports in a dual-slot configuration.

Need more 400 GbE ports? Talk to us about utilizing the ARC6 interfaces plus an additional pair of GTMs within TeraBox server chassis options at BittWare.com/contact.

Example 2

2x 400 GbE + 8x 100 GbE

Maximizing 400G and 100G bandwidth using the standard QSFP-DD mezzanine and the VP1502 device.

Example 3

16x 100 GbE

This example is very similar to #2, except we’ve exchanged two 400 GbE links for eight 100 GbE for a total of 16x 100GbE on the VP1502.

Example 4

32x 10 GbE

This example uses the standard QSFP-DD mezzanine and the Versal VP1552 device.

Example 5

2x 400 GbE + 2x 100 GbE + 8x 25 GbE

This example uses the standard QSFP-DD mezzanine and the Versal VP1502 device.

BittWare パートナーからのIPとソリューションで、より早く市場に参入する。

AV-870pブロック図、データシート、仕様書

ボード仕様

適応型SoC

- バーサル・プレミアム

- VP1402/VP1502/ VP1552

- コアスピードのグレード - 2

- その他のFPGAオプションについては、BittWare までお問い合わせください。

オンボードフラッシュ

- FPGAブート用フラッシュメモリ

外部メモリ

- 2x 8GB LPDDR4チップ(合計16GB)@4266MHz(64ビット)、NOC経由でARMおよびFPGAロジックにアクセス可能

- 432MBの超低レイテンシGSI SRAM(オプション)

- 12x18ビットチップ

- 216ビットのバス幅

ホストインタフェース

- PCIe Gen5 x8x8 (bifurcated) or PCIe Gen4 x16 connected to PCIe w/DMA (CPM5) Hard IP (VP1502/VP1552)

- PCIe Gen5 x4x4 (bifurcated) or PCIe Gen4 x8 connected to PCI Express Hard IP (VP1402)

I/O拡張

- I/O expansion site connected to FPGA via 48x SerDes channels

- 2×ARC6-16コネクタ、各8×SerDesチャネル経由でFPGAに接続(合計16×SerDesチャネル)

QSFP-DDモジュール

- デフォルトのI/Oモジュールは、56G PAM4をサポートする4x QSFP-DDケージをフロントパネルに装備(32x SerDesを使用)

- カスタムモジュールの追加も可能。BittWare までご連絡ください。

クロッキング

- 2x ネットワーク・リカバリ・クロッキング用ジッター・クリーナー

- 2x 1PPS (インボード)

USB

- BMCへのUSBアクセス、USB-JTAG、USB-UART

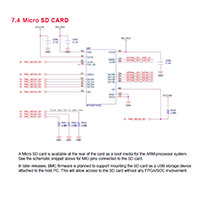

ボードマネジメントコントローラー

- オンボードCLI

- Python, C++ API (contact BittWare)

- FPGAファブリックとNOCに接続された200Mbpsパラレルポート

- ARMプロセッサーにOSイメージを簡単に転送できるUSB SDカードリーダー

- 高速FPGAブート・フラッシュ・プログラミング

- 温度、電圧、電流モニタリング

- 集中管理用SNMPエージェント

- あらかじめプログラムされた32個のMACアドレスの専用配列

- I/OポートのモニタリングCLIおよびAPIによるQSFP、SFP、QSFP-DDへのフルアクセスおよびプログラミング

- カスタムクロック設定に対応したCLIベースのクロック選択

クーリング

- 標準:デュアルワイド・パッシブヒートシンク

エレクトリカル

- オンボード電源は12V PCIeスロットと2x AUXコネクタから供給

- 消費電力はアプリケーションに依存します。

環境関連

- 動作温度5℃から35℃まで

フォームファクター

- 標準高さ、長さ3/4、デュアル幅PCIeカード

- 10×4.37インチ(254×111.15mm)

開発ツール

アプリケーション開発

- サポートされる設計フロー -Vivado Design Suite (HDL、Verilog、VHDL など)

r0 v17

購入の準備はできていますか?

Mouser Electronicsからのオンライン注文のための製品在庫状況:

価格や詳細についてご興味のある方は、こちらをご覧ください。

当社のテクニカルセールスチームは、在庫状況や構成情報を提供したり、技術的な質問に答えたりする準備ができています。

"*"は必須項目