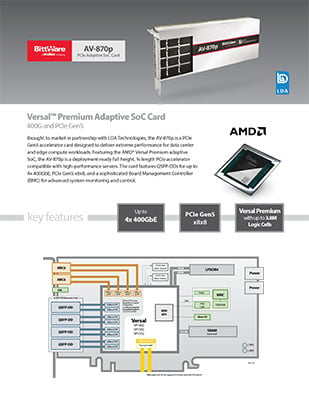

AV-870p

고속 I/O 및 PCIe Gen5

다음 파트너와 협력

AMD의 차세대 프로그래머블 하드웨어

AMD 버설 어댑티브 SoC는 가장 까다로운 컴퓨팅 및 네트워킹 애플리케이션을 위해 적응형 플랫폼에 네트워크로 연결된 전력 최적화 코어를 통합합니다.

- 7nm 아키텍처: Versal 프리미엄 아키텍처는 적응형 플랫폼에 높은 대역폭과 컴퓨팅 밀도를 결합합니다.

- PCIe Gen5 지원: Gen4보다 2배 빠른 데이터 전송 속도와 CPU와 워크로드 가속기 간의 고속 인터페이스.

7nm 아키텍처

최신 7nm 아키텍처는 적응형 컴퓨팅 엔진과 다양한 강화 메모리 및 인터페이스 기술을 결합하여 경쟁사 10nm FPGA보다 와트당 성능이 월등히 뛰어납니다.

PCIe Gen5 지원

PCIe Gen5는 PCIe Gen4보다 2배 빠른 데이터 전송 속도를 지원하여 PC 상호 연결, 그래픽 어댑터 및 칩 수준 통신 개발자에게 더 뛰어난 성능 기능을 제공합니다.

가격 견적이 필요하신가요?

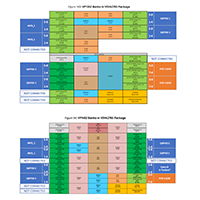

Ethernet Hard IP Conceptual Guide

Diagrams below show the basics of Hard IP blocks available for Ethernet. These diagrams are intended only to give a high-level understanding of possible configurations of network ports.

Contact us for specific capability questions at BittWare.com/contact.

Transceiver lane speed options for Ethernet

GTM

Each GTM: 4x lanes at 10G NRZ, 25G NRZ or PAM4, or 50G PAM4 (other non-Ethernet rates available)

GTYP

Each GTYP: 4x lanes at 10G or 25G NRZ (other non-Ethernet rates available)

Typical features driving chip/mezzanine options

Your particular needs will drive which is the best combination of chip and mezzanine:

Versal VP1402 + Standard QSFP-DD Mezzanine

(more using select TeraBox chassis)

Versal VP1502 + Standard QSFP-DD Mezzanine

Balance of network ports and chip resources

Versal VP1552 + Standard QSFP-DD Mezzanine

Maximize GTYPs for low latency and sub-10G (non-Ethernet) rates

Port Locations Map

For this guide, each ARC6 and QSFP-DD port is numbered as shown. Always defer to the HRG for port addressing from a development standpoint.

Using the dual ARC6 interfaces

One way to utilize the ARC6 connectors is as part of select TeraBox systems with front-panel QSFP-DDs that internally route to the card’s transceivers throught the ARC6 interfaces.

Options for card and server configurations vary. We recommend contacting us for more details at BittWare.com/contact.

Options using Versal VP1402 and Standard QSFP-DD Mezzanine

Options using Versal VP1502 and Standard QSFP-DD Mezzanine

Options using Versal VP1552 and Standard QSFP-DD Mezzanine

Options using Versal VP1552 and GTYP QSFP-DD Mezzanine

Alternative to the default mezzanine provides all-GTYP transceiver connections. Advantages include lower latency than GTMs and lower minimum (non-Ethernet) data rates to 1.25 Gb/s.

Example uses for specific Ethernet rates

Below are examples of how specific desired Ethernet rates can be achieved. Many more configurations are possible based on chip features, mezzanine options, user routing logic, and transceiver configuation. Specific Ethernet modules/cables required will also vary based on configuration, and often require breakout cables.

Example 1

4x 400 GbE

This first example pairs the Versal 1402 with the standard QSFP-DD mezzanine for 4x 400 GbE ports in a dual-slot configuration.

Need more 400 GbE ports? Talk to us about utilizing the ARC6 interfaces plus an additional pair of GTMs within TeraBox server chassis options at BittWare.com/contact.

Example 2

2x 400 GbE + 8x 100 GbE

Maximizing 400G and 100G bandwidth using the standard QSFP-DD mezzanine and the VP1502 device.

Example 3

16x 100 GbE

This example is very similar to #2, except we’ve exchanged two 400 GbE links for eight 100 GbE for a total of 16x 100GbE on the VP1502.

Example 4

32x 10 GbE

This example uses the standard QSFP-DD mezzanine and the Versal VP1552 device.

Example 5

2x 400 GbE + 2x 100 GbE + 8x 25 GbE

This example uses the standard QSFP-DD mezzanine and the Versal VP1502 device.

비트웨어 파트너의 IP 및 솔루션으로 더 빠르게 시장에 진출하세요.

AV-870p 블록 다이어그램, 데이터 시트 및 사양

보드 사양

적응형 SoC

- 버살 프리미엄

- VP1402/VP1502/ VP1552

- 코어 속도 등급 - 2

- 다른 FPGA 옵션에 대해서는 BittWare에 문의하세요.

온보드 플래시

- FPGA 부팅용 플래시 메모리

외장 메모리

- 4266MHz(64비트)에서 8GB LPDDR4 칩 2개(총 16GB), NOC를 통해 ARM 및 FPGA 로직에 액세스 가능

- 432MB의 초저지연 GSI SRAM(선택 사항)

- 12x 18비트 칩

- 216비트 총 버스 폭

호스트 인터페이스

- PCIe Gen5 x8x8 (bifurcated) or PCIe Gen4 x16 connected to PCIe w/DMA (CPM5) Hard IP (VP1502/VP1552)

- PCIe Gen5 x4x4 (bifurcated) or PCIe Gen4 x8 connected to PCI Express Hard IP (VP1402)

I/O 확장

- I/O expansion site connected to FPGA via 48x SerDes channels

- 각각 8개의 SerDes 채널을 통해 FPGA에 연결된 2개의 ARC6-16 커넥터(총 16개)

QSFP-DD 모듈

- 기본 I/O 모듈은 전면 패널에 56G PAM4를 지원하는 4개의 QSFP-DD 케이지를 갖추고 있습니다(32개의 SerDes 사용).

- 추가 사용자 지정 모듈을 사용할 수 있습니다. BittWare에 문의하세요.

클럭킹

- 네트워크 복구 클럭킹을 위한 지터 클리너 2개

- 1PPS 2개(온보드)

USB

- BMC, USB-JTAG, USB-UART에 대한 USB 액세스

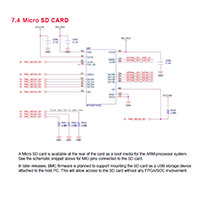

보드 관리 컨트롤러

- 온보드 CLI

- Python, C++ API (contact BittWare)

- FPGA 패브릭과 NOC에 연결된 200Mbps 병렬 포트

- ARM 프로세서로 간단한 OS 이미지 전송을 위한 USB SD 카드 리더기

- 빠른 FPGA 부팅 플래시 프로그래밍

- 온도, 전압, 전류 모니터링

- 중앙 집중식 관리를 위한 SNMP 에이전트

- 32개의 MAC 주소로 사전 프로그래밍된 전용 배열

- I/O 포트 모니터링. CLI 및 API를 통한 전체 QSFP, SFP, QSFP-DD 액세스 및 프로그래밍

- 사용자 지정 클록 구성을 지원하는 CLI 기반 클록 선택

냉각

- 표준: 이중 폭 패시브 방열판

전기

- 12V PCIe 슬롯과 2개의 AUX 커넥터에서 온보드 전원을 공급받습니다.

- 전력 손실은 애플리케이션에 따라 다릅니다.

환경

- 작동 온도: 5°C ~ 35°C

폼 팩터

- 표준 높이, 3/4 길이, 이중 폭 PCIe 카드

- 10 x 4.37인치(254 x 111.15mm)

개발 도구

애플리케이션 개발

- 지원되는 디자인 플로우 - 비바도 디자인 스위트(HDL, Verilog, VHDL 등)

r0 v17

구매할 준비가 되셨나요?

마우저 일렉트로닉스에서 온라인으로 주문할 수 있는 제품입니다:

가격이나 자세한 정보가 궁금하신가요?

기술 영업팀에서 가용성 및 구성 정보를 제공하거나 기술 관련 질문에 답변해 드립니다.

"*"는 필수 필드를 나타냅니다.