AV-870p

高速 I/O 和 PCIe Gen5

合作伙伴

AMD的下一代可编程硬件

AMD Versal Adaptive SoC 在一个可适应的平台上集成了网络化、功耗优化的内核,适用于最具挑战性的计算和网络应用。

- 7纳米架构:Versal Premium架构在一个可适应的平台上结合了高带宽和计算密度。

- 支持 PCIe Gen5:数据传输速度比 Gen4 快 2 倍,CPU 和工作负载加速器之间采用高速接口。

7纳米架构

最新一代的7纳米架构将适应性强的计算引擎与广泛的硬化存储器和接口技术结合起来,与竞争性的10纳米FPGA相比,性能/瓦特更出色。

支持PCIe Gen5

PCIe Gen5支持的数据传输速度比PCIe Gen4高2倍,为PC互连、图形适配器和芯片级通信的开发者提供了更大的性能能力。

需要报价吗?

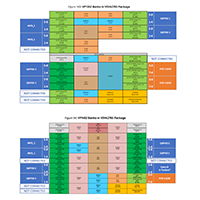

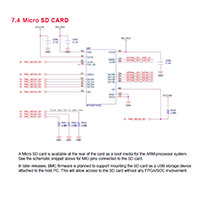

Ethernet Hard IP Conceptual Guide

Diagrams below show the basics of Hard IP blocks available for Ethernet. These diagrams are intended only to give a high-level understanding of possible configurations of network ports.

Contact us for specific capability questions at BittWare.com/contact.

Transceiver lane speed options for Ethernet

GTM

Each GTM: 4x lanes at 10G NRZ, 25G NRZ or PAM4, or 50G PAM4 (other non-Ethernet rates available)

GTYP

Each GTYP: 4x lanes at 10G or 25G NRZ (other non-Ethernet rates available)

Typical features driving chip/mezzanine options

Your particular needs will drive which is the best combination of chip and mezzanine:

Versal VP1402 + Standard QSFP-DD Mezzanine

(more using select TeraBox chassis)

Versal VP1502 + Standard QSFP-DD Mezzanine

Balance of network ports and chip resources

Versal VP1552 + Standard QSFP-DD Mezzanine

Maximize GTYPs for low latency and sub-10G (non-Ethernet) rates

Port Locations Map

For this guide, each ARC6 and QSFP-DD port is numbered as shown. Always defer to the HRG for port addressing from a development standpoint.

Using the dual ARC6 interfaces

One way to utilize the ARC6 connectors is as part of select TeraBox systems with front-panel QSFP-DDs that internally route to the card’s transceivers throught the ARC6 interfaces.

Options for card and server configurations vary. We recommend contacting us for more details at BittWare.com/contact.

Options using Versal VP1402 and Standard QSFP-DD Mezzanine

Options using Versal VP1502 and Standard QSFP-DD Mezzanine

Options using Versal VP1552 and Standard QSFP-DD Mezzanine

Options using Versal VP1552 and GTYP QSFP-DD Mezzanine

Alternative to the default mezzanine provides all-GTYP transceiver connections. Advantages include lower latency than GTMs and lower minimum (non-Ethernet) data rates to 1.25 Gb/s.

Example uses for specific Ethernet rates

Below are examples of how specific desired Ethernet rates can be achieved. Many more configurations are possible based on chip features, mezzanine options, user routing logic, and transceiver configuation. Specific Ethernet modules/cables required will also vary based on configuration, and often require breakout cables.

Example 1

4x 400 GbE

This first example pairs the Versal 1402 with the standard QSFP-DD mezzanine for 4x 400 GbE ports in a dual-slot configuration.

Need more 400 GbE ports? Talk to us about utilizing the ARC6 interfaces plus an additional pair of GTMs within TeraBox server chassis options at BittWare.com/contact.

Example 2

2x 400 GbE + 8x 100 GbE

Maximizing 400G and 100G bandwidth using the standard QSFP-DD mezzanine and the VP1502 device.

Example 3

16x 100 GbE

This example is very similar to #2, except we’ve exchanged two 400 GbE links for eight 100 GbE for a total of 16x 100GbE on the VP1502.

Example 4

32x 10 GbE

This example uses the standard QSFP-DD mezzanine and the Versal VP1552 device.

Example 5

2x 400 GbE + 2x 100 GbE + 8x 25 GbE

This example uses the standard QSFP-DD mezzanine and the Versal VP1502 device.

利用BittWare合作伙伴的IP和解决方案更快地进入市场

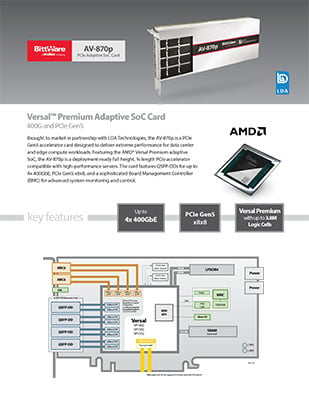

AV-870p 方框图、数据表和规格

董事会规格

自适应 SoC

- Versal Premium

- VP1402/VP1502/ VP1552

- 核心速度等级 - 2

- 联系BittWare以了解其他FPGA选项

车载闪光灯

- 用于启动FPGA的Flash存储器

外部存储器

- 通过 NOC 可访问 ARM 和 FPGA 逻辑的 2x 8GB LPDDR4 芯片(共 16GB),频率为 4266MHz(64 位

- 432 MB 超低延迟 GSI SRAM(可选)

- 12 个 18 位芯片

- 216 位总线宽度

主机接口

- PCIe Gen5 x8x8 (bifurcated) or PCIe Gen4 x16 connected to PCIe w/DMA (CPM5) Hard IP (VP1502/VP1552)

- PCIe Gen5 x4x4 (bifurcated) or PCIe Gen4 x8 connected to PCI Express Hard IP (VP1402)

输入/输出扩展

- I/O expansion site connected to FPGA via 48x SerDes channels

- 2 个 ARC6-16 连接器,通过每个 8 个 SerDes 通道(共 16 个)连接至 FPGA

QSFP-DD 模块

- 默认 I/O 模块前面板上有 4 个 QSFP-DD 固定架,支持 56G PAM4(使用 32 个 SerDes)

- 可提供其他定制模块。请联系 BittWare。

时钟

- 2 个抖动消除器,用于网络恢复时钟

- 2x 1PPS(板载)

USB

- USB访问BMC、USB-JTAG、USB-UART

董事会管理主计长

- 机载 CLI

- Python, C++ API (contact BittWare)

- 连接到 FPGA 结构和 NOC 的 200 Mbps 并行端口

- USB SD 读卡器可将操作系统图像轻松传输至 ARM 处理器

- 快速 FPGA 引导闪存编程

- 温度、电压、电流监控

- 用于集中管理的 SNMP 代理

- 由 32 个 MAC 地址组成的专用预编程阵列

- I/O 端口监控。通过 CLI 和 API 进行全面的 QSFP、SFP、QSFP-DD 访问和编程

- 基于 CLI 的时钟选择,支持自定义时钟配置

冷却

- 标准:双宽无源散热片

电气

- 板载电源来自 12V PCIe 插槽和 2 个 AUX 连接器

- 功率耗散取决于应用

环境

- 操作温度:5°C至35°C

形状系数

- 标准高度、3/4 长、双宽 PCIe 卡

- 10 x 4.37英寸(254 x 111.15毫米)。

开发工具

应用开发

- 支持的设计流程 -Vivado 设计套件(HDL、Verilog、VHDL 等)

r0 v17

准备购买吗?

可从 Mouser Electronics 在线订购的产品:

对价格或更多信息感兴趣?

我们的技术销售团队随时准备提供可用性和配置信息,或回答您的技术问题。

"*"表示必填项目