BittWare 파트너 IP

NVMe 브리지 플랫폼

NVMe 인터셉트 AXI-Stream 샌드박스 IP

컴퓨팅 스토리지 장치(CSD)는 스토리지 엔드포인트가 호스트 프로세싱을 오프로드하고 데이터 이동을 줄이기 위해 컴퓨팅 스토리지 기능(CSF)을 제공할 수 있도록 합니다. eBPF 처리, 암호화, 압축, 파일 시스템 관리, RAID와 같은 기능은 IntelliProp의 NVMe 브리지 플랫폼(NBP) IP 코어에 이상적으로 적합합니다.

인텔리프롭 IPC-NV171B-BR NVMe 브리지 플랫폼(NBP)은 인텔리프롭 NVMe 호스트 액셀러레이터 코어와 인텔리프롭 NVMe 타겟 코어를 활용해 NVMe 프로토콜 브리지를 생성합니다. 이 브리지는 명령 제출, 완료 알림 및 데이터 전송을 중단 없이 통과하거나 분석 또는 수정을 위해 가로채도록 설계되었습니다. 이 아키텍처는 AXI 스트림 프로토콜이 있는 "샌드박스" 영역에 인터페이스하여 IntelliProp 고객이 브리지에서 자체 맞춤형 RTL 및/또는 펌웨어를 구현할 수 있도록 합니다.

주요 기능

AXI-Stream 인터페이스를 갖춘 맞춤형 샌드박스

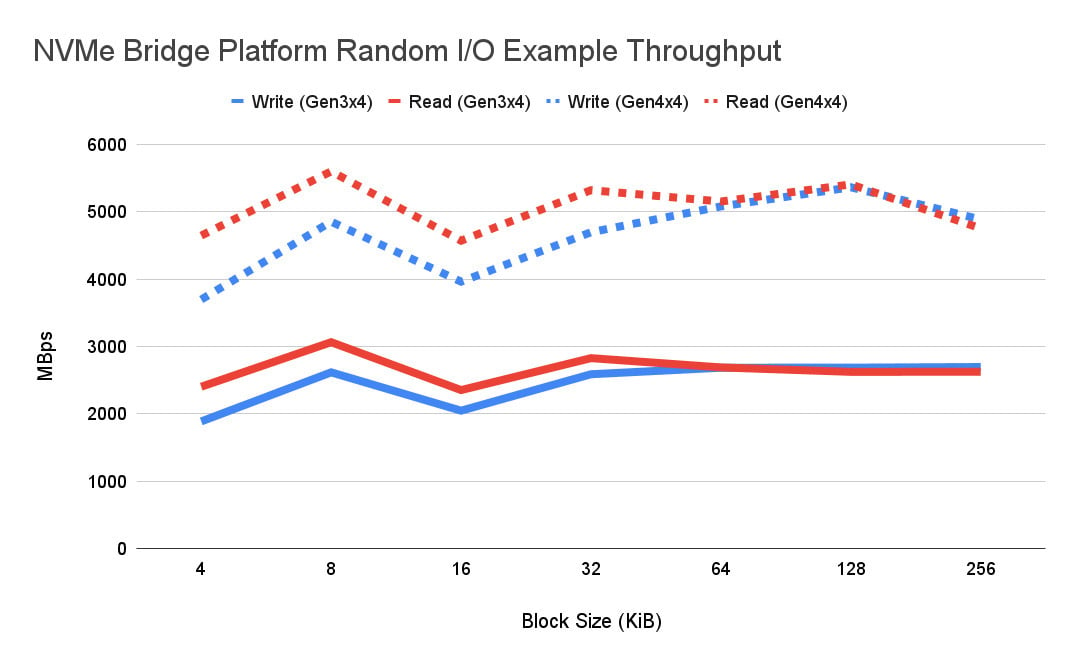

최대 6200MB/s PCIe Gen4x4

여러 SSD를 위한 PCIe 스위치 지원

마커스 웨들, 비트웨어

스토리지 가속화를 위한 FPGA에 초점을 맞춘 비디오로, NVMe 브리지 플랫폼이라는 IntelliProp의 프레임워크에 중점을 두고 있습니다.

오늘은 IntelliProp의 CEO인 Hiren Patel과 함께합니다. 함께 해주셔서 감사합니다!

인텔리프롭 CEO Hiren Patel

감사합니다, 마커스. 이 자리에 함께하게 되어 기쁩니다.

Marcus

간단한 빌딩 블록부터 시작하겠습니다. 예를 들어 매우 빠른 스토리지인 SSD 스토리지를 호스트 PCIe 버스에 연결하는 대신 그 중간에 FPGA를 넣을 것입니다. 그렇다면 첫 번째 질문은 왜 그렇게 할까요?

Hiren

여러 가지 이유가 있겠지만, SSD 앞의 FPGA를 사용하면 데이터 캡처(데이터 수집 시스템)를 구축하여 데이터를 SSD에 직접 저장한 다음 나중에 PCIe를 통해 호스트에서 다시 읽을 수 있습니다.

하지만 다시 한 번, 미리 로드할 수 있는 데이터 수집이 있습니다. 또한 브리지를 사용하면 요즘 성장하고 있는 새로운 시장인 컴퓨팅 스토리지를 공략할 수 있습니다.

우리는 특정 가속기 기능을 FPGA에 직접 오프로드할 수 있는 기능을 갖추고 있으며, 그러면 FPGA가 SSD에서 데이터를 검색하고 처리한 후 다시 호스트에 푸시하거나 다시 푸시할 수 있습니다. 이것이 현재로서는 가장 큰 두 가지 이유일 것입니다.

Marcus

데이터 수집 또는 데이터 캡처의 경우, FPGA를 사용하면 어떤 특별한 점이 있을까요? 왜냐하면... 다른 데이터 캡처 방법도 있는데... FPGA를 사용한 다음 이 브리지 프레임워크를 사용하는 것의 특별한 점은 무엇일까요?

Hiren

네, 또 좋은 질문입니다. FPGA를 빈 캔버스와 같다고 생각하시죠? FPGA에는 수많은 인터커넥트가 있습니다. 다른 종류의 데이터 수집, 온도 센서 등을 넣을 수 있는 연결 지점이 많고, 그 데이터를 가져와서 SSD에 넣을 수 있습니다. 이것이 주요 기준 중 하나입니다.

다른 기준은 FPGA에 강력한 프로세싱이 내장되어 있고, 요즘에는 여러 프로세서를 내려놓을 수 있는 ARM 코어가 있다는 것입니다. 데이터가 SSD에 도착하기 전에 모든 종류의 처리를 수행할 수 있습니다.

특히 브릿지 - 왜 브릿지를 사용하나요? 브리지는 주로 데이터 통과를 허용하므로 쓰기와 읽기 통과를 허용할 수 있습니다. 하지만 특정 명령을 가로챌 수도 있습니다. 필요에 따라 데이터를 가로챌 수 있으므로 호스트가 FPGA에 직접 명령을 내리고 FPGA가 SSD에서 더 많은 데이터를 검색하거나 검색 또는 일종의 가속 기능 등 필요한 작업을 수행한 다음 데이터를 다시 푸시할 수 있습니다. 따라서 FPGA에는 많은 용도가 있습니다.

또 한 가지 말씀드리고 싶은 것은 FPGA는 커스터마이징이 가능하기 때문에 실제로 하나의 FPGA를 여러 제품으로 만들 수 있다는 것입니다. SSD 앞에 FPGA를 빈 제품으로 가져와서 다른 알고리즘이나 다른 가속을 적용할 수 있습니다.

하나의 알고리즘은 압축일 수 있고, 다른 알고리즘은 압축 해제일 수 있으며, 암호화일 수도 있습니다. 검색과 같은 작업도 할 수 있습니다. 이러한 기능은 모두 특정 요구 사항에 맞는 가속기 기능이며, 한 가지가 모든 것을 충족하는 것은 아닙니다.

Marcus

Hiren, 호스트 CPU가 호스트 PCIe 버스가 아닌 FPGA에 직접 연결되어 있어도 호스트 CPU가 SSD를 볼 수 있는 프레임워크의 브리지 구성 요소로 이 개념을 소개하셨습니다. 하지만 이 모든 것이 작동하려면 사용자가 특별한 API를 실행해야 하거나 소프트웨어를 수정해야 할까요?

Hiren

아니요, 바로 사용할 수 없습니다. 셸에 브리지 플랫폼만 있으면 바로 호스트 PC와 SSD 사이에 연결할 수 있습니다. 아니요, 아무것도 변경할 필요가 없습니다. 호스트는 실제로 SSD가 직접 연결된 것처럼 열거합니다.

이제 가속 기능이나 데이터 캡처를 시작하려면 드라이버가 추가로 필요하거나 공급업체별 세부 정보를 통해 모든 작업을 수행할 수 있습니다. 공급업체별 명령을 브리지로 직접 전송할 수 있는 CLI가 있으며, 브리지는 이를 가로채서 필요에 따라 데이터를 처리할 수 있습니다.

Marcus

이제 구체적인 BittWare 하드웨어와 성능에 대해 이야기해 보겠습니다. 여기에서 볼 수 있는 BittWare IA-840f처럼 FPGA에 SSD를 직접 연결할 수 있는 FPGA 카드는 시중에 그리 많지 않다는 점에 주목하는 것이 중요하다고 생각합니다. 또한 이 카드에는 인텔의 최신 실리콘과 Agilex FPGA가 탑재되어 있다는 장점도 있습니다. 그렇다면 이러한 것들이 가져올 수 있는 이점과 지표에는 어떤 것이 있을까요?

Hiren

네, 맞습니다. 확실히 이러한 최신 FPGA는 PCIe에서 점점 더 빠른 세대 속도를 향해 나아가고 있습니다. 현재 애질렉스 보드는 곧 출시될 5세대와 함께 4세대에 도달할 수 있다고 생각합니다. 그리고 이 보드는 그 자체로 엄청난 업적이라고 생각합니다.

그리고 다시 브릿지를 통해 Gen4 x16을 PC 쪽으로 연결한 다음 뒷면에 여러 개의 SSD를 통합할 수 있습니다. Gen4 x4에서 4개의 SSD를 사용하는 것만으로도 포화 상태의 일부를 해소할 수 있습니다.

또한 3세대 x4 레인에 8개의 드라이브를 장착하여 포화 상태에 도달할 수 있습니다.

따라서 4개의 드라이브, 8개의 드라이브 등 많은 드라이브를 장착할 수 있습니다. 하지만 기본적으로 모든 트래픽은 FPGA를 통해 전달되기 때문에 컴퓨팅 스토리지나 데이터 수집을 수행할 수 있습니다.

Marcus

이러한 대역폭 수치에는 어떤 것들이 있을까요? 4개의 드라이브가 FPGA에 연결되어 있거나 심지어 FPGA가 8개의 드라이브가 있는 PCIe 스위치에 연결되어 있다고 가정해 보겠습니다. 그렇다면 Gen4 PCIe 수준에서 기대할 수 있는 성능 수치는 어느 정도일까요?

Hiren

따라서 4세대 수준에서는 단일 드라이브에서 초당 6,000메가바이트에 근접할 수 있을 것으로 예상됩니다. 3세대 속도에서는 이미 초당 3,000메가바이트에 가까운 3,500메가바이트 이상의 속도로 작동하는 브리지를 선보일 수 있습니다. 4세대에서는 그 두 배가 될 것으로 예상합니다.

Marcus

그리고 FPGA를 배포하는 사람들이 자주 제기하는 또 다른 질문은 브리지 IP와 함께 FPGA에 얼마나 많은 자체 IP를 넣을 수 있는가 하는 것입니다. 다시 말해, 다른 사람들을 위해 얼마나 많은 공간을 확보할 수 있을까요? 이에 대해 간단히 말씀해 주시겠습니까?

Hiren

네, 좋네요. 이 특정 보드에는 AGF027 부품이 있는 것 같습니다. 그 부품에는 아마 약 90만 개의 ALE/ALM이 있을 겁니다. 저희는 브리지에 약 10만 개를 사용합니다. 이는 단일 드라이브 연결을 위한 것입니다. 드라이브 연결이 여러 개라면 이를 확장하기 위해 약 4,000개의 ALM을 추가해야 합니다.

그렇게 나쁘지 않습니다. 그래도 10% 정도에 불과합니다. 따라서 고객은 여전히 가속 기능을 추가할 수 있는 충분한 양의 로직을 사용할 수 있습니다.

Marcus

하나의 드라이브 또는 여러 개의 드라이브를 카드에 직접 연결할 수 있다고 말씀하셨습니다. 이제 더 많은 드라이브를 연결하고 싶고 카드가 물리적으로 8개의 드라이브와 같이 연결할 수 있다면 정확히 어떻게 할 수 있나요?

Hiren

하나의 카드로도 여러 개의 드라이브를 연결할 수 있고, 이를 백플레인으로 확장하여 추가 드라이브를 연결할 수 있는 PCIe 스위치가 있는 백플레인으로 확장할 수도 있습니다. 따라서 8개의 드라이브를 PCIe 스위치에 연결한 다음 PCIe 스위치를 BittWare 카드에 연결할 수 있습니다. 이것이 가능한 솔루션 또는 토폴로지 중 하나라고 생각합니다.

Marcus

앞서 이야기했던 두 번째 사용 사례 그룹, 즉 인라인 가속기인 FPGA로 돌아가 보겠습니다. 이것은 컴퓨팅 스토리지 가속화의 큰 그림의 일부이며 CPU 오프로드에 대한 인기가 높아지고 있습니다. 컴퓨팅 스토리지용 인라인 가속기의 사용 사례 몇 가지를 소개해 주시겠어요?

Hiren

네, 맞습니다. 그래서 오늘날 많은 고객들이 미사용 데이터 암호화를 사용하고 있습니다. 따라서 FPGA는 SSD 또는 여러 개의 SSD 앞에 위치하며, 샌드박스 영역 또는 고객 가속 영역을 미사용 데이터 암호화로 사용하는 고객이 이를 사용합니다. 하지만 고객들은 검색 엔진, 검색 오프로드, 압축 eBPF도 또 다른 성장 영역입니다.

고객이 할 수 있는 일들 중 일부입니다. 압축 또는 압축 해제를 예로 들어보면, 브릿지로 할 수 있는 일 중 하나는 서버나 호스트가 브릿지를 통해 압축된 데이터를 변경하지 않고 SSD로 전송하도록 할 수 있습니다.

하지만 데이터를 검색할 때 압축 해제 하드웨어 엔진이 FPGA에 내장되어 있을 수 있습니다. 그러면 압축 해제 엔진이 데이터를 서버 호스트로 다시 전송하기 전에 압축을 해제할 수 있으며, 이것이 바로 우리가 볼 수 있는 사용 사례 중 하나라고 생각합니다.

앞서 말씀드린 것처럼 다른 사용 사례로는 eBPF가 있으며, 인텔리프롭이 이에 대한 레퍼런스 디자인을 개발하고 있는 것으로 알고 있습니다. 또 다른 사용 사례로는 eBPF 가상 머신이 있습니다.

Marcus

앞서 언급했지만 더 자세히 알고 싶었던 한 가지 사용 사례는 호스트가 검색 명령을 실행한 다음 검색 자체를 FPGA와 직접 연결된 SSD로 오프로드하는 것입니다. 압축 오프로드보다 조금 더 복잡하기 때문에 검색 오프로드는 어떻게 작동하나요?

Hiren

네, 좋은 질문입니다. 지난 11월에 세인트루이스에서 열린 슈퍼컴퓨트 '21에서 선보인 것 중 하나는 인라인 브리지가 실제로 검색 엔진을 오프로드하는 모습을 보여드린 것입니다. 그래서 CPU가 많은 양의 데이터를 SSD에 미리 로드하도록 했습니다. 서버가 브리지 중간에 공급업체별 명령을 보내면 RTL 코드가 공급업체별 명령을 보고 특정 패턴 검색을 수행할 LBA 또는 주소 공간 범위를 가져와서 서버로부터 패턴을 수신하도록 했습니다. 일단 패턴과 검색할 LBA 범위를 받으면, 우리는 나가서 우리가 읽어야 하는 전체 드라이브 섹션을 읽고, 특정 32비트 패턴을 찾고, 그 패턴의 모든 인스턴스, 즉 어떤 LBA에서 발생했는지 찾아서 이를 패키지화하여 서버 호스트에 완료를 다시 보냅니다.

일반적으로 가속기가 없었다면 서버는 모든 데이터를 시스템 메모리로 읽고 검색을 수행한 다음 데이터를 버려야 했을 것입니다. 이러한 데이터 이동 없이도 서버는 우리에게 명령을 내리기만 하면 "데이터를 찾은 모든 위치가 여기 있습니다"라는 응답을 전송했습니다. FPGA는 솔직히 이 작업을 훨씬 더 빠르게 수행할 수 있었고 그래프로도 이를 보여줄 수 있었습니다.

이제 데모 중 일부를 살펴보겠습니다. 위쪽 선은 직접 검색을 수행하는 동안 약 90%의 속도로 실행되는 CPU 부하를 보여주고 있지만, 그 사이에 FPGA 오프로드 버전이 당연히 몇 배 더 빠르며 CPU를 오프로드하고 있습니다... 여기서 어떤 FPGA를 사용하고 있나요?

예, 비디오의 데모는 Intel Stratix 10 DX에서 수행되었습니다.

특정 프레임워크 IP를 브릿지와 함께 사용해야 하는 시기를 어떻게 알 수 있나요? 브리지 구성 요소가 특히 필요한 시기를 어떻게 인식할 수 있나요?

네, 좋은 질문입니다. 다시 말씀드리지만, 패스스루 브리지입니다. 우리가 한 일은 NVMe의 복잡성을 모두 제거한 것입니다. 고객이 로직을 넣을 수 있는 AXI 스트림 인터페이스를 만들었습니다. 따라서 고객은 가속 기능에는 능숙하지만 NVMe에 대해서는 전문가가 아닐 수 있으며, 바로 이 부분에서 프레임워크의 진가가 빛을 발합니다. 우리는 데이터와 명령어 및 모든 것을 AXI 스트림을 통해 제어 및 데이터 정보로 중간에 제시하고 고객이 그 로직으로 무엇을 할 것인지 결정하도록 합니다.

그리고 반대편에는 데이터를 SSD로 계속 이동시키는 제어 및 데이터 플레인(다시 AXI 스트림)이 있습니다.

양방향으로 작동하므로 사용 편의성 측면에서 우리가 정말 빛나는 부분이 바로 이 부분입니다. 가속 기능에 대한 전문 지식이 있는 고객은 이를 샌드박스에 넣기만 하면 됩니다.

시장 출시 시간이 훨씬 단축됩니다. 그리고 BittWare의 도움을 받아 실제로 그 시간을 훨씬 더 단축할 수 있었습니다. 이제 샌드박스 브리지에 실제로 연결할 수 있는 실리콘, 즉 NVMe 브리지 플랫폼이 생겼고, 가속 기능을 계속 구축할 수 있는 플랫폼이 생겼기 때문입니다.

Marcus

자, 이제 이를 바탕으로, 그리고 이것이 마지막 질문입니다. 이 NVMe 브리지 IP를 직접 구축하는 것과 IntelliProp을 사용하는 것을 고려하는 시청자들을 위해... 실제로 IntelliProp을 사용하는 데 얼마나 걸렸으며 이제 이를 사용하여 애플리케이션을 구축하는 것이 얼마나 쉬워졌는지 궁금합니다.

Hiren

네, 그렇군요. 따라서 이 프레임워크는 사용자가 NVMe와 상호 작용해야 한다는 사실을 숨기거나 추정해낸 것이라고 말씀드리고 싶습니다. NVMe에 대해 아무것도 모를 필요는 없습니다. 어떤 주소와 제어 정보를 얻고 있는지만 알면 됩니다.

인텔리프롭은 이 브릿지를 개발하고 원하는 성능을 구현하는 데 약 1년 반이 걸렸습니다. 궁극적으로 고객의 시간을 절약할 수 있게 되었습니다.

예를 들어, 우리가 했던 SuperCompute '21 데모로 돌아가서 약 한 달 만에 해냈습니다. 브릿지가 없었다면 훨씬 더 오래 걸렸을 것입니다. 브릿지가 있고 제어 정보, 즉 우리가 얻고 있는 데이터 정보를 알고 있었기 때문에 가속 검색 기능과 데이터를 다시 전송하는 기능을 실제로 수행하는 데만 한 달이 걸렸습니다.

다시 말하지만, 이는 프레임워크이며, 모든 것이 미리 구축되어 있고, 플러시됩니다. 가속에만 집중하기만 하면 됩니다.

Marcus

좋아요, 훌륭합니다. 오늘 이 모든 것에 대해 이야기해 주셔서 감사합니다.

Hiren

감사합니다.

Marcus

이것이 바로 BittWare FPGA 카드에서 사용할 수 있는 IntelliProp의 프레임워크인 NVMe 브리지 플랫폼입니다. 특히 오늘은 직접 연결된 SSD가 장착된 IA-840F를 살펴보겠습니다. 자세한 내용은 BittWare 웹사이트를 방문하시고 시청해 주셔서 감사합니다.

특징

- NVM Express 1.4c 산업 사양을 완벽하게 준수합니다.

- PCIe 하드 블록으로 자동 초기화

- 여러 SSD를 위한 PCIe 스위치 지원

- 자동화된 명령 제출 및 완료

- 확장 가능한 I/O 대기열 깊이

- 분리된 프론트엔드 및 백엔드 인터페이스로 유연한 사용자 로직 및 애플리케이션 지원

- 유연한 데이터 버퍼 유형 및 크기

- AXI 스트림 기반 명령 및 데이터 경로

- 데이터 스트림에 명령 매개변수 인라인 포함

- 512바이트에서 4kB까지 블록 크기 지원

- 애플리케이션 계층 인터페이스를 통해 프로세서가 관리 명령을 제어하거나 수정할 수 있습니다.

- Verilog 및 VHDL 래퍼

NVMe 브리지 플랫폼 I/O 처리량

NVMe 브리지 플랫폼 IP 핵심 정보

제공 코어 포함

- 문서: 종합적인 사용자 설명서

- 디자인 파일 형식: 암호화된 베릴로그

- 제약 조건 파일: FPGA당 제공

- 검증: ModelSim 검증 모델

- 인스턴스화 템플릿: Verilog(VHDL 래퍼 사용 가능)

- 레퍼런스 디자인 및 애플리케이션 노트 스크립트 합성 및 배치 및 라우팅

- 추가 항목: 참조 설계

사용된 시뮬레이션 도구:

QuestaSim(지원되는 최신 버전은 IntelliProp에 문의)

지원:

정식 라이선스가 부여된 코어에 대해 배송일로부터 6개월 동안 전화 및 이메일 지원이 제공됩니다.

참고:

다른 시뮬레이터를 사용할 수 있습니다. 자세한 내용은 IntelliProp에 문의하세요.

블록 다이어그램, 데이터 시트 및 제품 세부 정보

애플리케이션

NBP IP는 호스트에 PCIe Gen4를 사용하는 CSD(컴퓨팅 스토리지 디바이스) 또는 CSA(컴퓨팅 스토리지 어레이)에서 사용할 수 있으며, 스위치 또는 별도의 PCIe 연결을 통해 여러 개의 PCIe Gen4 SSD를 사용할 수 있습니다.

기능 설명

인텔리프롭 NBP인 IPC-NV171B-BR은 인텔리프롭 NVMe 타겟 코어를 통해 명령을 수신 및 파싱하고 이를 인텔리프롭 NVMe 호스트 액셀러레이터 코어로 전달하여 NVMe SSD 엔드포인트에 전달하는 프로토콜 브리지를 구현합니다. 이 두 코어 간의 사용자 정의 가능한 브리징 로직은 미해결 명령을 전달 및 추적하고 데이터 액세스를 적절하게 라우팅하는 등 명령 관리를 용이하게 하며, '샌드박스' 영역을 사용하면 호스트와 타겟 간에 전송되는 버퍼링된 데이터에 대한 가시성과 유연성을 제공합니다.

브리징 로직의 레지스터는 펌웨어에 데이터 이동을 제어하고 개별 명령을 수동으로 실행하며 브리징 기능의 상태 및 동작을 제어할 수 있는 메커니즘을 제공합니다. 프로세서 또는 기타 관리 에이전트는 NVMe 타겟 코어로부터 관리 명령을 수신하고 적절하게 완료하는 반면, I/O 명령은 브리징 로직에 의해 자율적으로 실행됩니다. 결과적으로 NBP는 호스트와 엔드포인트 SSD 간에 투명성을 제공하는 동시에 설계자에게 명령 및 데이터 조작의 유연성을 제공합니다.

빈 제목

빈 헤디

블록 설명

NVMe 타겟 코어

NVMe 타겟 코어는 표준 릴리스 IntelliProp 코어(IPC-NV163A-DT)로, PCIe 코어와 함께 작동하여 호환되는 NVMe 장치 인터페이스를 구현하는 하드웨어를 정의합니다. NVMe 타겟 코어는 PCIe 인터페이스를 통해 시스템 호스트에서 명령 제출 항목을 검색하고 여러 명령 FIFO 중 하나에 해당 항목을 배치합니다. 두 개의 데이터 축 스트림(전이중), 즉 명령 컨텍스트 스트림과 완료 컨텍스트 스트림이 있습니다. 명령 완료를 수신하면 NVMe 타겟 코어는 내부 필드를 자동으로 채우고 완료를 호스트 시스템에 게시합니다.

NVMe 명령 가속기

자동화된 내부 상태 머신은 NVMe 타겟 코어와 상호 작용하여 제출 대기열 항목을 가져오고 완료 대기열 항목을 게시합니다. 데이터와 명령은 4개의 AXI 스트림 인터페이스를 통해 사용자 로직에 제공됩니다. NVMe 타겟 코어로부터 IO 명령을 수신하면 NVMe 명령 가속기는 AXI 스트림을 통해 명령을 전달한 다음 PCIe 엔드포인트 코어와 상호 작용하여 사용자 시스템과 NVMe 호스트 간에 데이터를 이동합니다. 통합 레지스터를 통해 사용자는 시스템 구성 및 코어 상태를 제어할 수 있습니다.

NVMe 명령 번역기

4개의 AXI 스트림 인터페이스를 통해 NVMe 명령, 데이터, 완료를 NVMe 명령 가속기와 협상합니다. 두 개의 데이터 AXI 스트림(전이중), 명령 컨텍스트 스트림, 완료 컨텍스트 스트림이 있습니다. 명령을 수신하면 이 블록은 NVMe SSD에서 데이터 전송을 수용하기 위해 버퍼 공간을 할당하고, 명령을 NVMe 호스트 가속기로 전달하여 SSD에 실행합니다. SSD에서 데이터와 NVMe 완료가 모두 반환되면 이 블록은 NVMe 명령 가속기에 완료를 반환하고 버퍼 공간을 할당 해제합니다. 통합 레지스터를 통해 사용자는 시스템 구성 및 코어 상태를 제어할 수 있습니다.

샌드박스

NBP의 사용자 로직 공간은 사용자가 NVMe 명령 가속기와 명령 번역기 사이에 사용자 지정 로직을 유연하게 삽입할 수 있도록 합니다. 이 로직은 명령, 완료 및 데이터를 전송하기 위해 표준화된 AXI 스트림 인터페이스를 준수해야 합니다. 명령과 완료는 직접 전달되거나 런타임에 수정(및 내부적으로 추적)될 수 있습니다. 데이터는 인라인으로 명령 매개변수를 포함하므로 해당 명령 컨텍스트에서 분리될 수 있습니다. 데이터 순서나 지연 시간에 대한 제한 없이 사용자 로직은 애플리케이션에 따라 다양한 형태를 취할 수 있습니다.

NVMe 호스트 가속기 코어

NVMe 호스트 가속기 코어는 표준 릴리스 IntelliProp 코어(IPC-NV164A-HI)로, 명령 대기열에 명령을 작성하고 PCIe 루트 컴플렉스 코어 인터페이스를 통해 사용 가능한 명령을 NVMe SSD에 알리는 하드웨어를 구현합니다. NVMe 호스트 가속기 코어에는 명령을 설정하고 완료된 명령을 검색하는 하드와이어드 인터페이스가 있습니다. 마이크로프로세서가 명령 제출을 설정하고 완료를 검색할 수 있도록 AXI 슬레이브 및 NVMe 호스트 액셀러레이터 코어 레지스터도 사용할 수 있습니다.

빈 제목

빈 제목

자세한 기능 목록

전체

- 완벽한 기성 솔루션, 즉시 운영 가능

- 직접 또는 포함된 PCIe 스위치를 통해 여러 개의 NVMe SSD(또는 HDD)를 지원합니다.

- 스위치 또는 별도의 PCIe 연결을 통해 호스트에 PCIe Gen4 및 여러 개의 PCIe Gen4 SSD를 연결할 수 있습니다.

- 제어 및 데이터용 AXI 스트림 인터페이스가 포함된 샌드박스

- 연산 기능의 추가적인 유연성을 위한 시스템 연결 프로세서

샌드박스별

- 4개의 AXI 스트림 인터페이스는 명령, 완료 및 데이터(사이드밴드 메타데이터를 포함한 전이중)를 제공합니다.

- 추가적인 유연성을 위한 프로세서 연결

- 가속을 위한 RTL 또는 FW 구현 옵션 포함

FPGA/하드웨어별

- PCIe Gen4 하드 블록 사전 연결

- 최대 6200MB/s 처리량(Gen4x4 인터페이스)

- 인텔 쿼터스 21.3 프로 툴과 통합

합성 스크립트 및 타이밍 제약 조건

빈 제목

빈 제목8

지원되는 FPGA 장치

| 장치 | 속도 | ALUT | FF | M20k |

|---|---|---|---|---|

| 알테라 애자일렉스 F-시리즈 | -2 | 31674 | 22136 | 190 |

| 알테라 스트라틱스 10 DX | -1 | 31589 | 20038 | 190 |

결과물

핵심에는 성공적인 구현에 필요한 모든 것이 포함되어 있습니다:

- IP 코어 정의를 위한 암호화된 합성 가능한 RTL 코드

- 암호화된 ModelSim/QuestaSim 시뮬레이션 모델

- 종합적인 사용자 설명서

- 레퍼런스 디자인

- 간단한 참조 프로젝트의 예시입니다:

- NVMe 호스트 가속기 IP 코어 인스턴스

- NVMe 타겟 IP 코어 인스턴스

- NVMe 명령 가속기

- NVMe 명령 번역기

- 샌드박스 블록 예시

- 프로세서

- 추억

- 합성 및 배치 및 경로 스크립트

- 참조 코어 제어 펌웨어

- 간단한 참조 프로젝트의 예시입니다:

이용 약관

수정: 일반적으로 IntelliProp의 IP 코어에 대한 코어 수정은 허용되지 않습니다. 요청된 모든 수정 사항은 해당 변경 사항의 통합 타당성을 판단하기 위해 IntelliProp에 제출해야 합니다.

지원: 정식 라이선스가 부여된 코어에 대해서는 배송일로부터 6개월 동안 전화 및 이메일 지원이 제공됩니다.

가격이나 자세한 정보가 궁금하신가요?

기술 영업팀에서 가용성 및 구성 정보를 제공하거나 기술 관련 질문에 답변해 드립니다.

"*"는 필수 필드를 나타냅니다.