ホワイトペーパー

合成トラフィックジェネレータのリファレンスデザイン

概要

対応ハードウエア

当社の最初のシンセティック・トラフィック・ジェネレーター・リリースは、BittWareのXUP-P3Rと 250-SoCカードをターゲットとし、100GbEのみを対象としています。 私たちは、Achronix、AMD、Intelから登場するマルチレート・イーサネット・ハードブロックに備え、これを作成しました。

データキャプチャーのリファレンスデザインに合成トラフィックジェネレーターを搭載

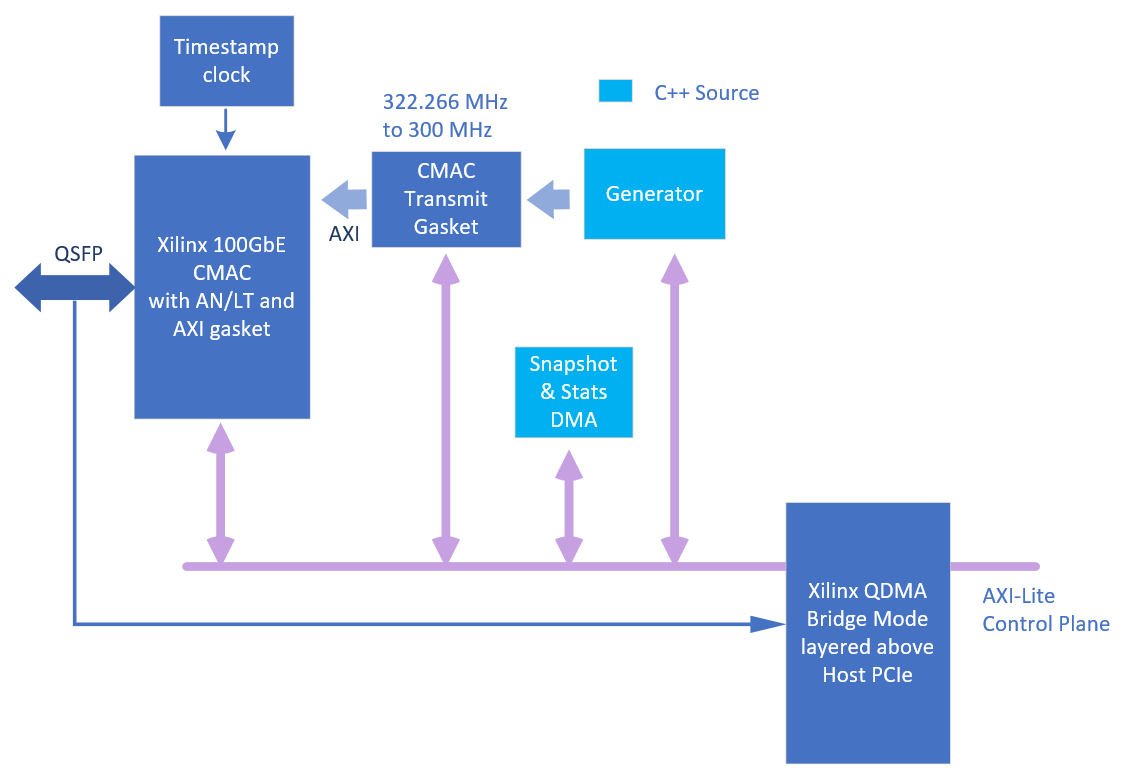

データキャプチャーのアーキテクチャコンセプトの一環として、データキャプチャーのリリース2.0からシンセティック・トラフィック・ジェネレーターをリリースすることになりました。Traffic GeneratorはQSFPの送信側を所有し、Data Captureは同じQSFPの受信側を所有します。これにより、CMACをローカルループバックモードにし(またはループバックケーブルを設置し)、Traffic Generatorを使用してData Captureをテストすることができます。また、通常のDACや光ケーブルを使用して、他のデバイスにトラフィックを送信することも可能です。

FPGAのビットストリームには、次の図のようなパイプラインが含まれています。

機能性

BittWareのSynthetic Traffic Generatorは、FPGA内でEthernetパケットを作成し、付属のネットワークに起動させます。

必要であれば、BittWareの別個のPCIe Data Capture Reference Designを導入して、これらのパケットを受信することができます。もちろん、これはソフトウェアがIPパケットを生成するためにTraffic Generatorを設定することを前提としています。

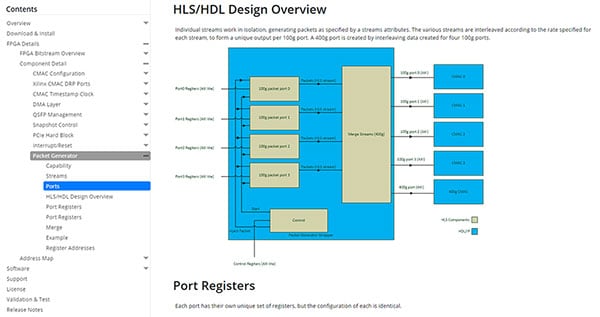

基本的な考え方は、様々なサイズのパケットを、ラインレートで、長時間作成することです。パケットヘッダは変化しない。ペイロード内に増加するパケットシリアル番号を設定することができます。

この「パケットストリーム」は最大32個までインターリーブすることができ、つまり最大32個の異なるパケットヘッダーを持つことができます。受信したパケットストリームを複数の「キュー」に分け、複数のホストCPUコアを用いて処理するターゲットをテストするためには、この機能が必要です。

ランダムなサイズのパケットを設定することもできますが、BittWare 、私たちは代わりにラインレートでデザインを掃引することが多いです。まず、ドロップがないことを確認するために小さなパケットを延々と繰り返し、次にペイロードに1バイトを追加し、ターゲットデザインが許す最大のペイロードに達するまでテストを継続します。

また、進行中のストリームに任意のパケットのインスタンスを1つ挿入することも可能です。これは、エラーを挿入して何が起こるかを確認するのに便利です。

パケットストリームはラインレートで起動する必要はなく、パケット間のギャップを長く定義してパケットレートを下げることができます。最後に、ペイロードデータは、ゼロ、乱数、64バイトの繰り返しパターン、または増加シーケンス(例:0123456789101112...)にすることができます。

ハードウェア

このシンセティック・トラフィック・ジェネレーターは、AMD VU9Pチップ、スピードグレード2を搭載したBittWare XUP-P3Rカードで作成され、テストされました。トラフィックジェネレーターは外部メモリーを使用しません。このデザインは、データキャプチャとトラフィックジェネレータの組み合わせを250-SoCに移植することで実証したように、CMACを含むAMDUltraScale+チップを搭載したBittWare カードに移植する必要があります。

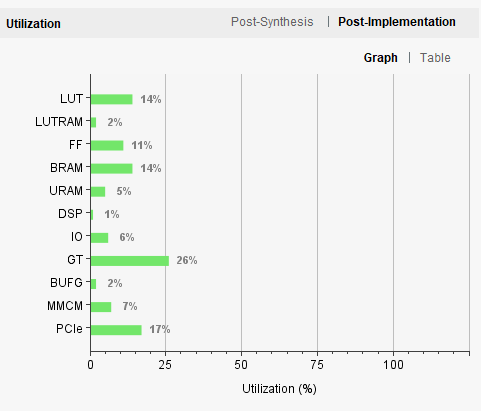

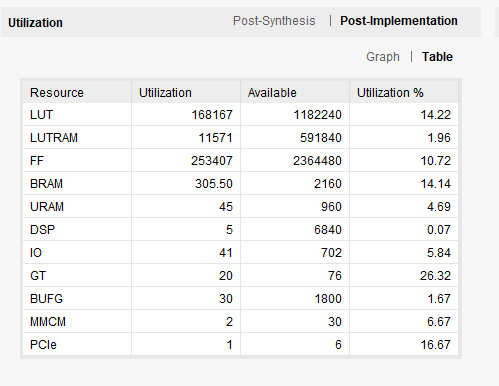

リソースの有効活用

これらの図は、Data Capture リファレンス・デザインの候補 2.0.0 リリース (2021 年 2 月) における FPGA リソース使用率を示しています。これは、私たちが最終的にリリースしたバージョンに、正確ではないにせよ、非常に近いと思われます。

このビットファイルには、リファレンス・デザインのTraffic GeneratorとData Captureの両方が含まれていることに注意してください。

関連プロジェクト/ソリューション

Synthetic Traffic Generatorは、BittWareのシンプルなループバック例で示されたものと同じDACケーブル機能を組み込んでいます。

別の関連プロジェクトであるStreamSurgeは、トラフィックを発生させない。その代わりに、ローカルメモリーバッファからパケットを送信します。これらのパケットはホストコンピュータから送られてくるので、StreamSurgeはより汎用的なツールとなっています。StreamSurgeには、2つの顕著な限界があります。まず、メモリベースの設計のため、400GbEでは特殊なハードウェアが必要となります。具体的には、400GbEとHBMの両方を搭載したカードが必要です。第二に、StreamSurgeのソースを構築するには、サードパーティのDPDK IPブロックのライセンスを取得する必要があります。

フル機能のトラフィックジェネレーターについては、100GbEでBittWare のハードウェアを使用する、お得なSiama PROVA-Cアプライアンスへの切り替えを見込んでいます。

まとめ・アプリノートへのリクエスト

BittWareのデータキャプチャーのリファレンスデザインには、この合成トラフィックジェネレーター(現在は100Gb/s用)が使用されています。私たちは、独自のセンサートラフィックを生成できるなど、その機能を共有したいと思いました。

より詳しく知りたい方は、以下のフォームからTraffic GeneratorのドキュメントであるApp Noteを請求していただければと思います。

もっと読みたいものがある:合成トラフィックジェネレーターのアプリを入手する Note

PDFダウンロードを希望する

このページで紹介するのは、BittWare's Synthetic Traffic Generatorの紹介です。アプリノートには、より多くの詳細が記載されています!フォームにご記入の上、PDF版のアプリノートへのアクセスをご請求ください。

"*"は必須項目