ホワイトペーパー

BittWare ネットワークパケット処理用SmartNIC Shellのご紹介です。

概要

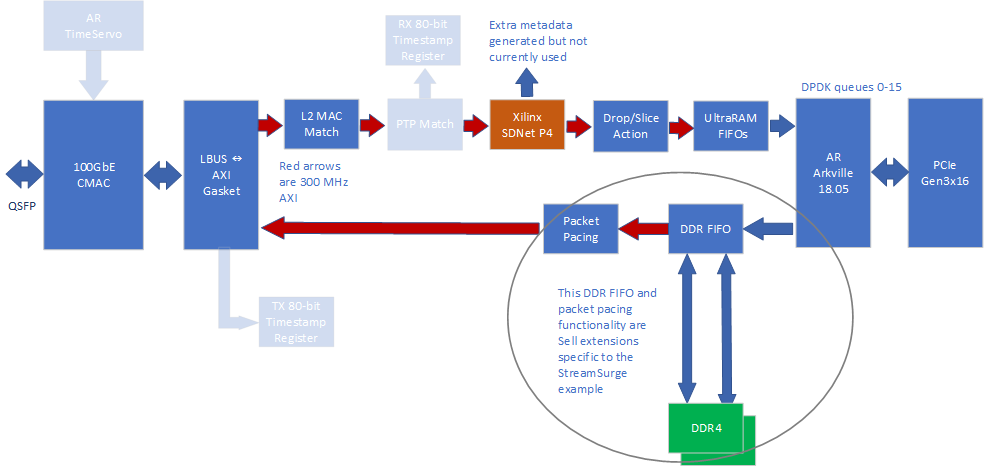

SmartNIC Shellは、BittWare FPGAボードに実装された完全な動作するNICで、ユーザがFPGAの価値を追加する出発点として使用します。SmartNIC Shellを使用すると、ネットワーク機能(NFV)、ネットワーク監視、特殊なパケットブローカー、またはパケットを操作するその他のものを迅速に展開することができます。シェルは、ホスト・アプリケーションと対話するためのDPDKオフロードを提供し、FPGAプロジェクト・ソースおよび完全機能のビットストリームとして提供されます。

SmartNIC Shellについて

SmartNIC Shellに含まれるものは何ですか?

- Arkville™ DPDK/AXIを意識したデータムーバー(アトミック・ルール)。

- PCIe Hard IP (ザイリンクス)

- AN/LT付き100Gイーサネットサブシステム (ザイリンクス)

- パケットペーシング(フレーム間ギャップ)ブロック (BittWare)

- UltraRam FIFOブロック (BittWare)

- ドロップ/スライスブロック (BittWare)

- Lbus-to-AXIコア (BittWare)

- DDR4 FIFO (BittWare)

- L2マッチ/アクションフィルター(BittWare)

- HLSベースパーサー (BittWare)

- HLSベースのRSS (BittWare)

対応製品

SmartNIC Shellは、以下のBittWare の製品に対応しています:

- XUPP3R: VU9P FPGA搭載の3/4レングスPCIe、スピードグレード2、4つのQSFPのうち1つが有効です。

ライセンシング

ループバックのFPGAビットストリームには、いくつかのコンポーネントが含まれています。各コンポーネントは、データプレーンとして使用される入力と出力の両方にまとめてAXI4-Streamインターフェイスを備えています。ビットストリームの制御プレーンは、物理PCIeインターフェイスに接続されたAXI4-Liteインターフェイスを使用します。

デザインの流れ

- BittWare は、Atomic Rules社からArkville™ DPDKとTimeServo™コアのライセンスを受け、それらを再配布します。BittWare は、BittWare's SmartNIC Shellの一部として、Arkville の上に価値を追加します。

- FPGA プロジェクトを構築するためには、「Xilinx 100G Ethernet Subsystem with AN/LT」のライセンスが利用可能である必要があります。

- FPGAプロジェクトでは、Vivado 2018.3が必要です。

ミティヘッド

空の見出し

ディーピーディーケー

SmartNIC ShellがDPDKを実装するまでの流れ

DPDKはBittWare カード上のFPGAに実装されています。BittWare'アトミック・ルールズとの共同作業は、FPGA内部にDPDKを実装した最初のものです。

BittWare ボードは、Atomic Rules PMD のパッチを当てたバージョンを使用しています。ベースとなるPMDはDPDKディストリビューションに含まれています。BittWare 、必要なパッチはソースディストリビューションの一部として提供されています。BittWareの DPDK によるテストでは、BittWorks II ドライバを置き換える uio_pci_generic ドライバが使用されています。しかし、BittWorks IIのツールの一部はまだ動作します。

ユーザーには、以下のような特典があります:

- FPGAの中に入れる「データムーバー」で、片方はAXIバス、もう片方はPCIeインターフェースに接続します。ザイリンクスまたはインテルの暗号化ライセンス方式で提供されます。これには、各社のオプションを活用して、期間限定の評価を提供することも含まれます

- DPDKと上記のデータムーバーを接続するためのオープンソースのDPDKポールモードドライバ(PMD)です。このPMDは、DPDK 17.05から公式のDPDKリリースの一部となり、"Arkville"という名前で提供されています。

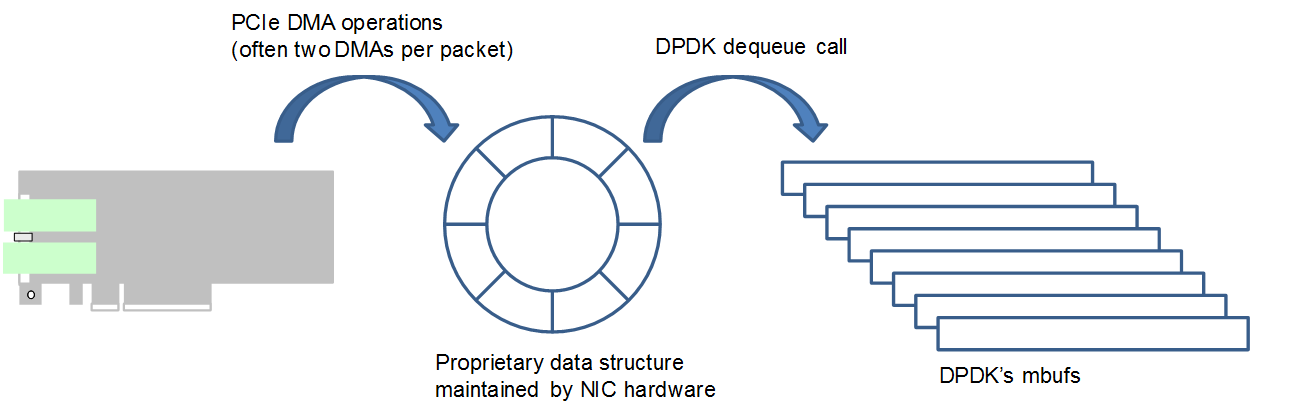

ASICやFPGAのDPDK実装の多くは、1回のコピーを実行します:

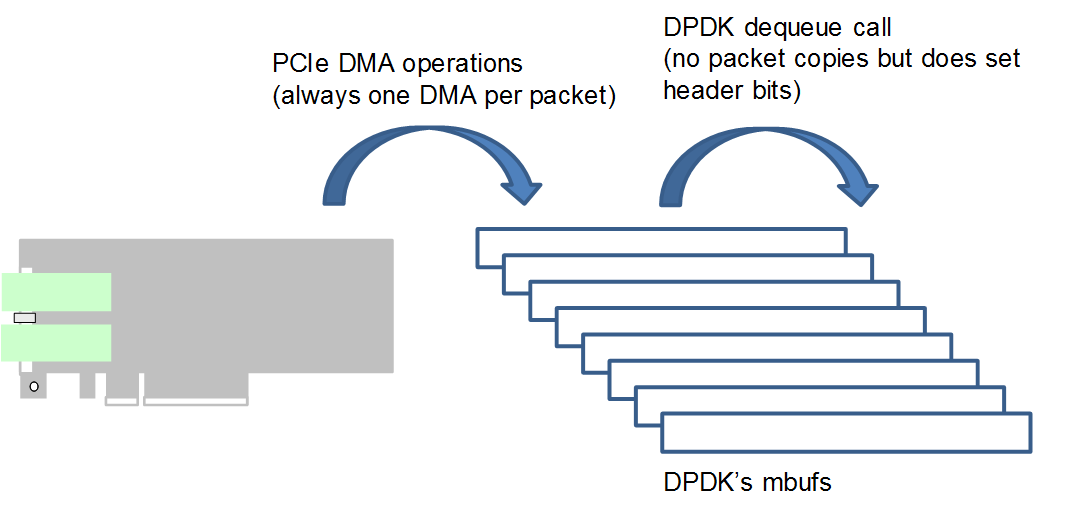

一方、SmartNIC ShellのDPDK IPコアは、常にDPDK mbufに直接DMAを行い、CPUがパケットデータをコピーする必要はありません。メタデータのための2回目のDMAは不要で、CPUのオーバーヘッド、レイテンシ、ホスト・メモリの要件を削減します。このため、小さなパケットをより少ないDMAで結合したり、PCAPレコードとして事前にフォーマットされたデータを書き込むなど、PCIeの最適化を行う機会が失われます。必要であれば、アプリケーション・コードがDPDKコアの上のFPGAでこれらの処理を行うことができます。

もっと読みたいものがある:SmartNIC Shell App Noteを入手する

PDFダウンロードを希望する

このページで紹介するのは、BittWareの SmartNIC Shell の紹介です。App Noteには、さらに多くの詳細が記載されています!フォームに記入して、フルアプリケーションノートのPDFバージョンへのアクセスをリクエストしてください。

"*"は必須項目