白皮書

介紹BittWare用於網路數據包處理的SmartNIC Shell。

概述

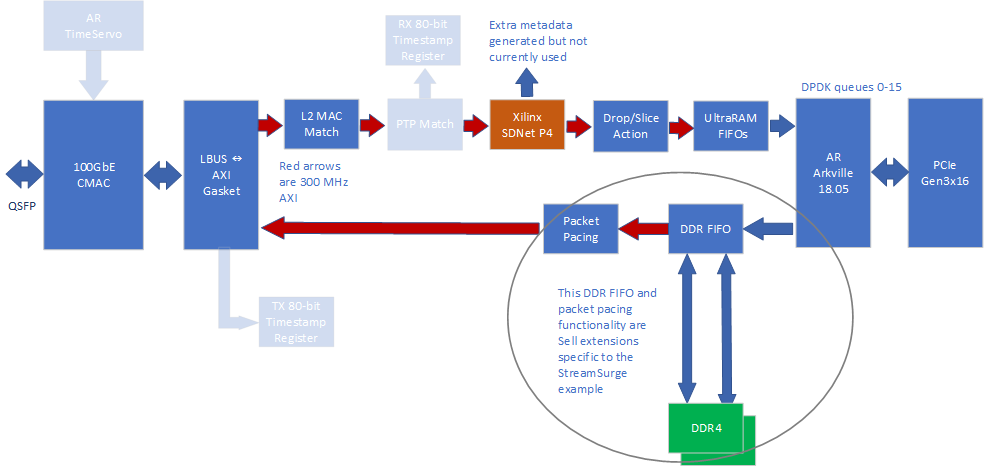

SmartNIC Shell是一個完整的工作NIC,在BittWare FPGA板上實現,作為使用者添加FPGA值的起點。您可以使用 SmartNIC 外殼快速部署網路功能 (NFV)、網路監控、專用數據包代理或任何其他操作數據包的內容。外殼提供 DPDK 卸載以與主機應用程式交互;它作為 FPGA 專案源和功能齊全的比特流交付。

關於智慧網卡外殼

SmartNIC Shell 包含哪些內容?

- 阿克維爾 ™ DPDK/AXI 感知資料行動器(原子規則)

- PCIe 硬 IP (賽靈思)

- 採用 AN/LT 的 100G 乙太網子系統 (Xilinx)

- 數據包起搏(幀間間隙)塊(BittWare)

- UltraRam FIFO block (BittWare)

- 拖放/切片塊(BittWare)

- Lbus-to-AXI Core (BittWare)

- DDR4 FIFO (BittWare)

- L2 符合/操作篩選器 (BittWare)

- 基於HLS的解析器(BittWare)

- 基於 HLS 的 RSS (BittWare)

支援的產品

SmartNIC Shell支援以下BittWare產品:

- XUPP3R:3/4 長度 PCIe,配備 VU9P FPGA,速度等級 2,啟用四個 QSFP 之一。

發 牌

環迴的 FPGA 比特流包含多個元件。每個元件在輸入和輸出上都有一個 AXI4-Stream 介面,統稱為數據平面。比特流的控制平面使用連接到物理PCIe介面的AXI4-Lite介面。

設計流程

- BittWare從Atomic Rules授權Arkville™ DPDK和TimeServo™內核並重新分發它們。BittWare作為BittWare的SmartNIC Shell的一部分,在Arkville之上增加了價值。

- “帶 AN/LT 的 Xilinx 100G 乙太網子系統”的許可證必須可供 FPGA 項目構建。

- FPGA 專案需要 Vivado 2018.3

MPTY標題

空標題

朝鮮民主主義人民共和國

智慧網卡外殼如何實現 DPDK

DPDK在BittWare卡上的FPGA中實現。BittWare與Atomic Rules的共同努力是FPGA中第一個DPDK實現。

BittWare開發板使用Atomic Rules PMD的修補版本。基本 PMD 包含在 DPDK 發行版中。BittWare提供必要的補丁作為我們原始程式碼分發的一部分。BittWare使用DPDK進行的所有測試都使用uio_pci_generic驅動程式,該驅動程式取代了BittWorks II驅動程式。但是,一些BittWorks II工具仍然可以工作。

使用者會收到以下內容:

- 一個「數據行動器」,用於放置在FPGA內部,一側連接到AXI總線,另一側連接到PCIe介面。它採用 Xilinx 或英特爾加密許可方案交付。這包括利用每家公司的選擇來提供限時評估

- 一個開源 DPDK 輪詢模式驅動程式 (PMD),用於將 DPDK 連接到上述數據行動器。此 PMD 成為 DPDK 官方版本的一部分,從 DPDK 17.05 開始,名稱為“Arkville”

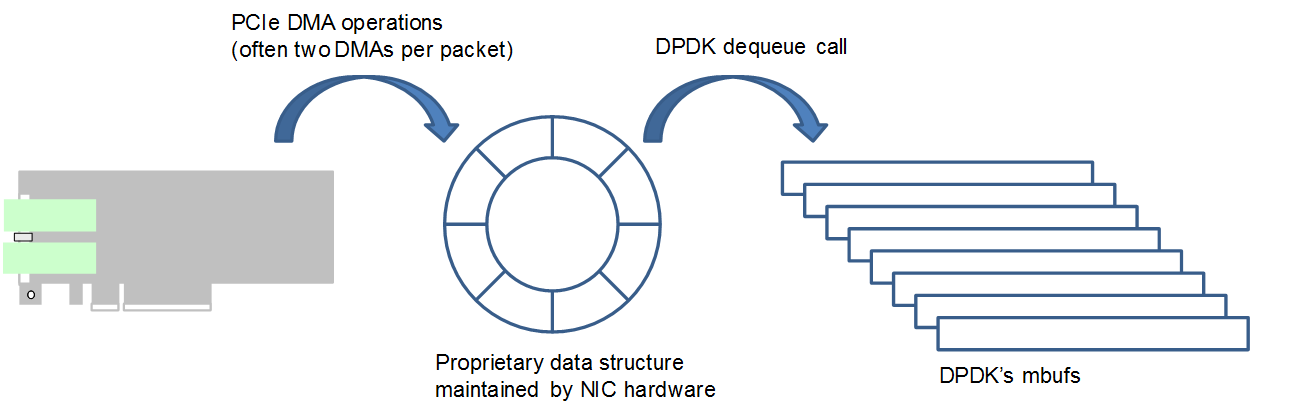

大多數 ASIC 和 FPGA DPDK 實現執行一個拷貝:

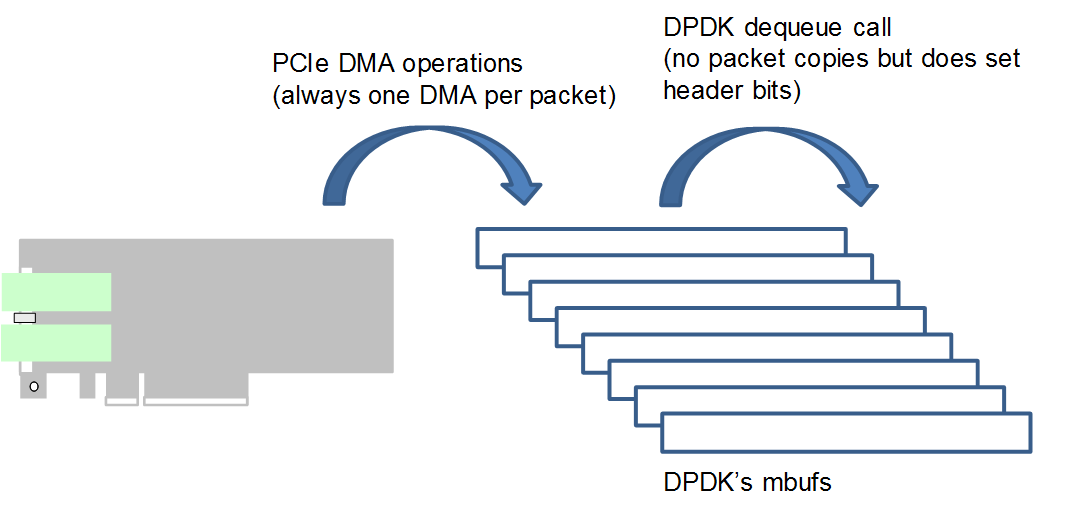

相比之下,SmartNIC Shell 的 DPDK IP 核始終將 DMA 直接連接到 DPDK mbuf,從不需要 CPU 複製數據包數據。元數據不需要第二個 DMA,從而減少了 CPU 開銷、延遲和主機記憶體要求。這確實消除了某些 PCIe 優化的機會,例如將小數據包合併為更少的 DMA 或寫入預先格式化為 PCAP 記錄的數據。如果需要,您的應用代碼可以在 DPDK 內核上方的 FPGA 中執行這些操作。

還有更多內容要閱讀:獲取SmartNIC外殼應用說明

請求 PDF 下載

您在此頁面上看到的是BittWare的SmartNIC Shell的介紹 。完整的應用說明中還有更多細節!填寫表格以請求訪問完整應用筆記的PDF版本。

“*”表示必填欄位