為什麼使用 FPGA 進行計算加速?

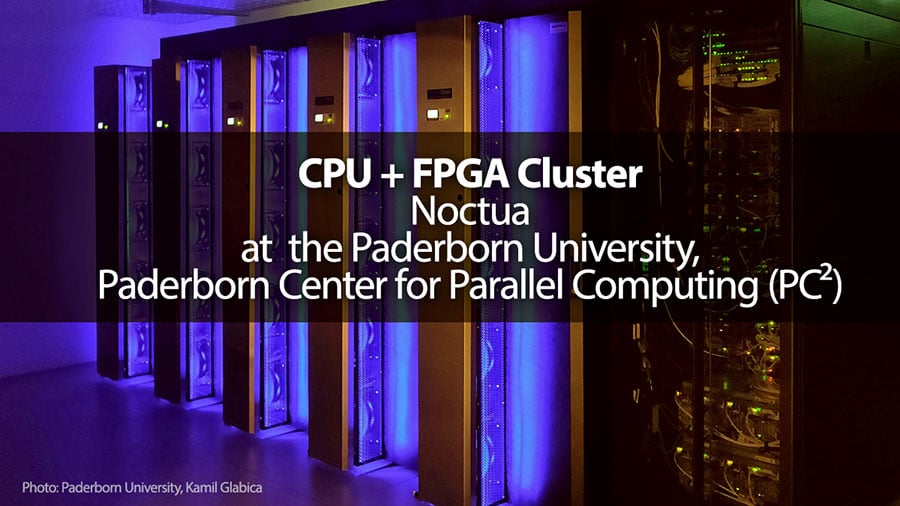

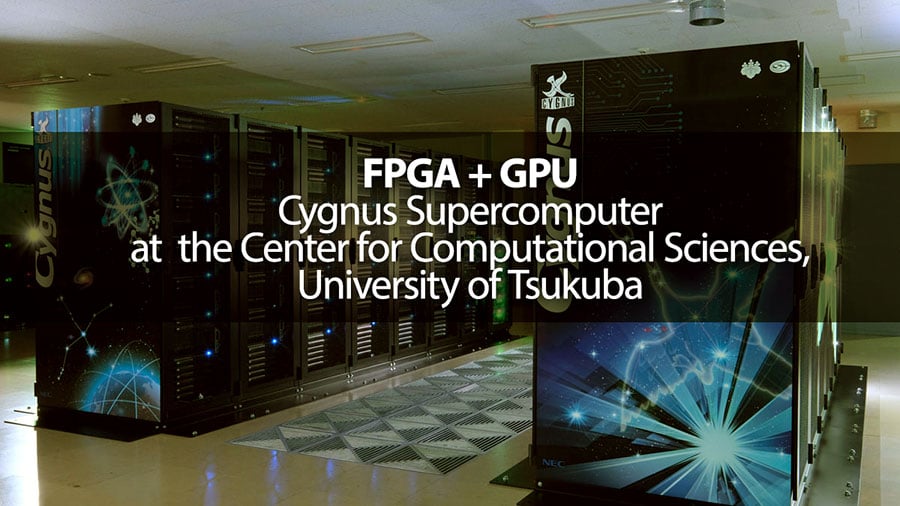

客戶越來越多地部署 異構 平臺,這些平臺具有多種互補技術協同工作。

FPGA 為各種 HPC 應用提供 高性能、工作負載 靈活性 和高 能效 操作。

核心 FPGA 對高性能計算的優勢

近年來,面向 HPC 的 FPGA 價值主張 得到了顯著加強。

這些是BWNN白皮書中展示的關鍵優勢:

效能 加速度

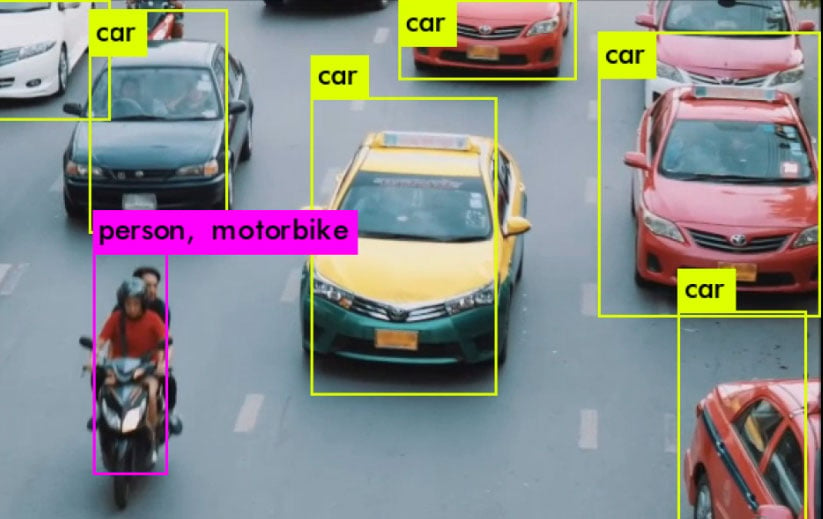

FPGA 與 CPU 配合使用,是異構計算方法的一部分。對於某些工作負載,FPGA 提供了比 CPU 顯著的加速,在這種情況下,機器學習推理的速度提高了 50 倍。

應用定製靈活性

FPGA 具有一系列工具,可針對應用進行最佳定製。硬體結構適應僅使用所需的內容,包括在需要時使用強化浮點塊。對於BWNN的權重,我們只使用了一個比特,加上平均比例因數,仍然達到了可接受的精度,但節省了大量資源。

能源效率

每瓦功率不僅在邊緣很重要,而且在數據中心的空間和電力成本方面的功率預算中也很重要。FPGA 可以獨特地提供最新的高效庫,但每瓦功耗遠低於 CPU。

基於軟體的開發

借助BittWare獨家優化的 OpenCL BSP,您可以利用面向軟體的開發人員和最新的軟體庫。這使我們能夠快速調整 YOLOv3 框架,該框架比舊的 ML 庫提高了性能。

深入瞭解高性能計算

Read the 2D FFT White Paper

瞭解 HBM2 如何使用我們的 520N-MX 卡説明加速 2D FFT 應用

Read the 2D FFT White Paper

點擊這裡

Read the BWNN White Paper

Learn how we used OpenCL to adapt the YOLOv3 machine learning framework to one of our FPGA cards

Read the BWNN White Paper

點擊這裡應用

當處理存儲的需求 超過 具有 CPU 的傳統架構時,我們針對應用程式。

人工智慧/機器學習推理

科學類比

圖像/視頻處理

粒子物理建模

基因測序

分子動力學

何時將 FPGA 用於高性能計算

FPGA 允許客戶建立具有以下特性的特定於應用的硬體實現:

- 高度並行的實現

- 對緩存不友好的記憶體訪問模式

- CPU 或 GPU 中本機不支援的數據類型

- 低延遲或確定性操作

- 需要連接到外部 I/O

兩個客戶在HPC中使用BittWare卡

流覽我們的計算加速產品

購買與 TeraBox 預先整合的卡

有問題嗎?

從我們的技術人員那裡獲取您的 HPC 問題的答案。

“*”表示必填欄位