nxFramework

Low-Latency Development Framework

The Exegy (Enyx) Development Framework (nxFramework) is a hardware and software development environment designed to efficiently build and maintain ultra-low latency FPGA applications for the financial industry. Based on 10 years of research and development, nxFramework is the foundation for all Enyx off-the-shelf solutions and provides clients with the toolchain to manage a large portfolio of applications.

Developed for building in-house high performance trading engines, order execution systems, pre-trade risk check gateways, and custom projects — any skilled FPGA developer starting a new low latency project, maintaining an existing one, or looking to change platforms can immediately reduce their time-to-production with nxFramework.

10G MAC/PC@

29奈秒RTT

10G TCP @

53奈秒RTT

圖書館

60 多個實用核心

特徵

Ultra-low latency connectivity cores

- 10G MAC/PCS – 29ns RTT – SOP to SOF @ 322MHz

- 40G MAC/PCS – 55ns RTT – SOP to SOF @ 322MHz

- 10G TCP stack – 53ns RTT @ 322MHz

- 10G UDP stack – 43ns RTT @ 322MHz

- PCIe streaming DMA – 790ns RTT @ 250MHz

Library of 60+ utility cores

- MMIO core library

- Packet streaming core library

- Memory management core library

- Math core library

- Statistics core library

- Simulation helpers library

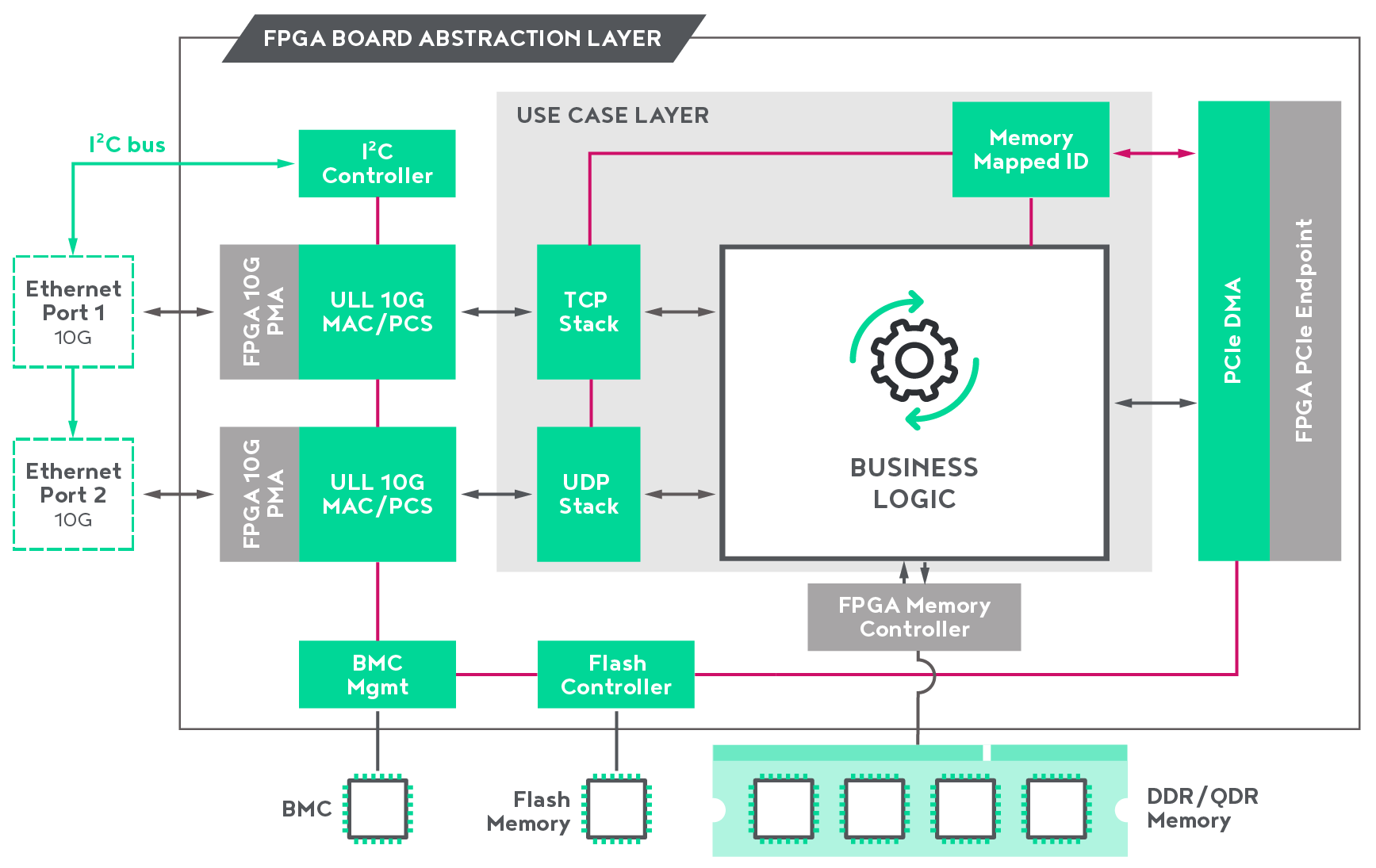

nxFramework Overview

NVMe Bridge Platform IP Core Facts

Provided with Core

- Documentation: comprehensive user documentation

- Design file formats: Encrypted Verilog

- Constraints files: Provided per FPGA

- Verification: ModelSim verification model

- Instantiation templates: Verilog (VHDL wrappers available)

- Reference designs and application notes: Synthesis and place and route scripts

- Additional items: Reference design

Simulation tool used:

QuestaSim (contact IntelliProp for latest versions supported)

Support:

Phone and email support will be provided for fully licensed cores for a period of 6 months from the delivery date.

Notes:

Other simulators are available. Please contact IntelliProp for more information.

框圖、數據表和產品詳細資訊

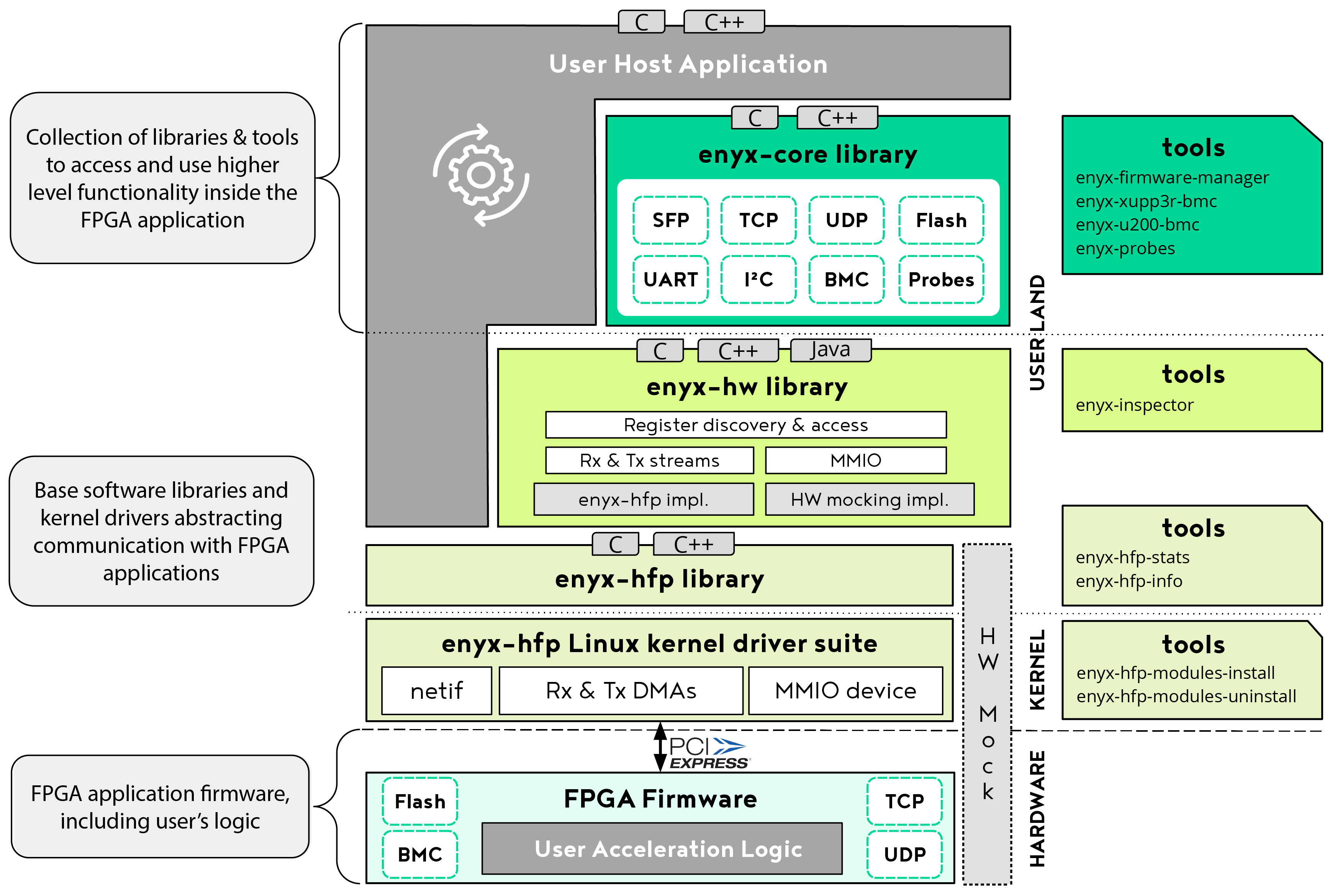

Enyx Runtime Software Stack

Enyx Runtime Software Stack

Enables simple configuration and monitoring of Enyx connectivity & utility cores, including interaction with the FPGA application via our C/C++ libraries.

空標題

Empty hea

Hardware Development Environment

A Python scripted development environment that enables users to simplify their development cycle and accelerate their time-to-production.

空標題

Empty head

The Enyx Inspector: Efficient Debugging

Equipped with a web-based GUI that can configure and monitor the FPGA at runtime, allowing for quick deployment and debug.

空標題

Empty head

Detailed Feature List

- All available Enyx connectivity and utility cores

- Board management cores:

- Flash controller support for FPGA bitstreams

- I²C bus controller for SFP/QSFP communication

- Configurable instantiation of memory controllers (DDR4, QDR II+)

- Additional elements included:

- The Enyx Inspector: a web-based debugging tool

- Linux drivers & configuration/communication libraries

- Off-the-shelf, configurable reference designs

- Support for widely used FPGA families in the financial sector

Reference Examples/Use cases

ULL Tick-to-trade platform

- Standard reference design for ULL tick-to-trade FPGA trading strategies

- nxFramework provides all the required hardware & software modules to assist with development

- Sub 100 ns RTT latency

Pre-trade Risk Check Gateway

- Standard reference design for risk checks gateway acceleration

- Two distinct TCP stacks connect respectively to the users and to the exchange

- Sub 1 µs RTT latency

相容的 FPGA 卡

對定價或更多資訊感興趣?

我們的技術銷售團隊隨時準備提供可用性和配置資訊,或回答您的技術問題。

“*”表示必填欄位