ホワイトペーパー

バイナリ重み付けニューラルネットワーク推論のFPGAアクセラレーション

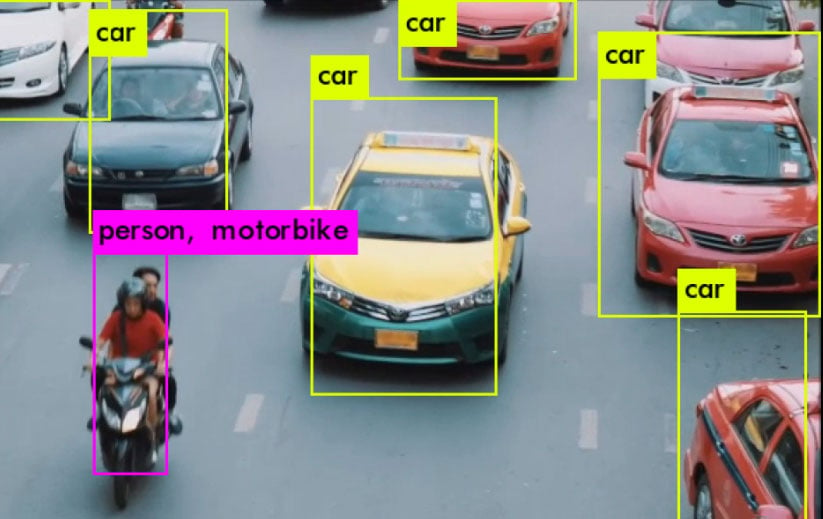

YOLOv3の特徴のひとつに、1枚の画像で複数の物体を認識することがあります。このネットワークを採用したのは、より複雑で高度なアプローチであり、限られたエッジ環境での適応能力が問われるからです。

今日のFPGAは、データセンターとエッジの両方の環境において急速に需要が高まっています。これは、性能の向上、より簡単な FPGA 開発ツールの使用、特定のアプリケーションに合わせてハードウェアアクセラレーション を調整する柔軟性へのニーズの高まりが原因です。FPGAアクセラレータ・ソリューションは、CPUと並行して動作することが多く、エンドユーザーの要件に合わせた柔軟なアプリケーション性能に焦点を当てた、異種混合コンピューティング・アプローチの一部となっています。

このホワイトペーパーでは、そのようなアプリケーションについて説明します。最近の機械学習ベースの画像認識システム(YOLOv3)を、IntelStratix 10 FPGA を搭載したBittWare 520N アクセラレーターボードに OpenCL で適用した交通監視を例にしています。FPGAの主要な推進力として言及された3つの側面、すなわち、CPUに対する性能、HDLの代わりにOpenCLを使用した開発の容易さ、最小限の電力/リソースを使用するためにアプリケーション(ここでは1ビットバイナリ重みを含む可変計算精度)を調整する柔軟性を検証する。

機械学習への需要の高まり

ほんの10年前まで、人工知能はほとんど学界や研究機関、SFの世界にしか存在していませんでした。しかし、近年、機械学習(Machine Learning: ML)の技術が、現実のアプリケーションの問題を解決するために、実用的かつ経済的に大規模に適用できることが明らかになり、市場関係者の活気あるエコシステムが生まれました。

しかし、機械学習は、データセットのトレーニング段階と、未知の入力を推論された出力に変換する「ランタイム」と呼ばれる段階の両方で、問題を解決するための非常に計算量の多いアプローチであるという現実を、機械学習のブレークスルーのニュースはまだ考慮する必要がある。機械学習アプリケーションのトレーニング段階は、データセンターで数時間から数日にわたる制約のない時間に一度だけ行われればよいのですが、ライブの推論は、システムのエッジで制約のあるハードウェアプラットフォームを使って、ほんの一瞬で行われなければならないことがよくあります。

本ホワイトペーパーのPDF版

機械学習の普及が進むためには、アプリケーションのニーズに合わせて最新の機械学習ライブラリをハードウェアに迅速に実装できる推論ソリューションが開発される必要があります。

フレキシブルFPGA

機械学習の推論に必要なシリコン数(つまり電力)を削減するアプローチの1つに、演算のダイナミックレンジを小さくすることがあります。例えば、32ビット浮動小数点演算から16ビット浮動小数点演算に変更しても、認識精度のアプリケーション性能はわずかに低下するだけで、ハードウェア要件を大幅に削減することができる。

さらに進化させたらどうでしょう。必要なビット数が 1 バイナリ・ビットまで減少すると、ハードウェア・ファブリックは必要なものだけを使用するように適応するため、FPGA が優れているのはこの部分です。また、必要に応じてStratix 10 FPGA のハード化された浮動小数点 DSP ロジック・ブロックを使用するなど、プロジェクト内で可変精度を使用することも可能です。FPGA では、ハードウェアをアプリケーションの要件に合わせて最適に調整するためのさまざまなツールを設計者が使用できます。

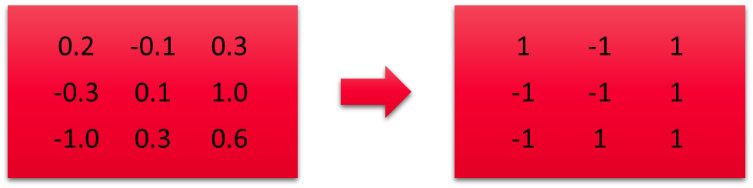

実際、私たちの研究では、2値化された重みだけを用いて機械学習を行うことに焦点を当てています:重みは、+1と-1の2値のみで2値化されます。画像ベースの機械学習アプリケーションの多くは、畳み込みニューラルネットワーク(CNN)と総称される一連の畳み込み演算を使用しますが、この新しいCNNの変種は、より具体的にはバイナリ重み付けニューラルネットワーク(BWNN)と呼ばれています。BWNNは、畳み込み層と完全接続層におけるすべての固定小数点乗算演算を、整数の加算演算に変換します。

著者について

Richard Chamberlainは、BittWare のシステムアーキテクトです。Richardは、FPGAの高水準プログラミングに関する豊富な経験を持ち、OpenCL開発プロジェクトを担当しています。また、新規設計や、CPUやGPUなど他のシステムタイプに基づいた設計に最適なハードウェアと開発アプローチについて、定期的に顧客にアドバイスを行っています。

空の見出し

この研究のもう一つの重要な要素は、520NのOpenCLサポートを利用して、ハードウェア開発プロセスをソフトウェアのようなツールフローに抽象化したことです。これにより、最新のアプリケーション・ライブラリをハードウェアのベースとして使用することができます。アクセラレーション-従来のHDL手法を使用して特定のデバイスとMLライブラリをターゲットにするのにかかる数ヶ月またはそれ以上の時間を短縮します(その間、より高性能な新しいMLライブラリがリリースされる可能性があります)。例えば、このホワイトペーパーは、OPERAプロジェクトのために、BittWare Arria 10ベースのボード、385A-SoCで行った作業に由来しています。私たちの開発チームは、OpenCL コードをこのデバイスからStratix 10 のはるかに大規模で高速なファブリックに迅速に移行しました。

可変精度、浮動小数点のDSP化、OpenCLによる開発など、アプリケーションに合わせたハードウェアソリューションでありながら、ソフトウェアのような開発速度を実現しています。

バイナリーニューラルネットワーク

CNNネットワークで畳み込みを処理するには、何百万もの係数を保存し処理する必要があります。従来、これらの係数は、それぞれ完全な単精度表現で保存されていました。研究者たちは、全体の精度を大きく変えることなく、必要なストレージ量とメモリ帯域幅を削減しながら、係数を半精度まで削減できることを実証しています。現在入手可能な事前学習済みのCNNモデルのほとんどは、半精度化された係数を使用しています。

しかし、これらの係数のトレーニングに別のアプローチを用いることで、ビット精度を1ビットとスケーリングファクター(ref)にまで低減することができる。浮動小数点係数のトレーニングでは、値がすべての入力係数の平均値より大きいか小さいかを表す2値化値に変換されます。これは2進数表記で1,0のどちらかで表されます(図1)。そして、コンボリューションの出力に平均値を乗じる。

図1:重みを2値化する(平均値=0.12)

FPGAの最適化

まず、重みを2値化することで、外部メモリの帯域幅とストレージの必要量を32分の1に削減することができます。FPGAファブリックは、各内部メモリブロックが1~32ビットの範囲のポート幅を持つように構成できるため、この2値化を利用することができます。したがって、重みを保存するための内部FPGAリソースが大幅に削減され、タスクの並列化のためのスペースが確保されます。

また、ネットワークの2値化により、CNNの畳み込みは入力の活性化の一連の加算または減算として表現することができる。ウェイトが2値0の場合、入力は結果から減算され、ウェイトが2値1の場合、結果に加算される。FPGA の各ロジック エレメントには、事実上あらゆるビット長の整数加算を効率的に実行できるキャリー チェーン ロジックが追加されています。これらのコンポーネントを効率的に使用することで、1つのFPGAで数万回の並列加算を実行することができます。そのためには、浮動小数点入力の活性化を固定精度に変換する必要があります。FPGAファブリックの柔軟性を利用すれば、CNNの要求に合わせて固定加算で使用するビット数を調整することが可能です。さまざまなCNNの活性化のダイナミックレンジを分析した結果、浮動小数点等価設計の1%以内の精度を維持するには、ほんの一握りのビット(通常は8ビット)が必要であることがわかりました。より高い精度を得るためには、ビット数を増やすことができます。

BNNのアプリケーションとして調査可能なネットワークは数多くあり、AlexNetのような多くのシンプルなネットワークの中から1つを選びたくなる。しかし、BWNN処理におけるFPGAの有効性を本当に理解するためには、YOLOv3のような最先端のネットワークを使用するのがよいでしょう。これは、多くの畳み込み層を持つ大規模な畳み込みネットワークである。

YOLOv3は深いネットワークであり、固定小数点丸めによって生じる誤差は、AlexNetのような小さなネットワークよりも、加算ごとに多くのビットを必要とします。FPGA技術の利点は、必要なビット数を正確に変更できることです。私たちのデザインでは、レイヤー間で転送されるデータを表現するために16ビットを使用しました。

コンボリューションを固定小数点に変換し、2値化による乗算の必要性をなくすことで、FPGA内で必要なロジックリソースが劇的に削減されます。これにより、単精度や半精度の実装と比較して、同じFPGAで大幅に多くの処理を実行したり、FPGAロジックを他の処理に解放することが可能になります。

ターゲット・ネットワーク・トレーニング

YOLOv3ネットワークは、106層からなる大規模な畳み込みネットワークで、オブジェクトを識別するだけでなく、そのオブジェクトの周囲にバウンディングボックスを配置します。オブジェクトの追跡が必要なアプリケーションで特に有効です。

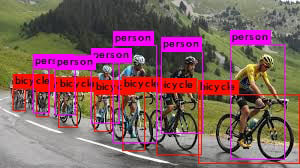

バイナリ重み付けネットワークは、適切に訓練された場合、YOLOv3ネットワークの精度をわずかに低下させるだけである。次の表は、再トレーニングしたYOLOv3ネットワークで得られた結果を示しています。

この画像の平均的な信頼度は、自転車の場合は76%、人の場合は82%でした。同じ画像で浮動小数点を使用した場合、自転車の平均信頼度は92%(16%向上)、人の平均信頼度は88%(6%向上)であることを比較してみてください。

FPGAで最高のパフォーマンスを発揮するためには、FPGAに最適なネットワーク機能をターゲットにすることが有効です。この場合、ネットワークは2値の重みで学習されるだけでなく、FPGAロジックに効率的にマッピングされる適切な活性化タイプが選択されました。

空の見出し

Designing forStratix 10

OpenCL は、CPU、GPGPU、FPGA の並列性を表現するために使用される一般的な言語です。ここでは、Intel FPGA OpenCLコンパイラを使用して、IntelStratix 10デバイスをターゲットとするアクセラレータをプログラミングしています。このホワイトペーパーのターゲットFPGAアクセラレータは、BittWare 520Nボードです。

FPGA デザインの性能は、以下のような多くの要因に左右されます(ただし、これらに限定されません):

- デバイスのスピードグレード

- デザインにおける組合せ論理の深さ

- デザインのファンアウト(多点間で共有される信号の数)

- 端末の過剰投入によるルーティングの輻輳化

- グローバルメモリ帯域幅

Stratix 10デバイスは非常に大きく、以前のデバイスよりもこれらの問題の影響を受けやすくなっています。以下の段落では、これらの問題のいくつかをより詳細に説明します。

図2:BittWare 520N FPGAアクセラレータボード

コンビナトリアルロジックの深さ:Intel OpenCLツールは、可能な限り自動的にデザインをパイプライン化し、Stratix 10上で可能な限り最高のパフォーマンスを達成するために必要なレジスタリングを挿入します。しかし、デザインにフィードバックがある場合、レジストレーションは常に可能とは限りません。これは通常、自己依存性を持つ複雑なインデキシング要件を作成する際に発生します。したがって、可能な限り、このようなパイプラインの依存関係を避けるようにコードを構成する必要があります。そうしないと、デザインのクロック周波数がこれらのパスによって支配されてしまいます。

ファンアウト:ファンアウトとは、ソースは1つであるがエンドポイントが複数ある信号のことである。デバイスで使用できるネットの数は限られているため、ルーティングツールにとって問題となることがあります。このような経路が混雑すると、信号の一部が混雑箇所を通過することになり、経路が長くなり、最終的にクロック周波数が遅くなる。ファンアウトは、デザインの複数の部分で変数を共有することの影響をコーディング時に認識することで削減することができます。

オーバーポピュレーション:しかし、デバイスの人口が多くなると、デザインのクロック周波数が低下し始めるポイントがあります。これは、FPGAの周囲で経路を探そうとする多数の信号による配線混雑が原因です。大規模なデザインで高いクロック周波数を実現するには、パイプラインを多用し、ファンアウトを大きくしないようにする必要があります。

メモリ帯域幅: FPGAのローカルメモリに十分なデータを保存できるとは限らず、データは深い外部メモリから書き込んだり読み込んだりする必要があります。S10デバイスのサイズを考えると、この帯域幅は、すべてのニューラルネットワーク層にデータを供給し続けるには十分ではありません。幸いなことに、CNNコードは多くのデータの再利用が可能です。この問題は,BittWareの 520N-MX ボードで使用されているような,HBM2 バージョンのStratix 10 を使用することで多少軽減することができる.

結局のところ、ほとんどの設計は上記の妥協点であり、ここで説明するBNN設計も例外ではありません。

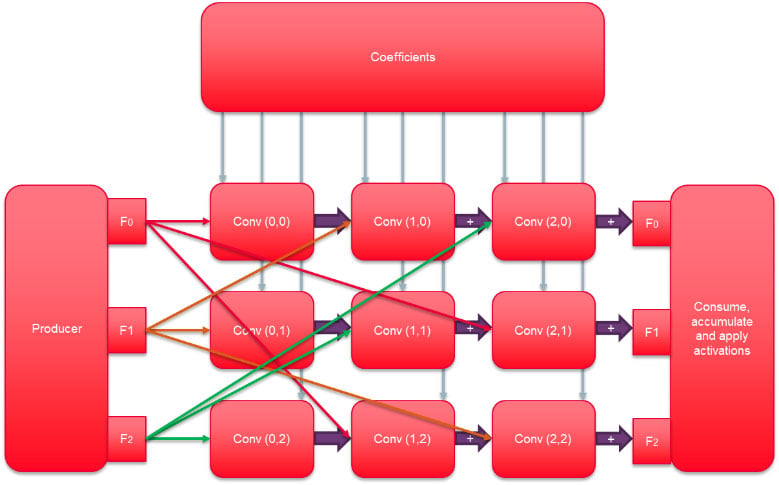

図3は、この設計の主要な処理要素であるコンボリューションパスを示しています。データは可能な限りパイプライン化され、3つの累積パスに分かれています。各コンボリューションブロックは、32×32のバイナリ重みコンボリューションブロックを実行し、32の各入力は32の全出力で共有されます。このため、ファンアウトは大きくなりますが、外部メモリの帯域幅への負担は軽減されます。96×96のコンボリューションを32×32の複数のブロックに分割することで、ファンアウトの配線は各ブロック内に限定され、デザイン全体のファンアウトを低減している。入力データはOpenCLパイプを介して各畳み込みブロックに渡され、必要に応じてコンパイラが追加のレジスタを挿入することができます。

図3に示す「producer」「consume」「coefficient」カーネルは、グローバルメモリから異なるコンボリューションブロックにデータを渡します。また、コンシューマーブロックは、出力に対して浮動小数点活性化関数を実行する。

表1は、各32×32コンボリューションを表す1024個の16ビットアキュムレーションを実行するために必要なリソースを示しています。

16ビットデータを使用する場合でも、すべての入出力特徴データを格納するために必要なストレージは、FPGAデバイスで使用可能な容量を超えます。そのため、グローバルメモリからローカルFPGAメモリに一括してデータをコピーする必要があり、並列コンボリューションの数がグローバルメモリで対応できる範囲を超えると、最終的にパフォーマンスが低下する。

| ALM | レジスター | オプス |

|---|---|---|

| 35305 (2%) | 41601 (2%) | 2048 |

表1 : 32×32コンボリューションマトリックスのStratix 10リソース

| オジック(ALMs) | メガヘルツ | ピークTOPS | 高速化対 OpenMP 32スレッド (Xeon CPU D-1587 1.7 GHz) |

|---|---|---|---|

| 536,122 (57%) | 300 | 5.5 | 50x |

16ビットデータを使用する場合でも、すべての入出力特徴データを格納するために必要なストレージは、FPGAデバイスで使用可能な容量を超えます。そのため、グローバルメモリからローカルFPGAメモリに一括してデータをコピーする必要があり、並列コンボリューションの数がグローバルメモリで対応できる範囲を超えると、最終的にパフォーマンスが低下する。

表2は、最終的にコンパイルされたデザインの統計データを示しています。なお、Logicには、PCIeおよびグローバル・メモリ・インターフェースを介したホスト通信に必要なボード・サポート・パッケージ・リソースも含まれています。

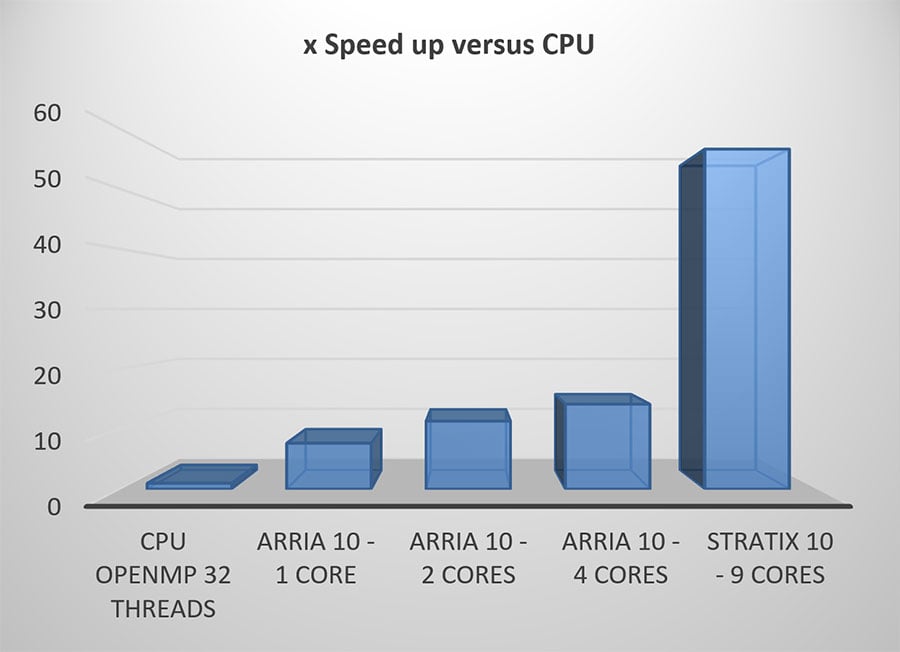

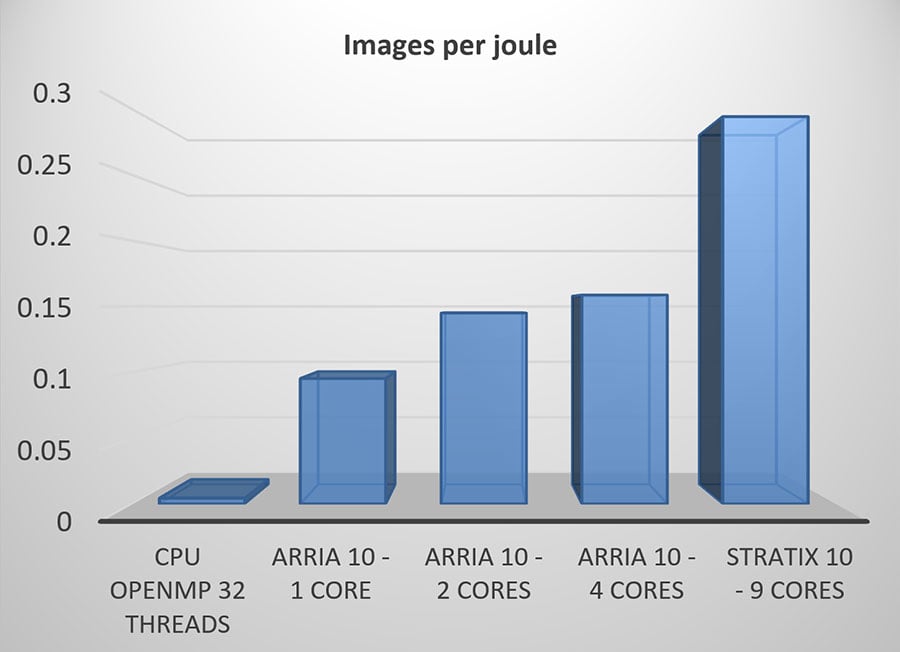

次の図は、Arria 10 と Xeon CPU の両方と比較した場合の速度と使用電力あたりの性能の比較を示しています。なお、Stratix 10 では、さらに多くのコアを利用することで、さらなるスピードアップが期待できます。

Stratix 10 MXのHBM2

新しいBittWare 520N-MX ボードは、IntelStratix 10 MX デバイスを搭載しています。このFPGAは、3D積層高帯域幅メモリ2(HBM2)を搭載し、32個のユーザーポートを備え、合計で最大512GB/秒のメモリ帯域幅を提供します。この帯域幅の拡大により、さまざまなアーキテクチャが可能になり、デザインにおける高いファンアウトを削減し、外部メモリ用の内部バッファリングの必要性を減らすことができるようになります。MXデバイスは、メモリ集約型アルゴリズムで複雑になりがちなメモリ調停ネットワークを簡素化し、これまで不可能だったCNNの帯域制限ソリューションを可能にすることで、より多くのユーザーロジックを処理用に解放するはずです。

結論

FPGA の柔軟性は、他のテクノロジーでは不可能ではないにせよ、個々のネットワークごとに CNN を最適化する機会を提供します。産業界がニューラルネットワークの利点を認識し始め、推論アプリケーションの数が増えるにつれて、異なるデータセット、精度、および電力に合わせたネットワークの要件も増えていくでしょう。

将来の幅広いアプリケーションを完全に実現するには、特にエッジでのコンピューティングにおいて、汎用的な API では完全に満たすことができないトポロジーが必然的に必要となります。BittWare'sの多種多様なFPGAソリューションとCNN FPGA最適化の専門知識を組み合わせることで、業界がCNN用FPGAの可能性を実現するのを支援するユニークな立場にある。