M2. Module

250-M2D

Xilinx® Kintex® UltraScale+™ FPGA on M.2 Accelerator Module

Obsolete Product Notice:

This is an obsolete product and is no longer available for purchase. Contact BittWare for a recommended newer product.

Overview

The BittWare 250-M2D is an FPGA-based Computational Storage Processor (CSP) designed to meet the draft M.2 Accelerator Module Hardware Specification standard*. It is intended to operate in Glacier Point carrier cards for Yosemite servers. These feature-rich, dense servers are favored by hyperscale and cloud companies striving to improve the performance density and energy-efficiency of machine learning platforms.

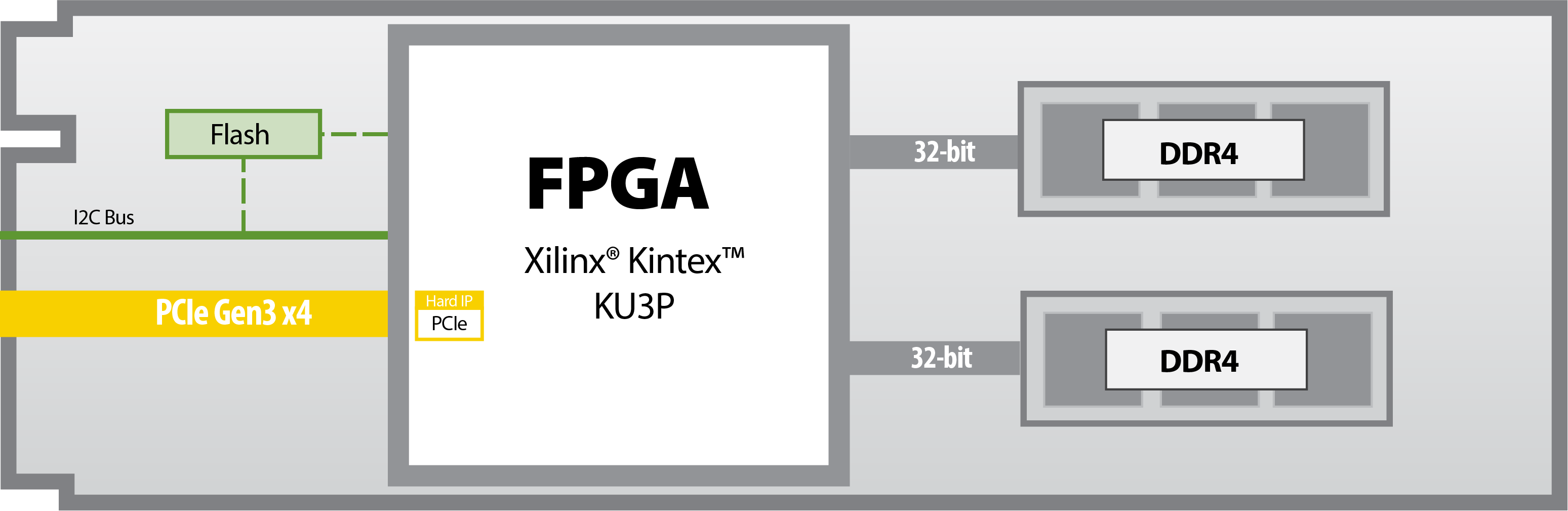

The 250-M2D product features a Xilinx Kintex® UltraScale+ FPGA directly coupled to two banks of local DDR4 memory. Customers can either develop their own acceleration applications in HDL, or take advantage of pre-programmed accelerator solutions featuring IP from BittWare partner companies.

Key Features

Ideal for Computational Storage

KU3P FPGA: 356K LCs Kintex UltraScale+

Up to 32 GBytes DDR4

Looking for a Compute and Storage solution?

The 250-M2D is available pre-configured with compute and storage IP from our solutions partners Myrtle.ai and Eideticom

Block Diagram, Data Sheet and Specifications

Specifications

FPGA

- Xilinx Kintex UltraScale+

- KU3P in an B784 package

- Core speed grade - 2

- Contact BittWare for additional FPGA option

On-board DDR4 SDRAM

- Two banks of DDR4 SDRAM x 32 bits

- 8GB bank (16GB version also available)

- Transfer Rate: up to 2400 MT/s

Host interface

- M.2 interface supporting Gen3 x4 PCIe

Cooling

- Passive heatsink

Electrical

- Hot swapping tolerant

- Power dissipation is application dependent

- TDP: 14.85W max

- Module Absolute Peak Power (20us): 24W

Environmental

- Operating temperature: 5°C to 50°C at module inlet

- Cooling: air convection

Quality

- Manufactured to IPC JSTD-001 -Class 2

- RoHS compliant

Form factor

-

- M.2 Accelerator Module Hardware Specification* (not designed for standard M.2)

Draft specification document: https://www.opencompute.org/wiki/Server/Working

Development Tools

FPGA development

- BIST - Built-In Self-Test for CentOS 7 provided with source code (pinout, gateware, PCIe driver and host test application)

Application development

- Xilinx Tools - Vivado Design Suite HLx Editions: HDL and C/C++ with HLS

PCIe carrier card

- PCIe carrier card allowing 250-M2D to be populated in a standard PCIe slot for lab development

Deliverables

- 250-M2D FPGA board

- Built-In Self-Test (BIST)

- Eideticom NoLoad pre-installed (optional)

- Myrtle.ai SEAL pre-installed (optional)

- 1-year access to online Developer Site

- 1-year hardware warranty

- Contact BittWare for extended warranty and support options

Interested in Pricing or More Information?

Our technical sales team is ready to provide availability and configuration information, or answer your technical questions.

"*" indicates required fields