White Paper

Introduction to BittWare's SmartNIC Shell for Network Packet Processing

Overview

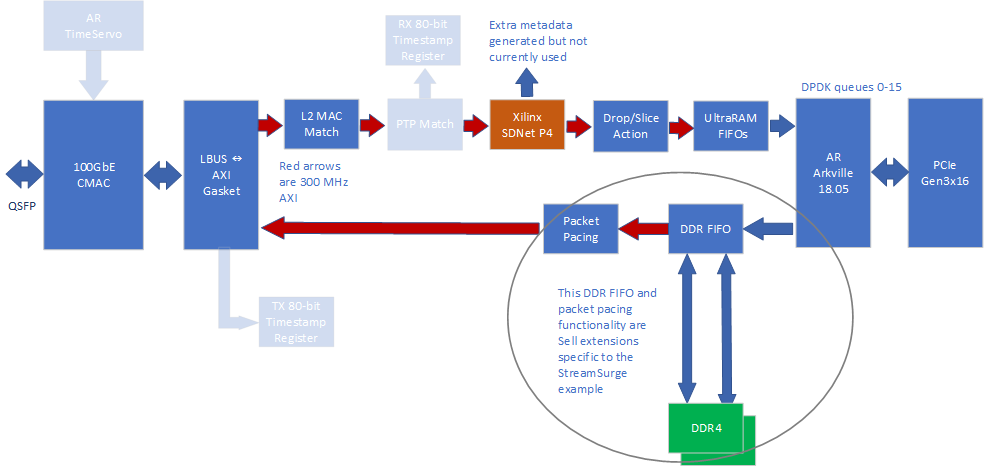

SmartNIC Shell is a complete working NIC that is implemented on a BittWare FPGA board as a starting point that users add FPGA value into. You can use SmartNIC Shell to quickly deploy network functions (NFV), network monitoring, specialized packet broker, or anything else that manipulates packets. The shell provides DPDK offload to interact with host applications; it is delivered as FPGA project source and as a fully functional bitstream.

About SmartNIC Shell

What is Included with SmartNIC Shell?

- Arkville™ DPDK/AXI aware Data Mover (Atomic Rules)

- PCIe Hard IP (Xilinx)

- 100G Ethernet Subsystem with AN/LT (Xilinx)

- Packet pacing (interframe gap) block (BittWare)

- UltraRam FIFO block (BittWare)

- Drop/slice block (BittWare)

- Lbus-to-AXI Core (BittWare)

- DDR4 FIFO (BittWare)

- L2 match/action filter (BittWare)

- HLS based Parser (BittWare)

- HLS based RSS (BittWare)

Supported Products

SmartNIC Shell supports the following BittWare products:

- XUPP3R: 3/4-length PCIe with a VU9P FPGA, speed grade 2, one of four QSFPs enabled.

Licensing

The Loopback’s FPGA bitstream contains several components. Each component has an AXI4-Stream interface on both input and output collectively used as a data plane. The bitstream’s control plane uses AXI4-Lite interfaces connected to the physical PCIe interface.

Design Flow

- BittWare licenses the Arkville™ DPDK and TimeServo™ cores from Atomic Rules and redistributes them. BittWare adds value above Arkville as part of BittWare’s SmartNIC Shell.

- A license for the “Xilinx 100G Ethernet Subsystem with AN/LT” must be available for the FPGA project to build.

- The FPGA project requires Vivado 2018.3

mpty heading

Empty heading

DPDK

How SmartNIC Shell Implements DPDK

DPDK is implemented in the FPGA on the BittWare card. BittWare’s joint effort with Atomic Rules is the first DPDK implementation inside an FPGA.

The BittWare board uses a patched version of the Atomic Rules PMD. The base PMD is included inside the DPDK distribution. BittWare supplies the necessary patches as part of our source distribution. All of BittWare’s testing with DPDK uses the uio_pci_generic driver, which replaces the BittWorks II driver. However, some of the BittWorks II tools still work.

Users receive the following:

- A “data mover” to put inside the FPGA, attached to an AXI bus on one side and the PCIe interface on the other. It is delivered using the Xilinx or Intel encrypted licensing scheme. That includes leveraging each company’s options to provide a time-limited evaluation

- An open source DPDK poll mode driver (PMD) to interface DPDK to the data mover above. This PMD became part of the official DPDK release starting with DPDK 17.05 under the name “Arkville”

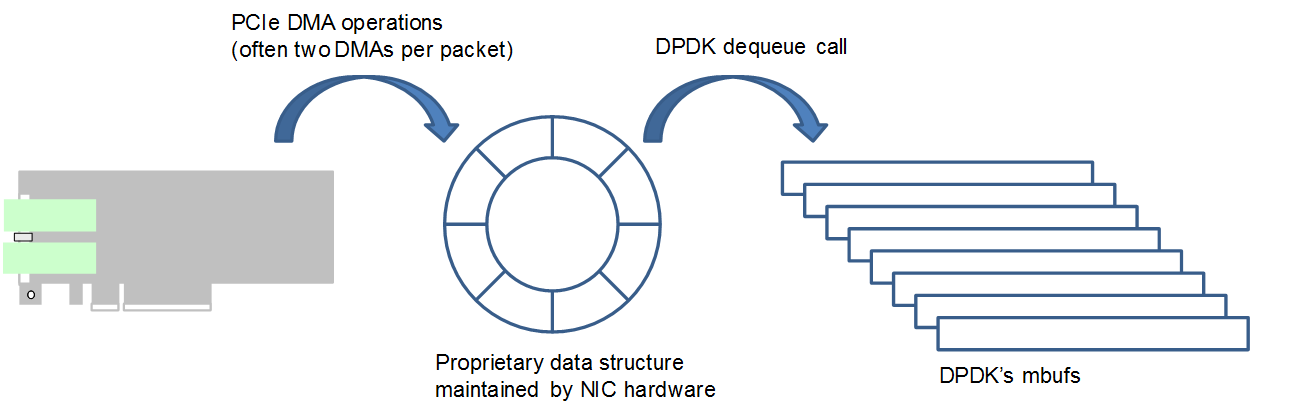

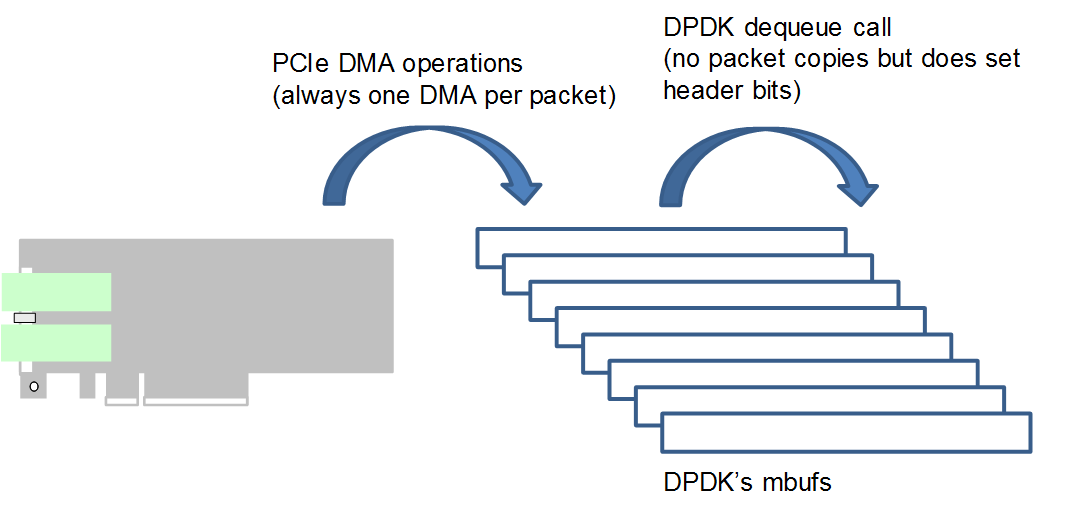

Most ASIC and FPGA DPDK implementations perform one copy:

In contrast, SmartNIC Shell’s DPDK IP Core always DMAs directly into DPDK mbufs, never requiring the CPU to copy packet data. No second DMA is needed for metadata, reducing CPU overhead, latency, and host memory requirements. This does eliminate the opportunity for some PCIe optimizations like coalescing small packets into fewer DMAs or writing data preformatted as PCAP records. If needed, your application code can do those things in the FPGA above the DPDK core.

There's More to Read: Get the SmartNIC Shell App Note

Request PDF Download

What you see on this page is the introduction to BittWare’s SmartNIC Shell. There’s a lot more detail in the full App Note! Fill in the form to request access to a PDF version of the full App Note.

"*" indicates required fields