PCIe FPGA Card

A10PL4

Arria 10 FPGA Low-Profile PCIe Card

Dual QSFP28 and DDR4

Obsolete Product Notice:

This is an obsolete product and is no longer available for purchase. Contact BittWare for a recommended newer product.

Need a Price Quote?

Overview

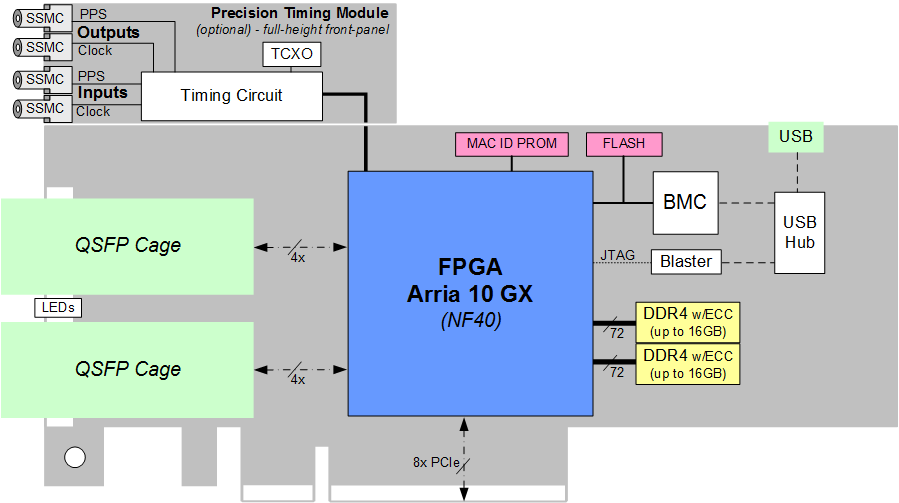

BittWare’s A10PL4 is a low-profile PCIe x8 card based on the Intel Arria 10 GX FPGA. The Arria 10 boasts high densities and a power-efficient FPGA fabric married with a rich feature set including high-speed transceivers, hard floating-point DSP blocks, and embedded Gen3 PCIe x8. The board offers over 32 GB of memory, sophisticated clocking and timing options, and two front panel QSFP cages, each supporting 40 Gbps.

The A10PL4 also incorporates a Board Management Controller (BMC) for advanced system monitoring, which greatly simplifies platform management. All of these features combine to make the A10PL4 ideal for a wide range of applications, including network processing and security, compute and storage, instrumentation, broadcast, and SigInt.

Key Features

Intel Arria 10 GX 1150

2x QSFP28 for 10/40 Gbps

Precision Timing Options

Precision Clocking and Timing

The A10PL4 is available with an optional add-on module that provides precision timestamping capabilities. Contact your BittWare Sales representative to learn more.

Video

Learn how FPGAs accelerate workloads like database find/replace.

Block Diagram, Data Sheet and Specifications

Want More Details?

Request the Hardware Reference Guide (HRG)

The HRG gives you much more detail about the card such as block diagrams, tables and descriptions.

Specifications

FPGA

- Altera® Arria® 10 GX FPGA

- High-performance, multi-gigabit SerDes transceivers @ up to 17 Gbps

- Up to 1150K logic elements available

- Up to 53 Mb of embedded memory

- 1.6 Gbps LVDS performance

- Up to 3,300 18x19 variable-precision multipliers

On-Board Memory

- Two banks DDR4 with ECC, up to 16 GBytes (x72) each

- 64 MBytes of Flash memory for booting FPGA

PCIe Interface

- x8 Gen1, Gen2, Gen3 direct to FPGA

USB Header

- USB 2.0 interface for debug and programming FPGA and Flash

- Built-in Altera USB-Blaster

Precision Timing Module(Optional)

- 1 PPS input and output

- Reference clock input and output

- Adjustable TCXO

QSFP Cages

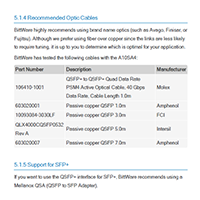

- 2 QSFP28 (zQSFP) cages on front panel connected directly to FPGA via 8 SerDes (no external PHY)

- Each supports 40GbE or 4 10GbE

- Backward compatible with QSFP and can be optionally adapted for use as SFP+

Board Management Controller

- Voltage, current, temperature monitoring

- Power sequencing and reset

- Field upgrades

- FPGA configuration and control

- Clock configuration

- I2C bus access

- USB 2.0 and JTAG access

- Voltage overrides

Size

- Low profile (Half-height, half-length) PCIe slot card; x8 mechanical

- 168mm x 68.9mm

- Max. component height: 14.47mm

Development Tools

System Development

- BittWorks II Toolkit - host, command, and debug tools for BittWare hardware; Matlab API; source code porting kit also available

FPGA HDL Development

- FPGA DevKit

- Physical interface components

- Board, I/O, and timing constraints

- Example Quartus projects

- Software components and drivers

- Altera Tools

- Quartus II software

OpenCL Development

- OpenCL Developer’s Bundle - BittWorks II Toolkit, Board Support Packages, Altera SDK for OpenCL, Altera Quartus II

Order Your Cards in a TeraBox™ FPGA Server

Get extended warranty support and save time with a pre-integrated solution!

Ready to Buy?

This product is available for quick online ordering from Mouser Electronics. Check stock at Mouser’s website:

Interested in Pricing or More Information?

Our technical sales team is ready to provide availability and configuration information, or answer your technical questions.

"*" indicates required fields