PCIe FPGA Card

250-U2

UltraScale+ on U.2 Form Factor

Fully programmable FPGA processor for NVMe acceleration

Legacy Product Notice:

This is a legacy product and is not recommended for new designs. It is still available for purchase, but development tools and software are no longer maintained for compatibility with the latest FPGA tools and operating systems. Minimum order quantities (MOQs) may apply. Contact BittWare for details.

Need a Price Quote?

Overview

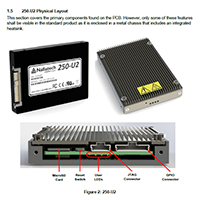

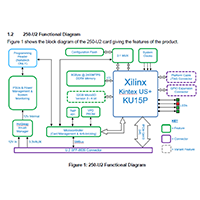

BittWare’s 250-U2 is a Computational Storage Processor conforming to the U.2 form factor. It features an AMD Kintex UltraScale+ FPGA directly coupled to local DDR4 memory. This energy-efficient, flexible compute node is intended to be deployed within conventional U.2 NVMe storage arrays (approximately 1:8 ratio) allowing FPGA-accelerated instances of:

- Erasure Coding and Deduplication

- Compression, Encryption & Hashing

- String/Image Search and Database Sort/ Join/Filter

- Machine Learning Inference

The 250-U2 can be wholly programmed by customers developing in-house capabilities or delivered as a ready-to-run pre-configured solution featuring Eideticom’s NoLoad® IP. The 250-U2 is front-serviceable in a 1U chassis and can be mixed in with storage units in the same server, allowing users to mix-and-match storage and acceleration.

Key Features

Ideal for U.2 NVMe storage arrays

Up to 16 GBytes DDR4

KU15P Kintex UltraScale+ FPGA: 1.1 million LCs

Block Diagram, Data Sheet and Specifications

Want More Details?

Request the Hardware Reference Guide (HRG)

The HRG gives you much more detail about the card such as block diagrams, tables and descriptions.

Specifications

FPGA

- AMD Kintex UltraScale+

- KU15P in an FFVA1156 package

- Core speed grade - 2

- Contact BittWare for KU11P FPGA option

On-board DDR4 SDRAM

- One bank of DDR4 SDRAM x 72 bits

- 8GB bank (16GB version also available)

- Transfer Rate: 2400 MT/s

Host interface

- U.2 Connector

- Compliant to SFF-8639

Datacenter deployment

- On-board NVMe compliant SMBUs controller (Spec. 1.0a)

- Field flash update via software or SMBus

- SMBus FPGA flash control: anti-bricking, fallback, and multiboot

- SMBus access to unique board data and temperature sensor

Back panel features

- User LEDs accessible

- Reset switch to restore factory settings

Development features (behind back panel)

- JTAG connector for access to the FPGA, flash, and debug tools

- GPIO connector

- MicroSD connector

Power supply monitoring & reporting

- Voltage monitoring

- Temperature monitoring

- Fault condition reporting to FPGA

Cooling

- U.2 drive case optimized for cooling with passive heatsink

Electrical

- Hot swapping tolerant

- On-card power derived from U.2 supplies

- Power dissipation is application dependent

- Typical FPGA power consumption ~20W

- Card designed to deliver up to 25W power consumption

Environmental

- Operating temperature: 5°C to 35°C

- Cooling: air convection

Form factor

- U.2 compliant 2.5” Drive Form Factor

- Height: 15mm

Development Tools

FPGA development

- BIST - Built-In Self-Test for CentOS 7 provided with source code (pinout, gateware, PCIe driver and host test application)

Application development

- AMD Tools - Vivado Design Suite HLx Editions: HDL and C/C++ with HLS

Deliverables

- 250-U2 FPGA board

- Built-In Self-Test (BIST)

- Eideticom NoLoad pre-installed (optional)

- 1-year access to online Developer Site

- 1-year hardware warranty

- Contact BittWare for extended warranty and support options

r4 v0

Order Your Cards in a TeraBox™ FPGA Server

Get extended warranty support and save time with a pre-integrated solution!

Ready to Buy?

Product availability for online ordering from Mouser Electronics:

Interested in Pricing or More Information?

Our technical sales team is ready to provide availability and configuration information, or answer your technical questions.

"*" indicates required fields