oneAPIにおけるFPGAリソースの効率的な共有化

FPGAのリソース共有を解決するバタフライクロスバースイッチの構築

シェアードリソース 問題点

FPGAカードは通常、高性能なメモリやI/Oインターフェースを多数搭載しています。

- キャッシュを内蔵していない

- ハードコードによる調停ロジックがない

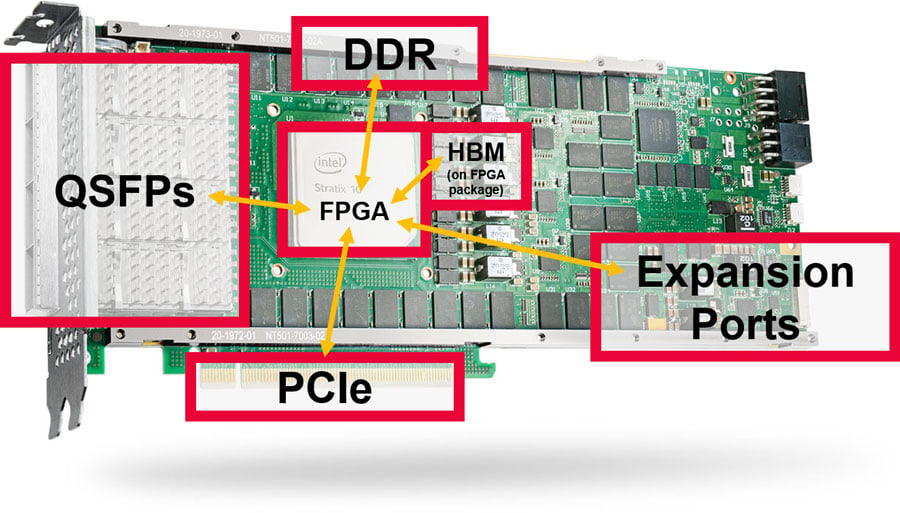

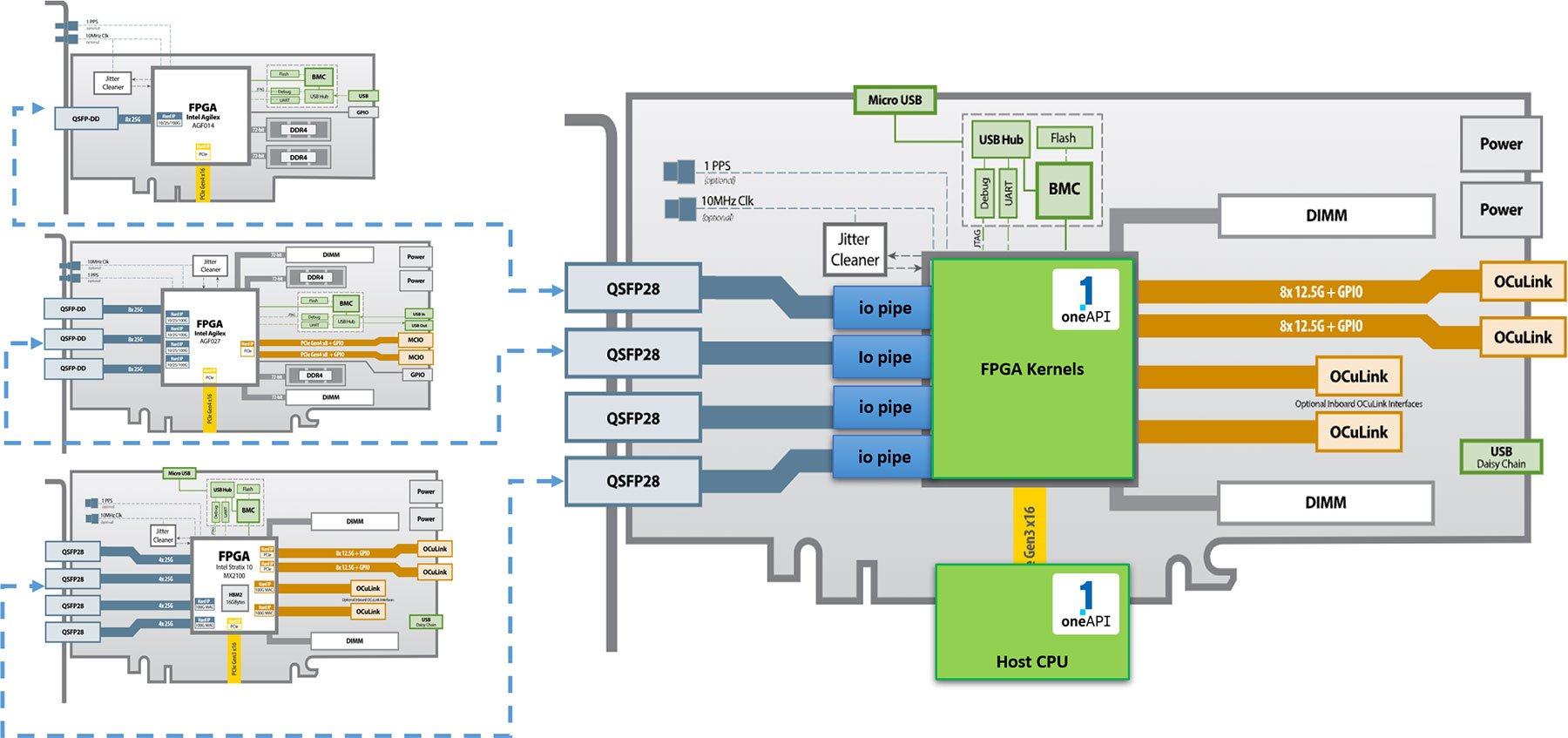

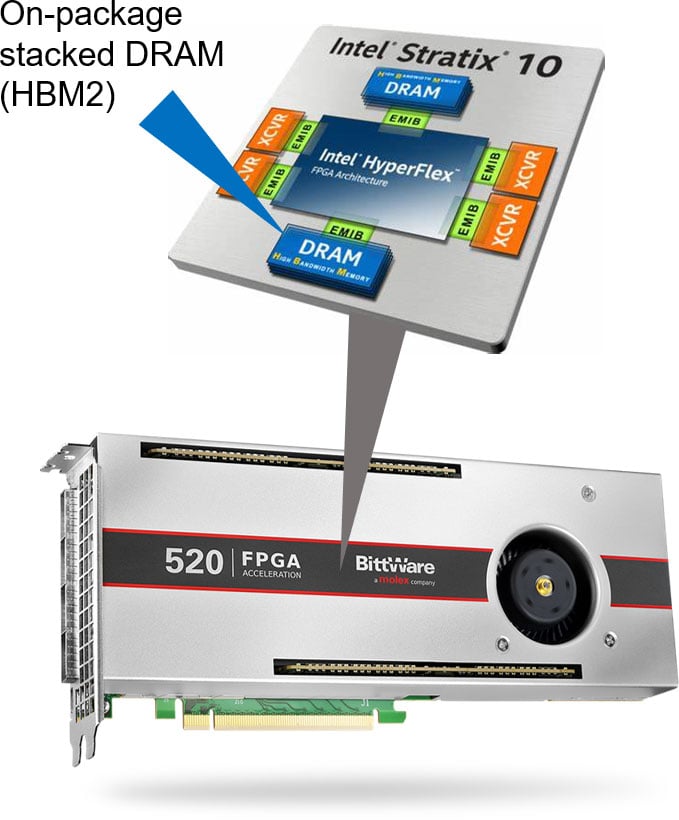

インテルの Stratx 10 やAgilex シリーズなどの大型 FPGA は、豊富な I/O インターフェイスを備えています。BittWare は、QSFP、PCIe、オンカード DDR4 および GDDR6 メモリ、拡張ポートなどの機能を提供し、これらを活用するカードを提供します。また、オンパッケージのHBM2を搭載したFPGAを搭載したカードも用意しています。

特に、複数のカーネル間でリソースを共有する必要がある場合、これらすべてのインターフェイスにアクセスすることは簡単ではありません。FPGA には、基本的なメモリ コントローラーを超えるキャッシュや調停ロジックが内蔵されていないため、調停はユーザーの責任で行う必要があります。

共有資源問題に対する我々の解決策:

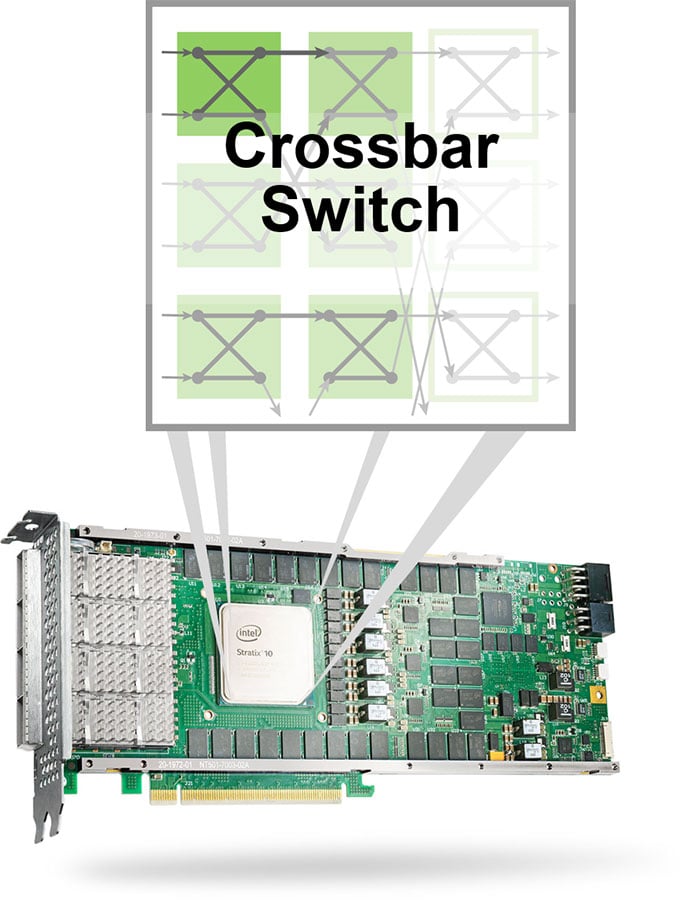

を作成します。 クロスバースイッチFPGAのロジックに

インテル® oneAPIを使ってバタフライ・クロスバー・スイッチを作りました。

- 低レベルのRTLではなく、高レベルのツールであるoneAPIを使用することで 設定しやすい解決策 オプティマイズしやすい用途に応じて

- をターゲットにしました。 520N-MXカードに使用することができます。このコードは、oneAPIを使用して他のBittWare カードに使用することができます。

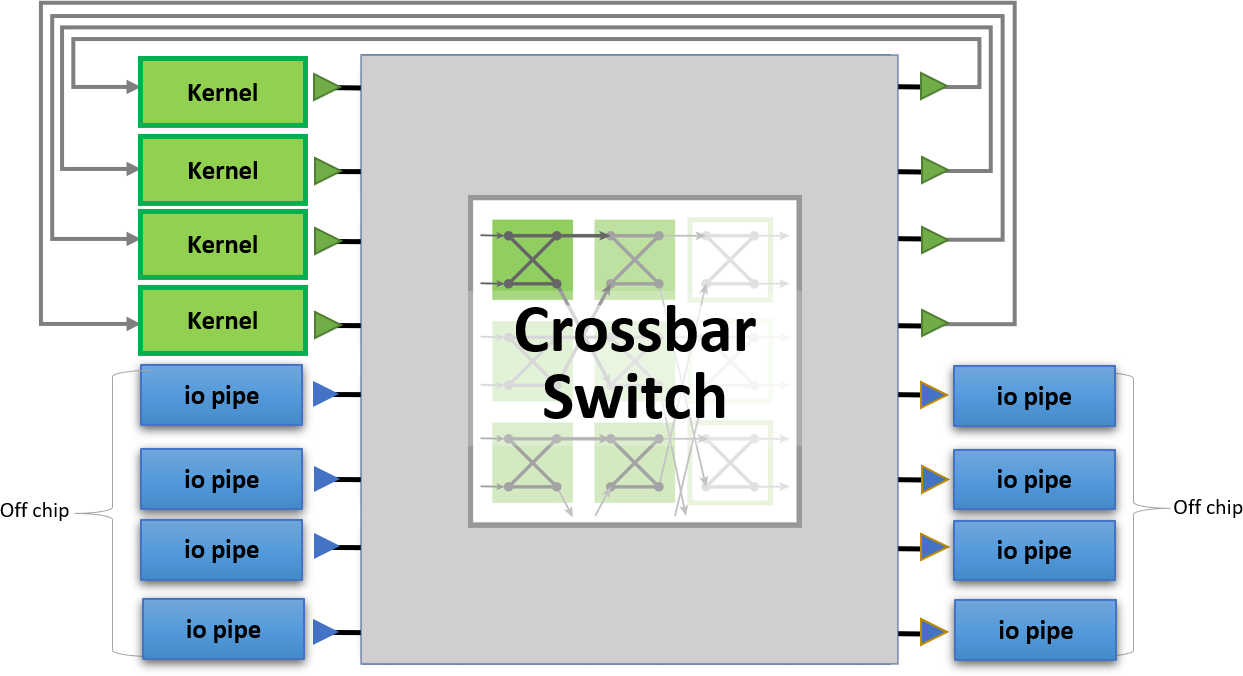

複数のカーネルや複数のインターフェース間で接続性を共有するためのソリューションの1つがクロスバー・スイッチです。これは、もちろんFPGAネイティブのプログラミングを使って作成することができます。しかし、oneAPIのような高水準のプログラミング言語を使えば、必要な接続数やインターフェースの幅に応じて、可能な限り効率的に最適化することが容易にできる。

BittWare バタフライ・クロスバー・スイッチは、HBM2メモリと複数のネットワークポートを搭載した当社の520N-MXカードで開発されました。

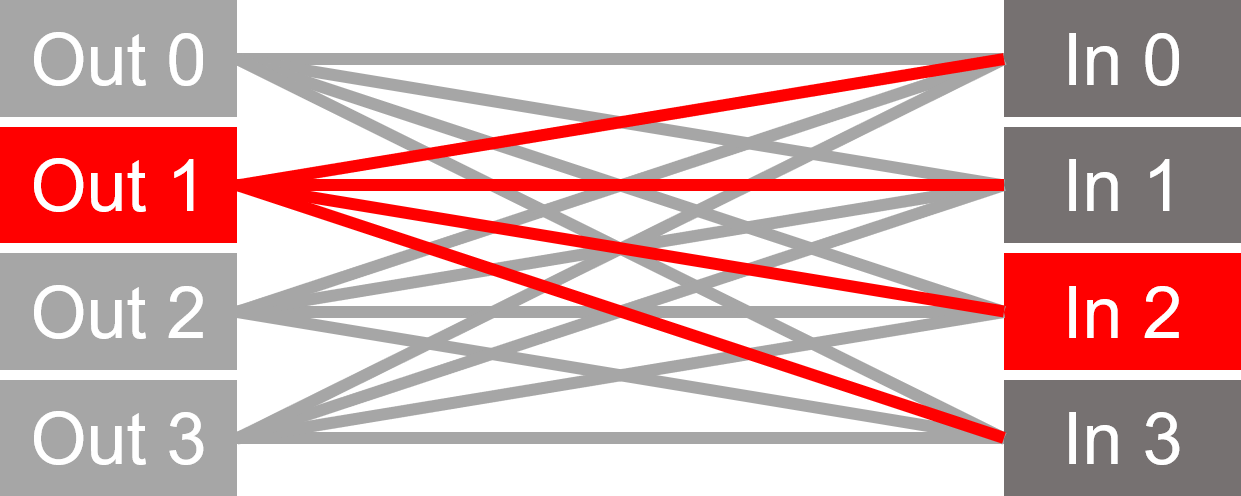

なぜクロスバーを使うのか?

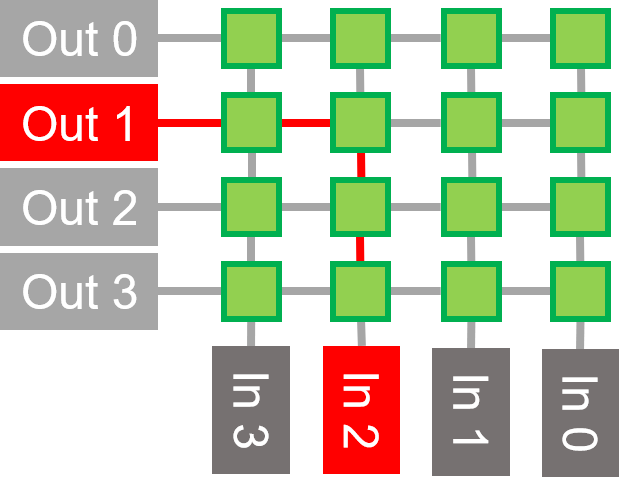

クロスバーは、マトリックス状に配置されたスイッチの集合体です。入力/出力グループ間の接続を 減らすことができます。

スイッチなし:

マルチプレクサ:すべてのイン/アウトが相互に接続されている。

クロスバースイッチ付

スイッチは、より少ない接続数で信号をルーティングします。

FPGAでは、接続数が少ない=配線が容易で、クロック周波数が高く、性能が向上する

クロスバースイッチの種類は複数ある

フルクロスバーとバタフライがその例です:

フルクロスバー:

行列は、入力の数と出力の数を掛け合わせたものである。

バタフライクロスバー

マトリックスサイズは、N×log2(N)/2(Nは入力数)です。

Butterflyを選んだのは、FPGAリソースの使用量が少なくて済むからです。しかし、場合によってはスループットが低下する可能性があります。

詳細はこちら

BittWareの「バタフライ・クロスバー・スイッチ

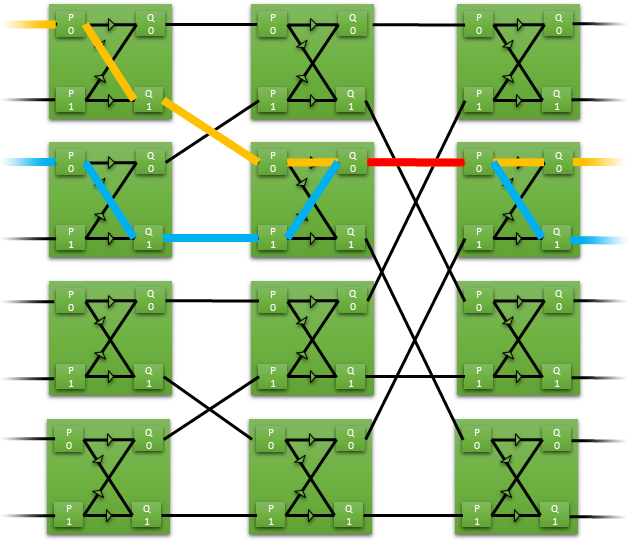

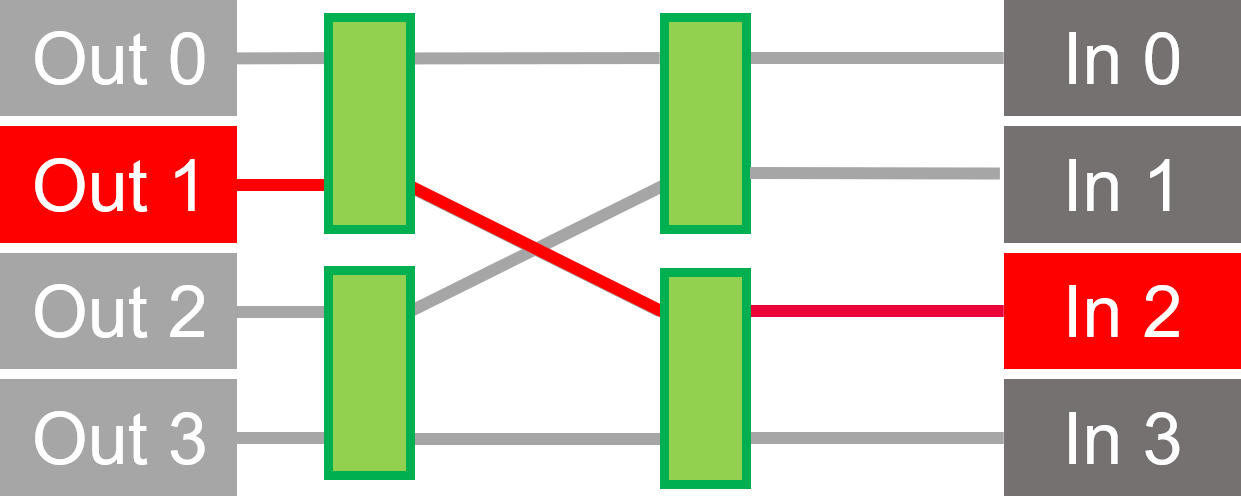

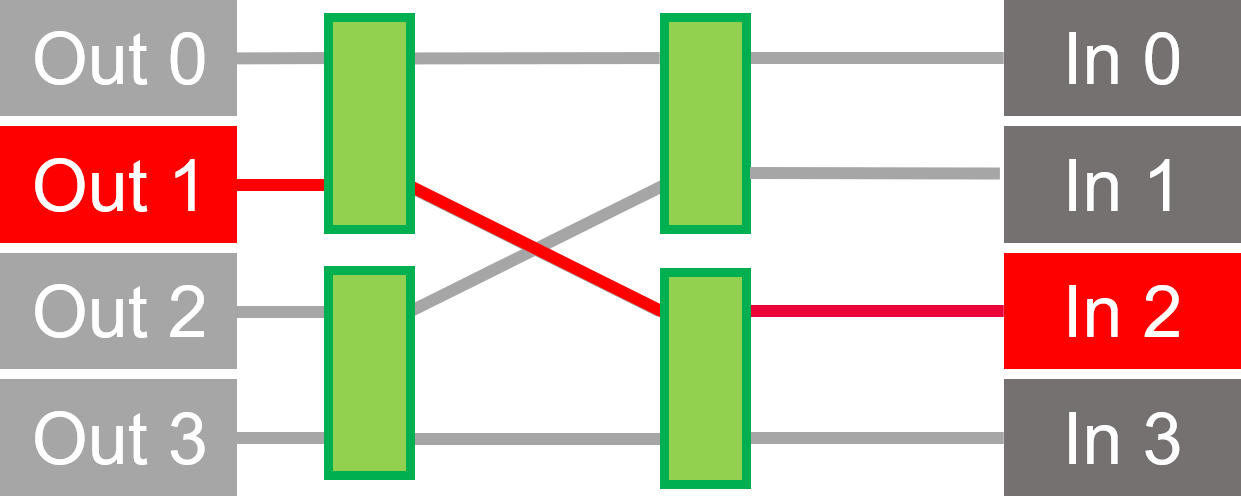

- 例:8入力-8出力クロスバー

- ポートルート0-2、2-3で衝突する例

- 仲裁はシンプルなピンポン方式を採用しているが、必要に応じてより高度な方式を簡単に実装できる。

画像をクリックすると、ポートルート0-2、2-3の衝突例をアニメーションで表示します。

このバタフライクロスバーの例では、わずか12個のスイッチで8個の入力を8個の出力にルーティングしています。各スイッチには2つの入力と2つの出力があります。データはそのままルーティングされるか、反対側のルートに切り替わります。

1つの経路しか切り替わらない場合、出力で衝突する可能性があり、スイッチは誰がその経路にアクセスできるかを仲裁しなければなりません。仲裁は、デフォルトでは単純なピンポン方式を採用していますが、必要に応じてより洗練された方式を簡単に実装することができます。

高位設計ツール(oneAPI DPC++)の使用について

高レベル言語(DPC++)を活用することで、クロスバースイッチを特定のアプリケーション要件に合わせて調整することができます:

- 並列カーネル(入力ポート)の数

- データパスの幅

- 同じデザインで複数の異なるクロスバーがある

これにより、リソースに最適化された設計が可能になります。常時アクティブな内蔵汎用スイッチが不要なため、電力を最小限に抑えることができます。

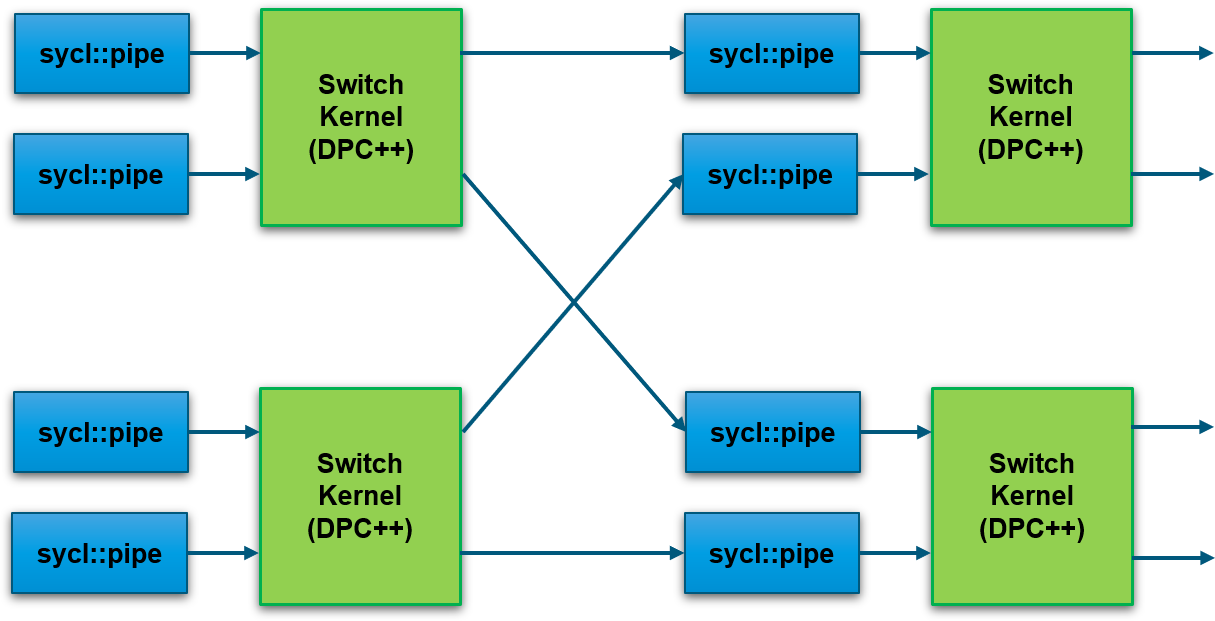

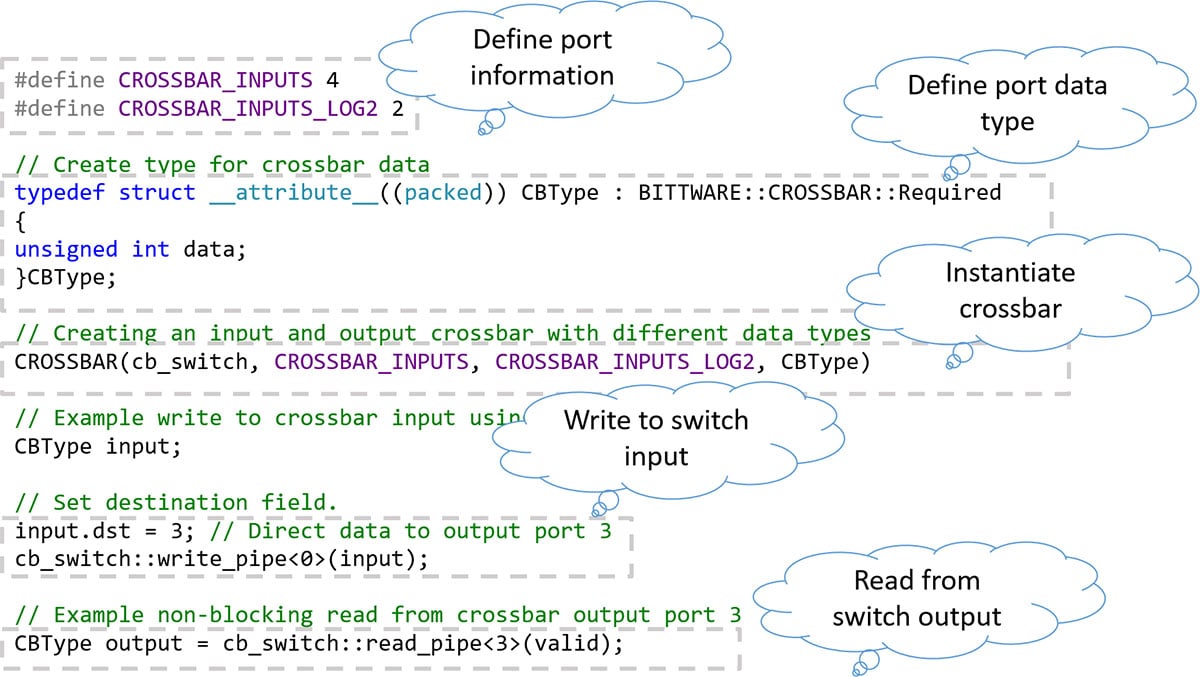

oneAPIツール(DPC++、SYCL)の使用について

- 各クロスバー・スイッチは、ユニークなスイッチ・カーネルのグループです

- スイッチはSYCLパイプで接続し、必要なポート数のクロスバーを作成します

- 各スイッチの幅は、必要なデータ型から推測されます。

- ポート数は2のべき乗であること

- 合成時に未使用のポートが最適化される

- データ型は、デスティネーション情報を含むスイッチメタデータ構造を継承すること。

- ポートはSYCLのパイプメソッドを使用し、必要に応じてブロッキングまたはノンブロッキングでアクセスされます。

DPC++でクロスバーを使う

BittWare'クロスバースイッチの3つの使用例

ネットワーク処理|HBM2のカーネル共有|分散型グラフ処理

ユースケース1:

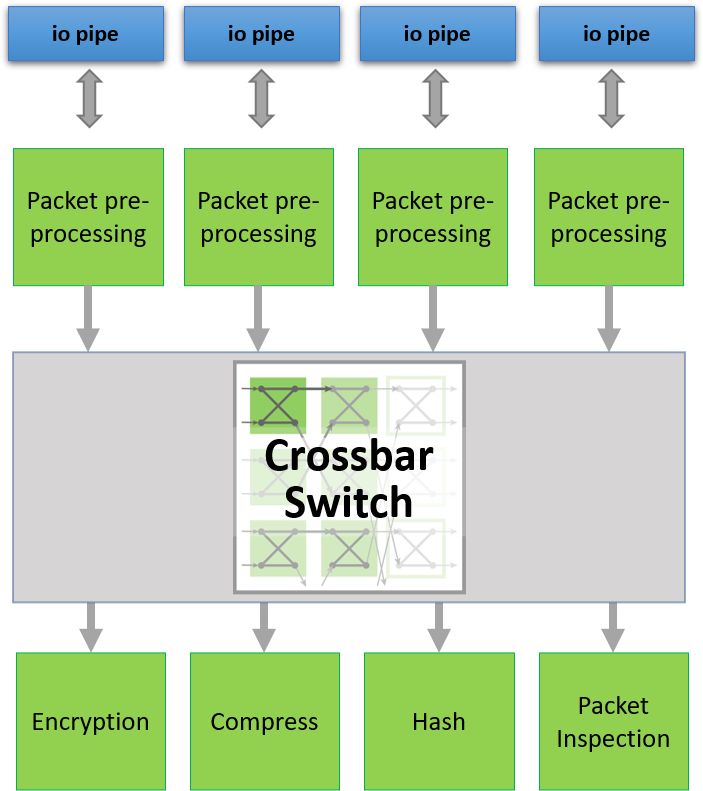

ネットワーク処理

oneAPIでIOインターフェイスと会話する

oneAPIは、ホストとFPGAの間のインターフェイスを抽象化します。外部I/O(図のQSFPなど)とのインターフェースも、oneAPI I/Oパイプを使用して抽象化されます。これにより、oneAPIをサポートする複数のBittWare FPGAカードにデザインをスケールアウトすることができます。

クロスバー・スイッチは、パケットをネットワーク・ポートへ、またはポートから直接送るために使用することができます。ここでは、DCP++のコードを少し修正することで、仲裁がネットワークパケットの境界上になるように変更しています。

ユースケース2:

HBM2のカーネル共有

(イーサリアムブロックチェーンのマイニングの例で)

Crossbar Switchを使用することで、HBM2メモリチャネルへのアクセスを共有する必要があるカーネルを最適化することができます。

そのユースケースとして、イーサリアムの採掘があります。

- Ethereumを競争力のあるパフォーマンスでマイニングするには、DAGと呼ばれる大規模な(現在は4.5GB)メモリ空間にアクセスできる複数の並列カーネルがそれぞれ必要です。

- イーサリアムマイニングのボトルネックはメモリ帯域なので、オンパッケージのHBM2は、サイズと帯域の両方の要件に見事に適合しています。

IntelStratix 10 MX FPGAは、32個の独立したHBM2メモリポートを備えています。

各ポートのピークスループットは12.8GBytes/Secです。

各ポートは、わずか512MBytesのメモリにアクセスできます。

合計16GByte

しかし、FPGAにはスイッチが内蔵されておらず、さらに高レベルのツールでは、複数のポートを自動的に連結したり、調停したりすることはできない。

当社のクロスバースイッチは、これらの問題を解決し、パフォーマンスを向上させることができます。

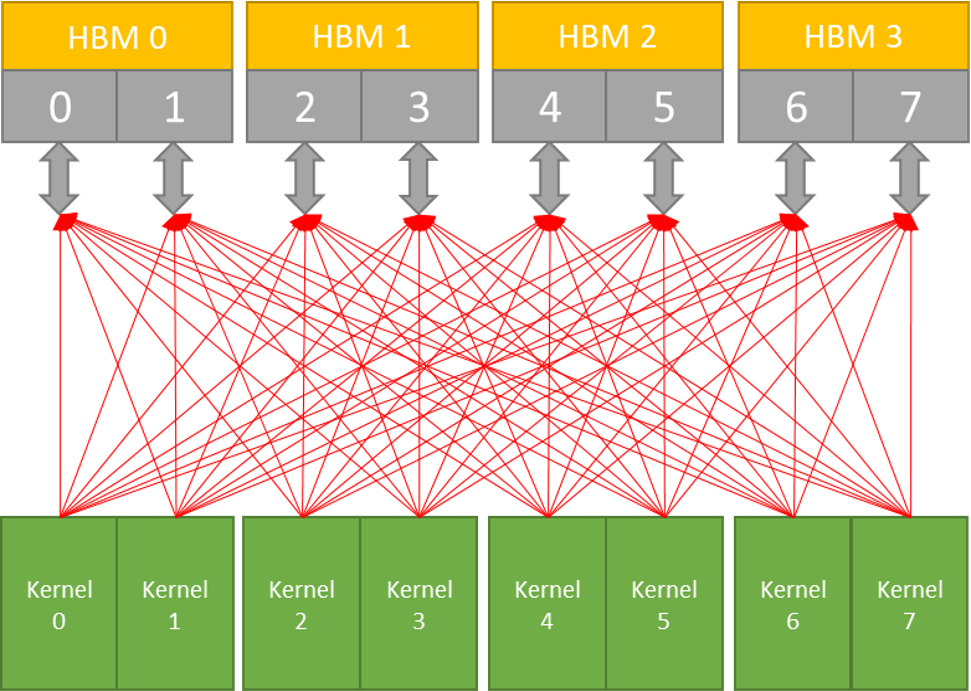

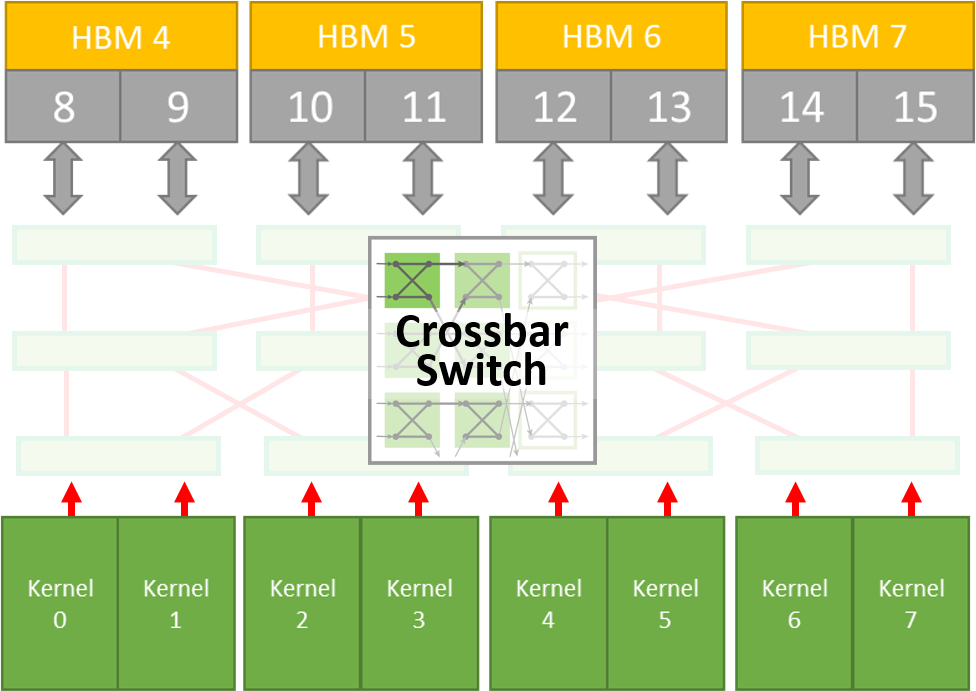

HBMメモリ8枚を共有する場合の例

クロスバーなし:多重化方式(アービトレーションなし)で多数の経路を持つ。

バタフライ・クロスバー・スイッチは、ルーティングを減らし、アービトレーションを追加して、より高いパフォーマンスを実現します。

ユースケース3:

分散型グラフ処理

- 大きなグラフは、複数のFPGAに分散して大きなメモリリソースを必要とします。

- クロスバースイッチは、カーネルのローカルとオフデバイスの間で通信するためのエレガントなソリューションです。

- グラフ処理には多くの応用がある

- 生物学、ソーシャルメディア、金融、その他多数

結論

- FPGAはユニークな機能を備えていますが、効率的に使用するには複雑で難しい場合があります。

- BittWareのバタフライ・クロスバー・スイッチIPは、複数のメモリやIOインタフェース間の共有アクセスを提供するシンプルな方法を提供し、これらの複雑さの一部を簡素化する。

- DPC++のような高級言語では、このようなIPをさまざまなユースケースに合わせて容易にカスタマイズすることができます。

ソースコードを要求する

BittWare バタフライ・クロスバー・スイッチは、このフォームに記入することでリクエストできます。弊社の営業チームが次のステップのために接続し、ライセンス契約の承諾とコードをダウンロードするためのログインをセットアップします。

"*"は必須項目