在一個API中高效共用FPGA資源

構建蝶形橫桿開關以解決 FPGA 中的資源分享問題

共用資源 問題

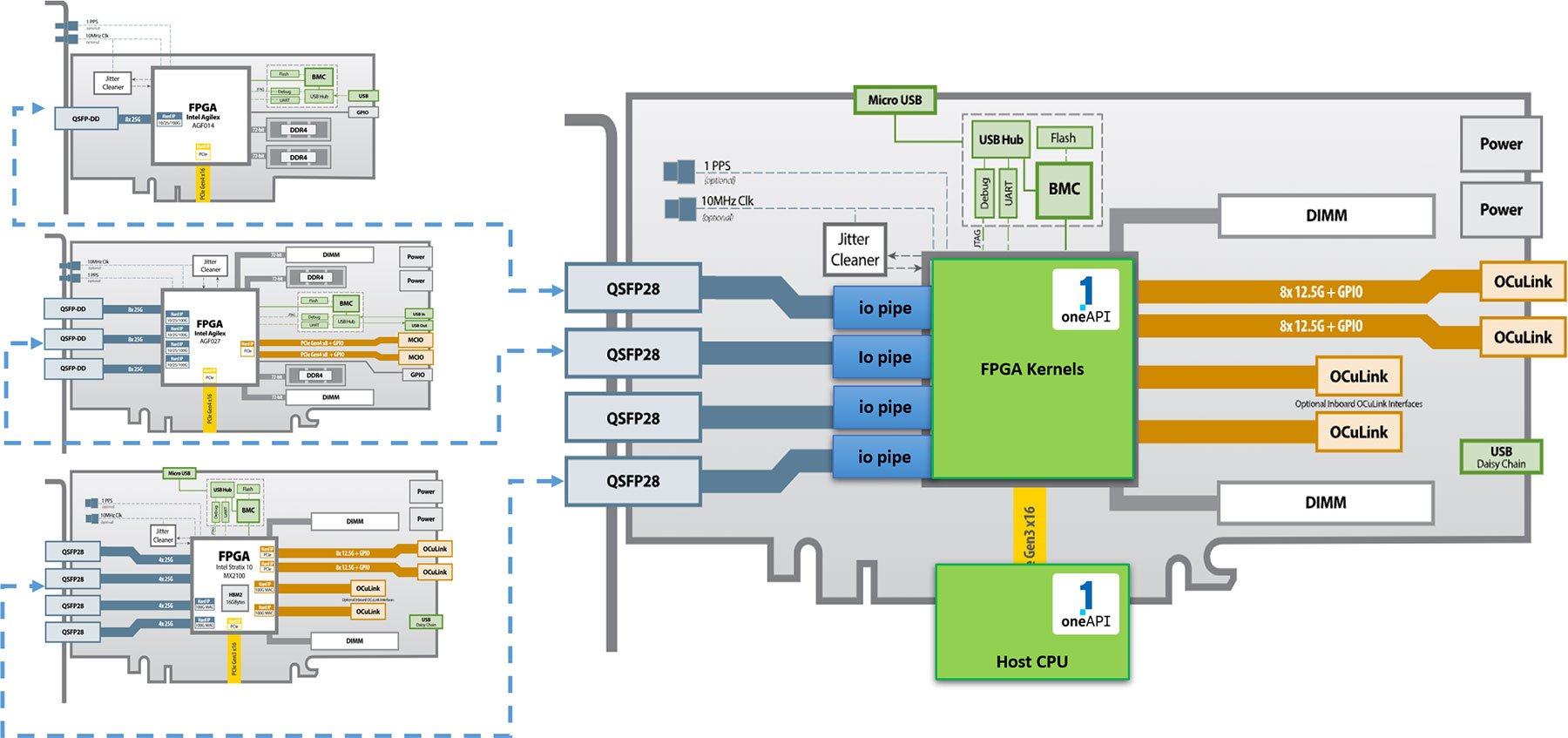

FPGA 卡通常具有許多高性能記憶體和 I/O 介面。

- 無內置緩存

- 無硬編碼仲裁邏輯

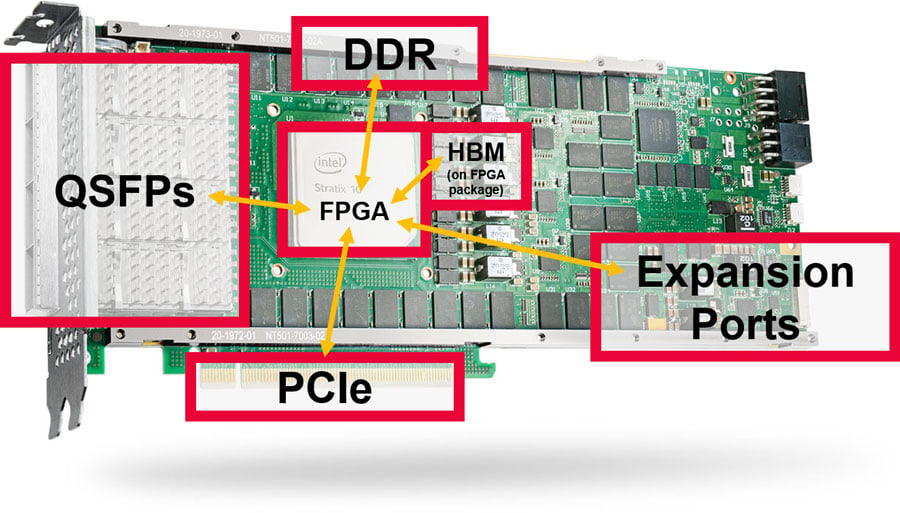

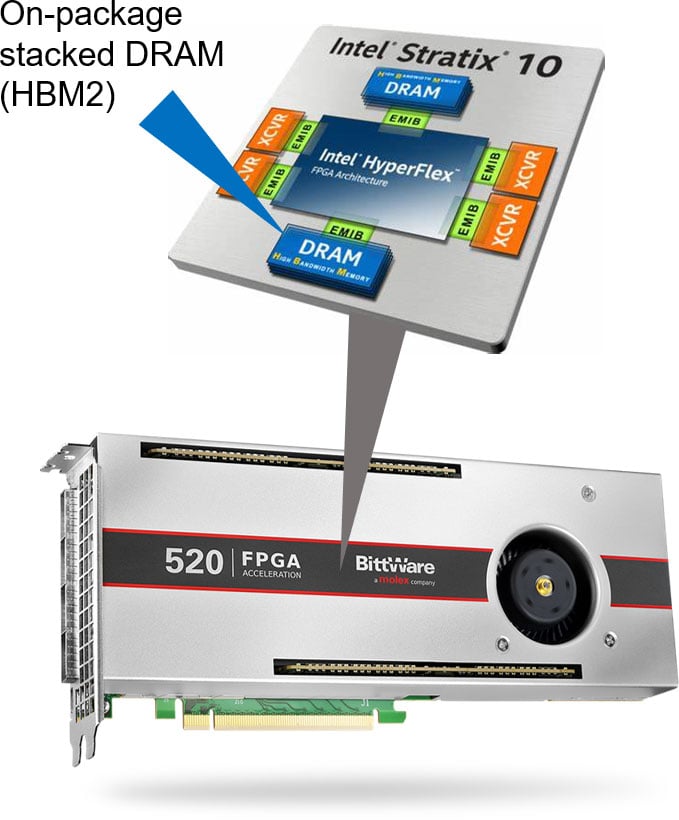

大型 FPGA,如英特爾的 Stratx 10 和 Agilex 系列,具有廣泛的 I/O 介面。BittWare通過提供QSFP,PCIe,卡上DDR4和GDDR6記憶體和擴展埠等功能來提供使用這些卡。我們也有採用封裝上HBM2的FPGA的卡。

訪問所有這些介面並不簡單,尤其是在需要在多個內核之間共用資源的情況下。FPGA 除了基本記憶體控制器外,沒有內置緩存或仲裁邏輯 — 仲裁是用戶的責任。

我們對共用資源問題 的解決方案 :

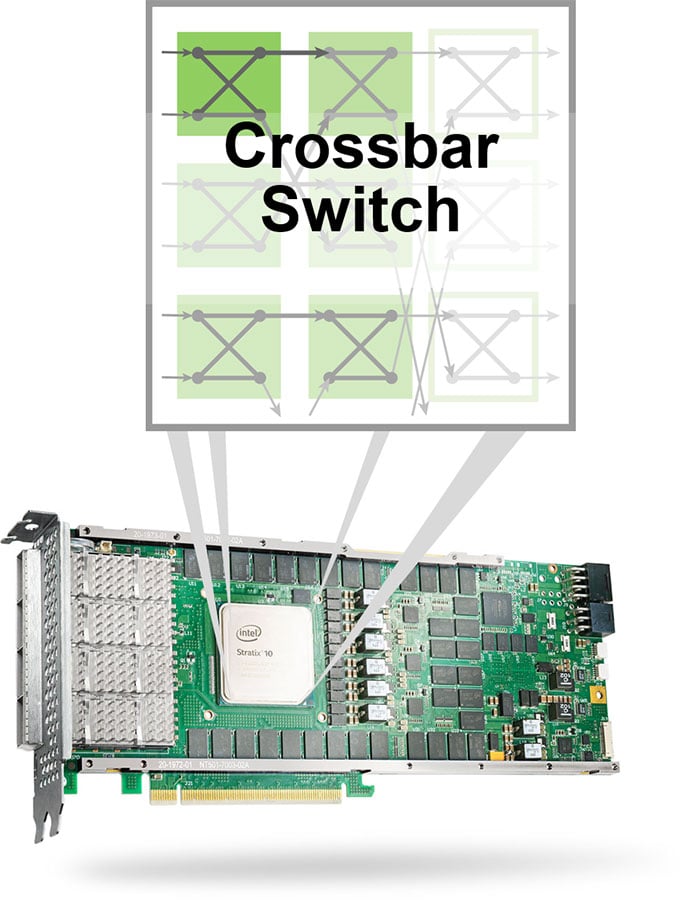

在 FPGA 邏輯 中 建立交叉 開關

我們使用英特爾 ® oneAPI 構建了一個蝶形交叉開關。

- 通過使用 oneAPI(一種高級工具)而不是低級 RTL,我們獲得了一個 易於配置 的解決方案, 該解決方案可輕鬆 針對不同用途進行優化

- 我們瞄準了 520N-MX 卡;該代碼可以使用oneAPI在其他BittWare卡上使用

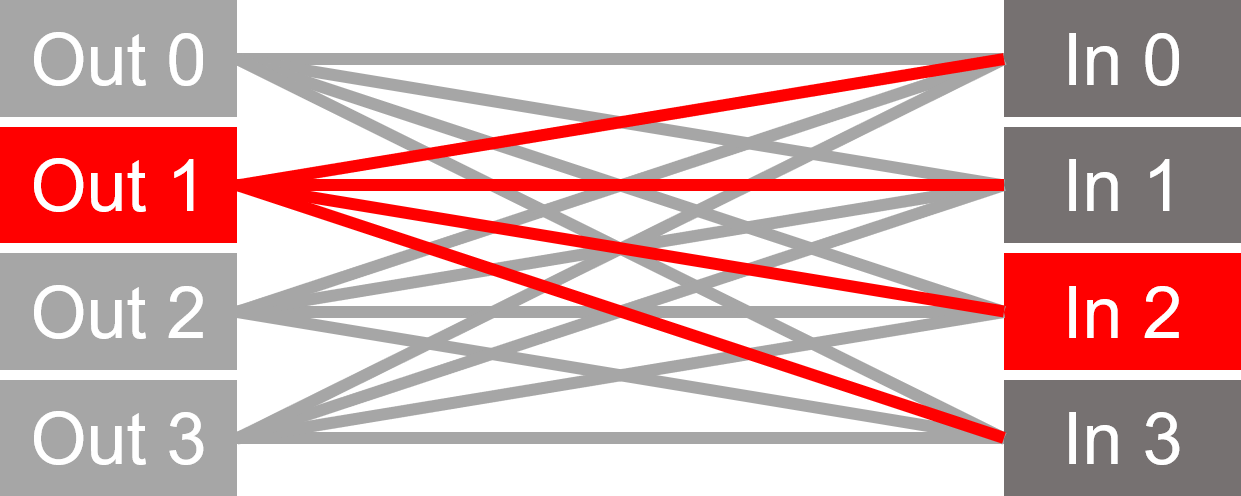

為什麼要使用橫杆?

橫杆是排列在矩陣中的開關的集合。它 減少了 一組輸入/輸出之間所需的 連接 。

沒有 開關:

多路複用器:所有輸入/輸出互連。

帶橫杆開關

交換機使用較少的連接路由信號。

在 FPGA 中,更少的連接 = 更簡單 的 佈線、更高的時鐘 頻率和 更好的 性能

有多種類型的交叉開關

兩個例子是全橫杆和蝶形:

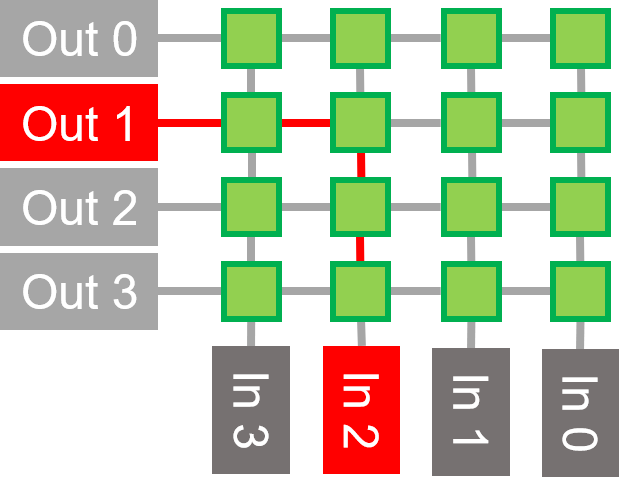

全橫杆:

矩陣等於輸入數乘以輸出數。

蝴蝶橫桿

矩陣大小為 N x log2(N) / 2,其中 N 是輸入數。

我們之所以選擇 Butterfly ,是因為它使用的 FPGA 資源更少。但是,在某些情況下,它可能會降低輸送量。

更多詳情:

BittWare的蝴蝶橫桿開關

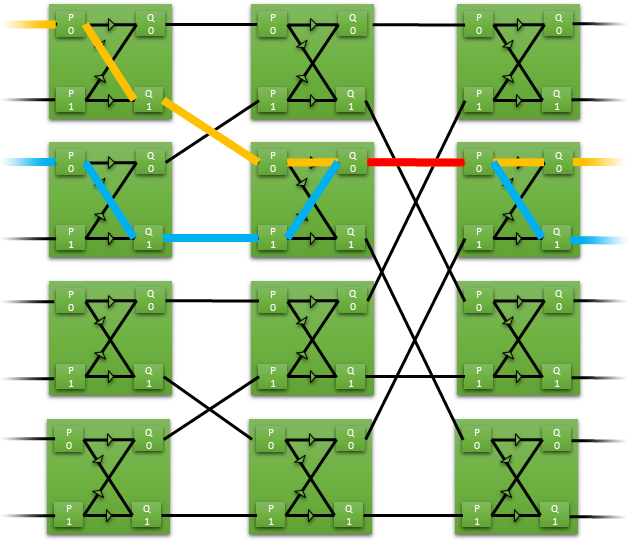

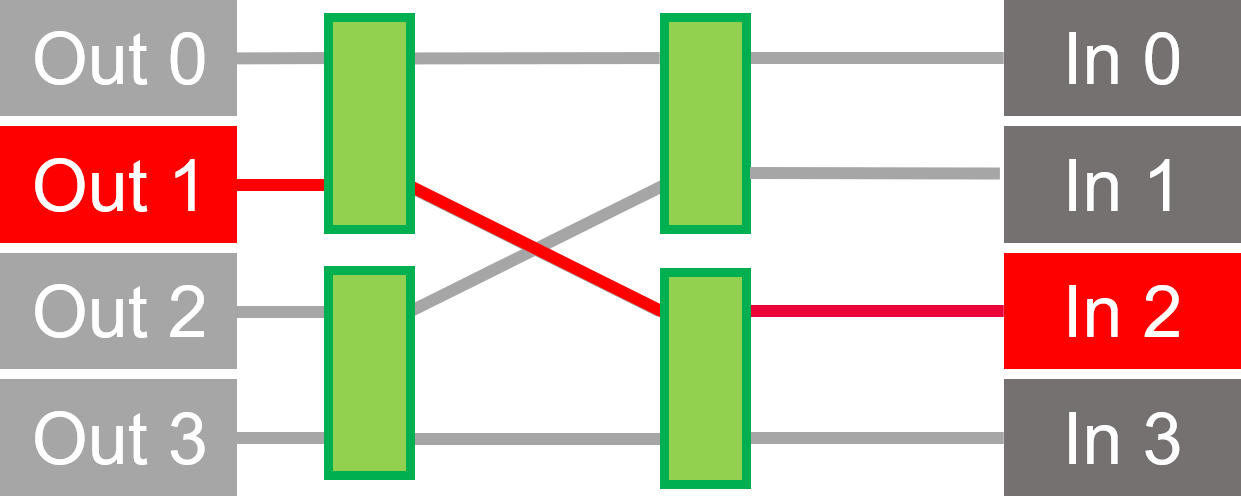

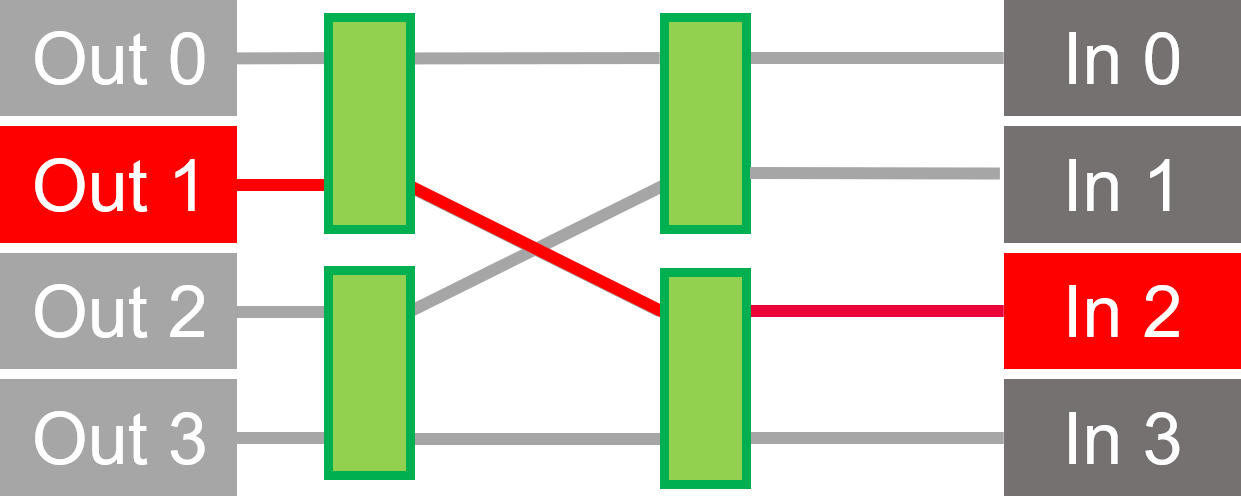

- 示例:8 個輸入到 8 個輸出橫杆

- 港口路由 0-2 和 2-3 上的衝突示例

- 仲裁使用簡單的乒乓球方案,但如果需要,可以輕鬆實施更複雜的方案

按兩下圖像以動畫顯示埠路由 0-2 和 2-3 上的範例衝突。

在這個蝶形橫桿的例子中,8個輸入僅使用12個開關就路由到8個輸出。每個開關有兩個輸入和兩個輸出。數據直接路由或切換到相反的路由。

如果只切換一條路徑,則輸出端可能會出現衝突,交換機必須仲裁誰有權訪問該路徑。仲裁預設使用簡單的乒乓球方案,但如果需要,可以輕鬆實施更複雜的方案。

使用進階設計工具(oneAPI DPC++)

通過使用高級語言 (DPC++),可以針對特定應用要求定製交叉開關,例如:

- 並行內核(輸入埠)的數量

- 數據路徑的寬度

- 同一設計中的多個不同橫杆

這允許針對資源優化設計。通過消除對始終處於活動狀態的內置通用開關的需求,將功率保持在最低水準。

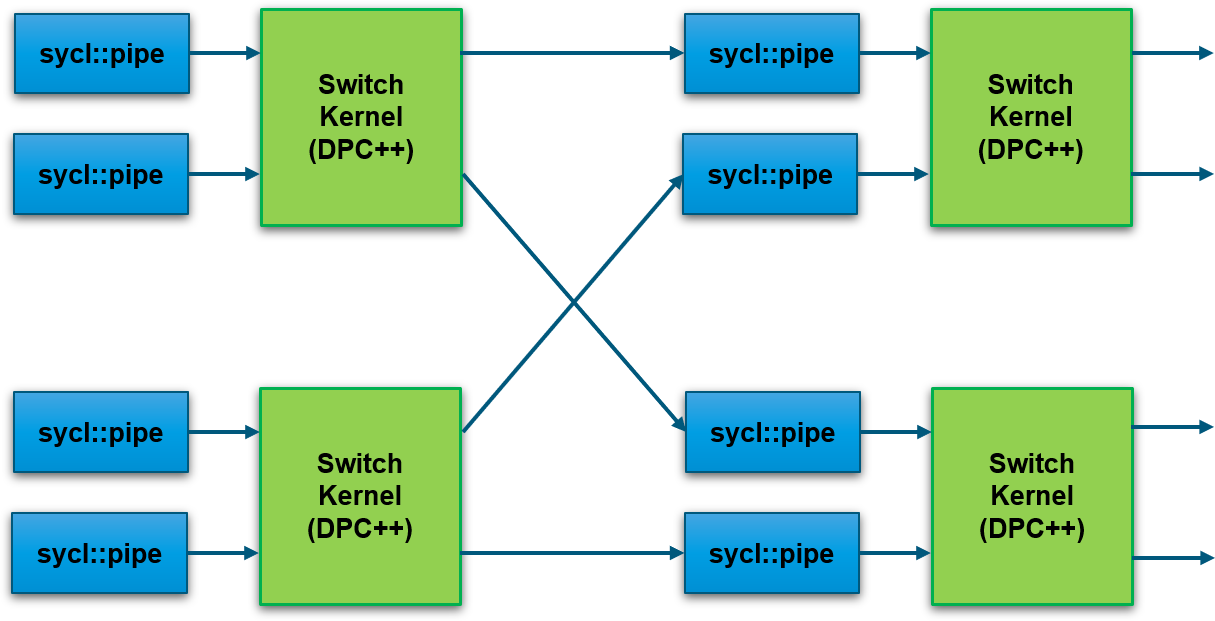

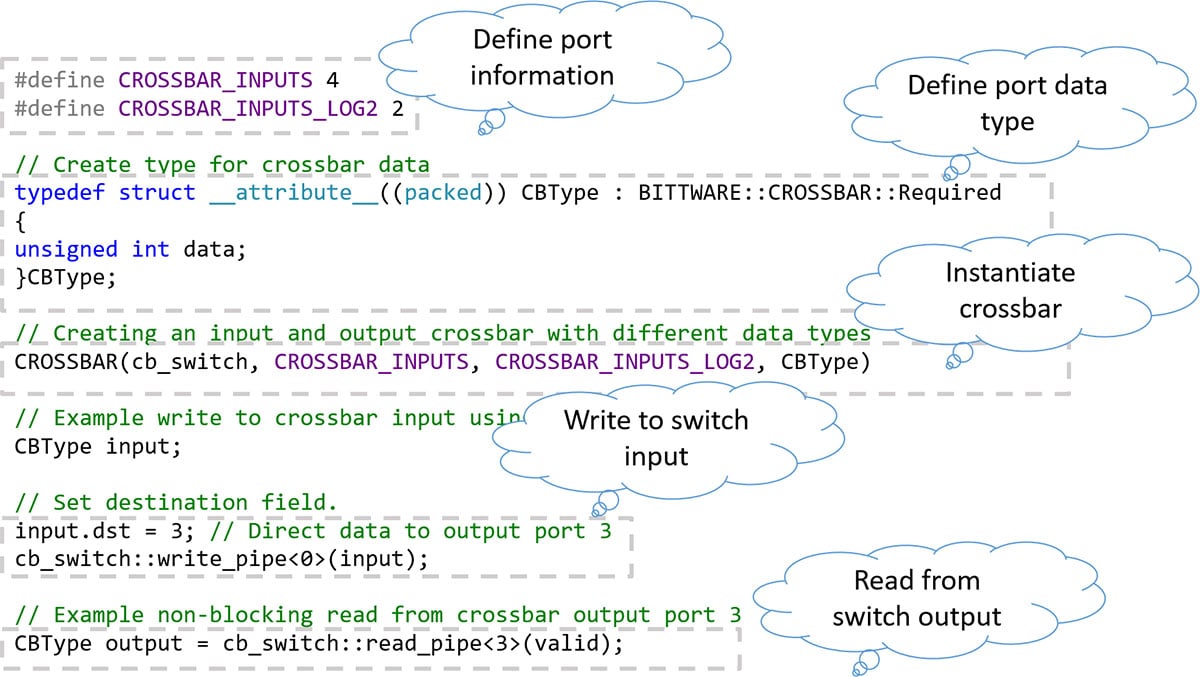

使用 oneAPI 工具(DPC++ 和 SYCL)

- 每個交叉開關都是一組唯一的開關內核

- 交換機通過 SYCL 管道連接,以創建具有所需埠數的橫杆

- 每個開關的寬度隱含在所需的數據類型中

- 埠數必須為2的冪

- 未使用的埠在合成過程中得到優化

- 數據類型必須繼承包含目標資訊的交換機元數據結構

- 埠使用 SYCL 管道方法訪問,根據需要阻塞或非阻塞

在 DPC++ 中使用橫杆

BittWare橫桿開關的三個示例用例

網路處理 |HBM2 的內核共用 |分散式圖處理

用例 1:

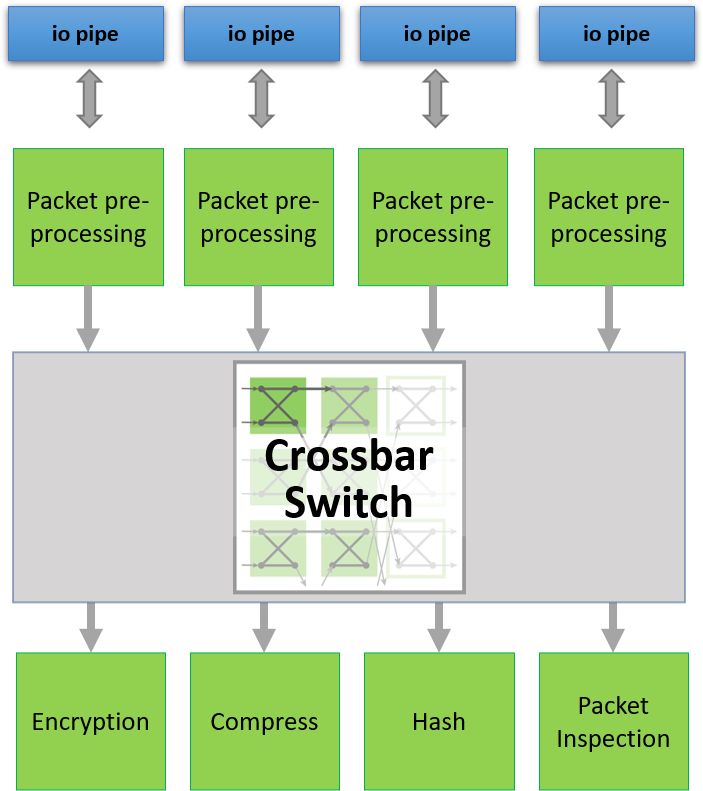

網路處理

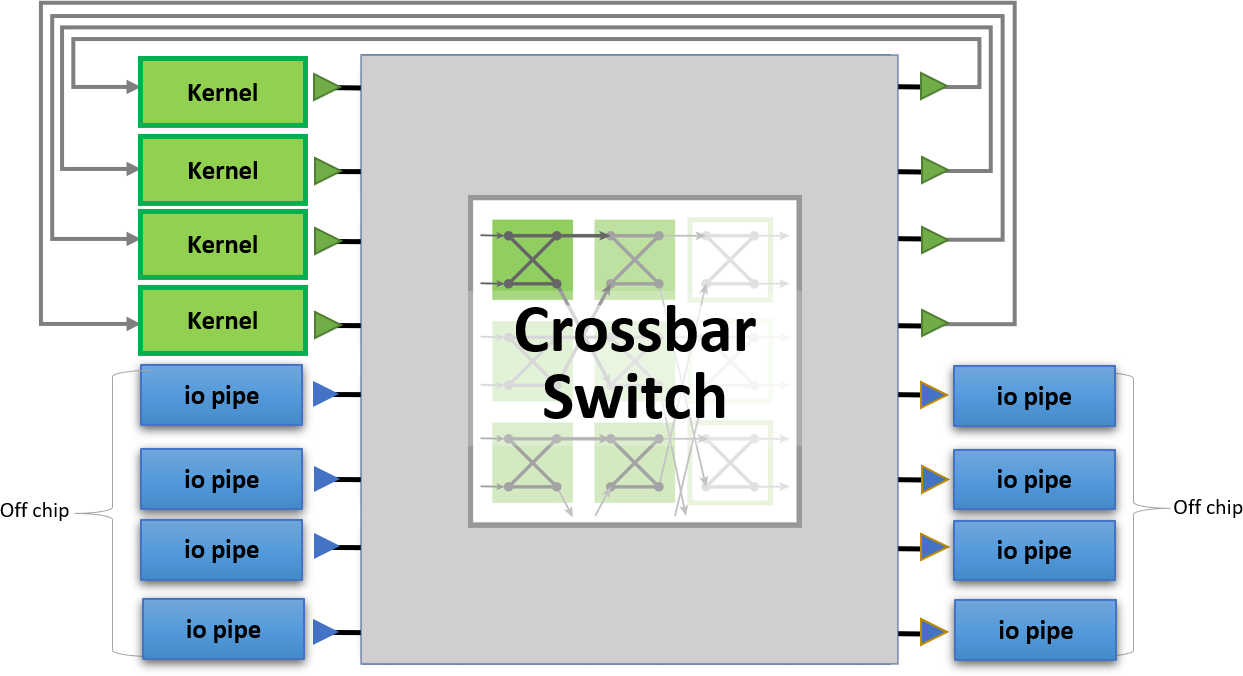

在一個 API 中與 IO 介面通信

oneAPI 抽象了主機和 FPGA 之間的介面。具有外部 I/O 的介面(例如圖中的 QSFP)也使用 oneAPI I/O 管道進行抽象。這允許將設計擴展到支援oneAPI的多個BittWare FPGA卡。

交叉開關可用於將數據包定向到網路埠或從網路埠定向數據包。在這裡,對 DCP++ 代碼的一個小修改將仲裁更改為在網路數據包邊界上。

用例 2:

HBM2 的內核共用

(以乙太坊區塊鏈挖礦為例)

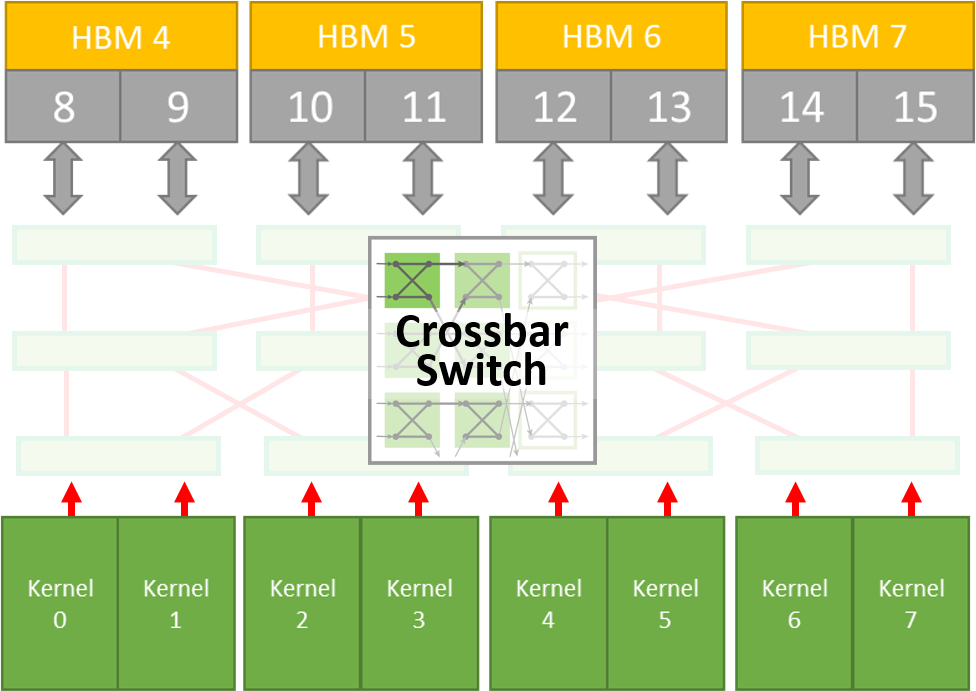

使用交叉開關,我們可以優化需要共用訪問 HBM2 記憶體通道的內核。

一個用例是挖掘乙太坊。

- 挖掘具有競爭力性能的乙太坊需要多個並行內核,每個內核都可以訪問稱為DAG的大型(目前為4.5 GB)記憶體空間。

- 乙太坊挖礦的瓶頸是記憶體頻寬,因此封裝上的 HBM2 非常適合大小和頻寬要求。

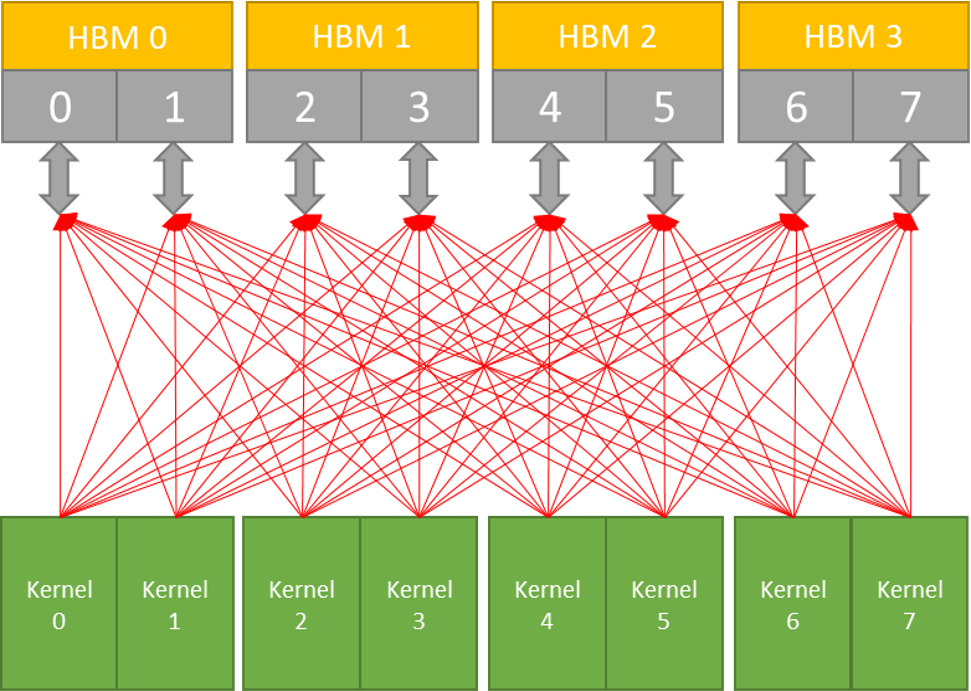

英特爾 Stratix 10 MX FPGA 具有 32 個獨立的 HBM2 記憶體埠。

每個埠的峰值輸送量為12.8 GB/秒。

每個埠只能訪問 512 MB 記憶體

共 16 GB

但是,FPGA沒有內置開關,而且高級工具不會自動連接或仲裁多個埠。

我們的橫杆開關可以解決這些問題以提高性能。

共用 8 個 HBM 記憶體的範例

沒有 橫杆:使用多路複用方法的大量路由(無仲裁)。

我們的蝶形橫桿開關減少了佈線,並增加了仲裁以提高性能。

用例 3:

分散式圖處理

- 大型圖形需要分佈在多個FPGA上的大量記憶體資源。

- 交叉開關是在本地內核和關閉設備之間進行通信的優雅解決方案。

- 圖形處理有很多應用

- 生物學、社交媒體、金融等等

結論

- FPGA 具有獨特的 功能 ,可能很複雜且 難以 有效使用。

- BittWare的Butterfly Crossbar Switch IP提供了一種在多個記憶體或IO介面之間提供共用訪問的簡單方法,簡化了其中一些複雜性。

- DPC++等高級語言允許針對不同的用例輕鬆定製此類IP。

請求原始程式碼

您可以通過填寫此表格來請求BittWare蝴蝶橫桿開關。我們的銷售團隊將與您聯繫,以完成後續步驟,以接受許可協定並設置登錄以下載代碼。

“*”表示必填欄位