솔루션

AI/ML 추론의 혁신

AI 가속을 위한 더 스마트한 접근 방식 활용하기

추론 가속화의 새로운 물결

몇 년 사이에 AI/ML 모델과 추론에 많은 변화가 있었습니다. 훈련 알고리즘을 처리하는 데 탁월한 하드웨어는 실시간 배치 크기 1 추론에서는 지연 시간과 활용도가 떨어질 수 있습니다. 딥러닝 모델은 더욱 복잡해져 실시간 애플리케이션이 이를 따라잡기 위해서는 새로운 접근 방식이 필요합니다.

좋은 소식은 머신 러닝이 발전함에 따라 가속 기술이 더욱 스마트해지고 효율성이 높아졌다는 점입니다. 이는 전용 ASIC 디바이스를 사용하는 것과 같은 실리콘 수준과 연결에 8비트 정수를 사용하는 것과 같은 설계 접근 방식 모두에서 이루어집니다.

30년 이상 최고의 가속 기술을 시장에 선보이며 신뢰를 쌓아온 브랜드인 BittWare는 추론에 최적화된 FPGA 및 ASIC 기반 AI 솔루션 에코시스템을 구축했습니다.

CPU 또는 GPU 기반 시스템을 최신 데이터센터급 텐서 프로세서로 확장하든, 엣지 중심 솔루션을 사용하여 모든 성능을 최대한 활용하든, 위험을 줄이고 시장 출시 기간을 단축하는 데 필요한 모든 것을 갖추고 있습니다.

비트웨어 + ML/AI 추론

비트웨어 사용 시기

- 훈련된 모델이 있고 이를 배포하는 데 도움을 요청하는 경우

- 배포 개념 검증을 도와드릴 수 있습니다.

- PCIe 카드가 적합하지 않은 경우, 사용자 정의에 대해 논의할 수 있습니다.

- 추론 모델에 실제 데이터를 가져오는 옵션에 대해 이야기할 수 있습니다.

배포 대상

BittWare AI/ML 고객은 어디에 배포하나요?

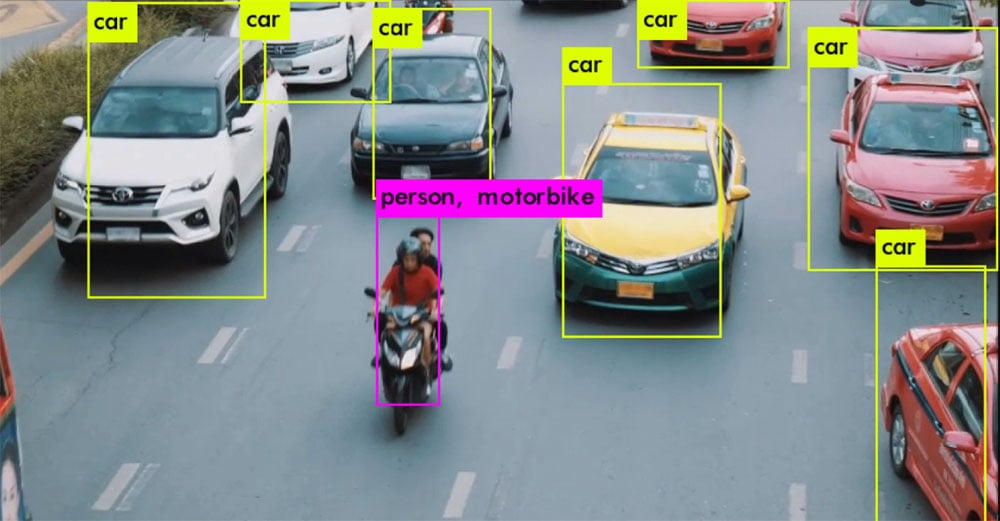

- "엣지에서의 배포"는 감시 카메라부터 전신주, 사무실 건물 내부의 옷장까지 모든 것을 포함합니다.

- 데이터센터 내부에 특수 목적 장치를 배포하는 데 도움을 드릴 수 있습니다(파트너는 일반적으로 데이터센터 내부의 기존 서버를 잘 다루고 있습니다).

개발 플랫폼

일부 파트너의 경우 기술 평가에 사용되는 개발 플랫폼도 제공하고 있습니다.