白皮书

利用BittWare FPGA解决方案构建NVMe Over Fabrics

概述

自非易失性内存快车(或NVMe)协议推出以来,数据中心客户已广泛采用这项新技术,它为存储应用带来更高的性能和低延迟(Gupta,2018)。NVMe的功能集已使该技术成为市场上增长最快的存储解决方案。到2021年,国际数据公司预测,基于NVMe的存储解决方案将产生超过50%的与主要外部存储出货量相关的收入(Burgener, 2019)。

BittWare提供FPGA加速解决方案,以实现基本的硬件卸载(压缩、去重等)以及特定的应用算法,如使用FPGA进行推理的机器学习应用。这种以与NVMe相匹配的性能水平对存储进行基本和高级加速的混合,就是我们所说的计算型存储。我们的250系列产品,包括250S+、250-SoC和250-U2,专注于这个市场。

最近,NVMe联盟推出了一个名为NVMe over Fabrics(NVMe-oF)的协议变体,以利用NVMe在现有网络基础设施上的优势。随着数据中心继续看到内部NVMe存储的扩展,远程用户可以使用NVMe-oF以很少的开销访问分解的存储(Gibb,2018)。这需要在硬件中实施专门的网络堆栈,以保持NVMe的低延迟和高带宽优势。

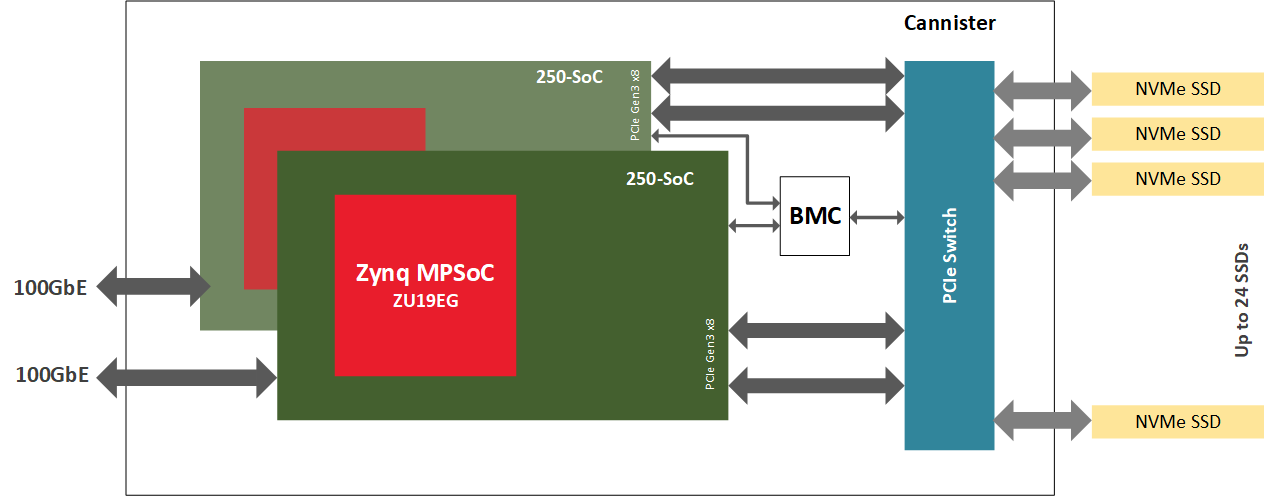

我们的解决方案使用了带有片上ARM处理器的FPGA,即我们250-SoC板上的Xilinx Zynq MPSoC。FPGA作为NVMe-oF控制器,从CPU卸载,甚至在使用片上处理器时与CPU解耦。我们通过在FGPA逻辑中完全实现NVMe数据平面,包括网络协议栈,提供低延迟和高带宽。ARM内核在设计中使用软件来处理控制平面,其中延迟和带宽是一个较小的问题。本应用说明介绍了如何将BittWare 250-SoC配置为JBOF中的NVMe-oF控制器。

什么是NVMe Over Fabrics

NVMe-oF协议使用高速SSD技术,并将其扩展到本地服务器或数据中心之外。

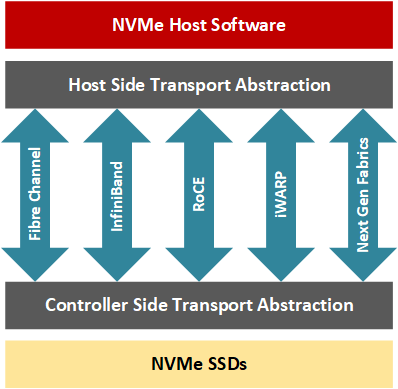

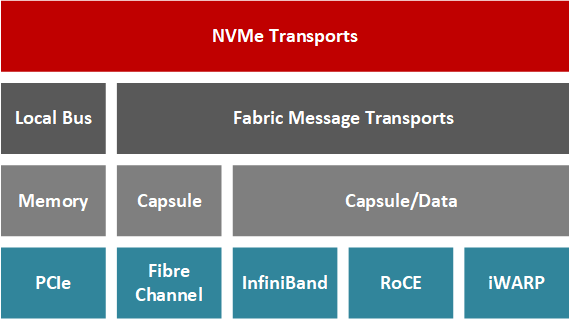

NVMe-oF允许应用程序开发人员访问网络结构上的远程存储节点,如光纤通道、InfiniBand、RDMA(远程直接内存访问)聚合以太网(RoCE)、iWARP和最近的TCP/IP,同时保持低延迟(通常在100个NVMe驱动器集群的10us到大型集群的100额外微秒之间)。简而言之,NVMe-oF交易涉及一个主机和一个目标;目标是服务器在网络上暴露NVMe块存储设备供主机服务器访问(Davis,2018)。通过RDMAs,主机-目标数据传输可以在没有CPU处理交易的情况下进行;相反,专用的RNIC在资源之间传递数据,对计算资源的影响很小,因为NIC中的部分硬件管理着网络堆栈的传输层。

为什么在NVMe-oF中使用FPGA?

当你决定将NVMe-OF卸载到PCIe卡时,你基本上有三种选择:

首先,你可以使用ASIC实现,这将是最低成本和最低延迟的选择。然而,ASIC不允许你同时卸载 "计算存储 "算法。ASIC一般也只适用于最流行的网络带宽,而这很少是最高的带宽。

第二,你可以使用具有高核心数的片上系统,这将允许你增加 "计算存储 "算法。然而,这样做需要并行编程技巧。最终的解决方案通常是这里的选择中延迟最高的,这直接违背了NVMe的低延迟价值主张。与ASIC一样,这些MPP SOC通常只适用于最流行的网络带宽,而这些带宽很少是最高带宽。

第三,你可以使用FPGA。这个选项允许你添加 "计算存储 "算法,同时保持类似ASIC的延时。这个选项还可以实现高带宽网络,如100或甚至400Gb。尽管它可能是三个选项中最昂贵的,但当你考虑到存储市场所涉及的数量时,成本差异就会变得只有一点点。

自适应存储

通过利用FPGA和SoC等技术,数据中心架构师可以进一步减少数据密集型操作在CPU之间的数据移动。通过硬件驱动的加速,用户应用程序显示出更高的性能和更低的响应时间。随着空闲CPU周期数量的增加,分配工作负载的进程利用混合系统架构,更有效地使用专用硬件和CPU。FPGA结构、它们的IO吞吐量和它们的编程灵活性促进了可重新配置的硬件与高带宽NVMe存储紧密结合的设计。例如,FPGA特别适用于压缩、加密、RAID和擦除代码、重复数据删除、键值卸载、数据库查询卸载、视频处理或NVMe虚拟化等。FPGA硬件提供了专用解决方案的性能,但也具有可重新配置的优势,可以随着数据中心需求的变化快速切换用途。

在NVMe-oF目标中使用Xilinx MPSoC

BittWare 250-SoC采用Xilinx UltraScale+ Zynq ZU19EG MPSoC,可以通过两个QSFP28端口连接到网络结构,并通过一个16通道的主机接口或四个8通道的OCuLink连接器连接到PCIe结构。这个MPSoC适配器是驱动NVMe-oF目标节点的完美平台,因为它结合了FPGA结构(也称为PL或可编程逻辑)中的数据流计算、网络IO、PCIe连接和板载ARM处理器。请注意,ARM不在数据平面内;它处理控制平面的工作。在CPU和存储端点之间放置一个专门的硬件加速器,可以创建一个优化的系统,使计算更接近数据。

硬件

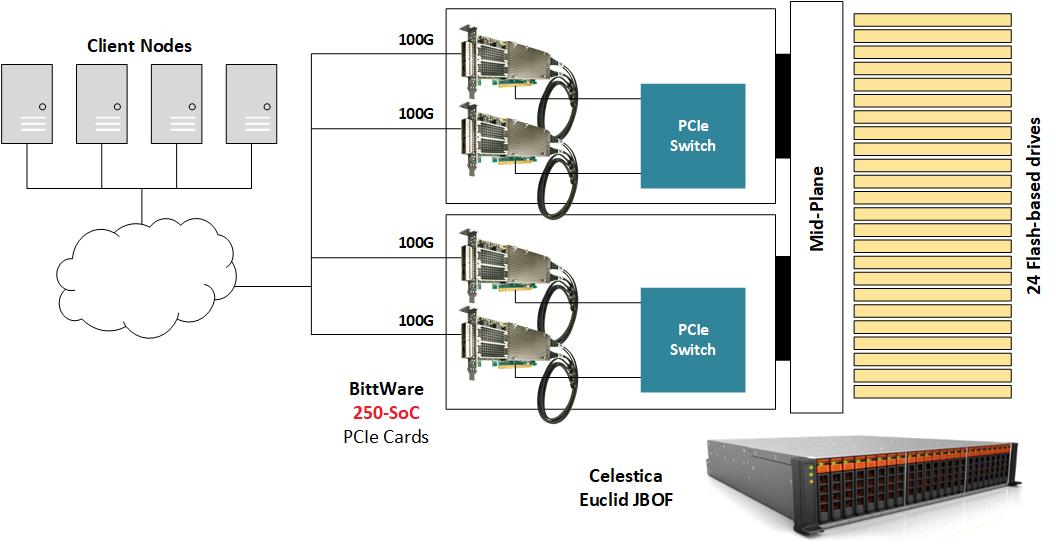

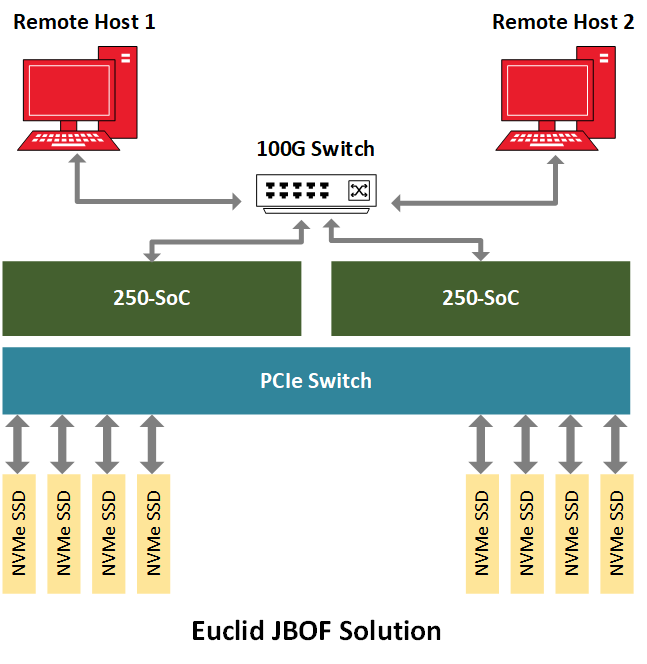

为了演示NVMe-oF,BittWare将250-SoC放置在一个JBOF(Just-A-Bunch-Of-Flash)机箱内,该机箱内装有多个NVMe U.2硬盘,并将250-SoC板的QSFP28端口暴露在网络上。Celestica Euclid JBOF具有两个带有PCIe交换机和PCIe插槽的插入式刀片;每个抽屉充当网络结构和NVMe存储之间的管道。NVMe数据包从QSFP28端口转到FPGA结构,然后经过PCIe主机接口、JBOF的PCIe交换机,最后到达NVMe驱动器。在这个实施方案中,250-SoC的OCuLink连接器没有被使用,但在不同的硬件平台上,它们可以容纳这种设计的电缆版本,PCIe交易将通过电缆运行。

闸道器

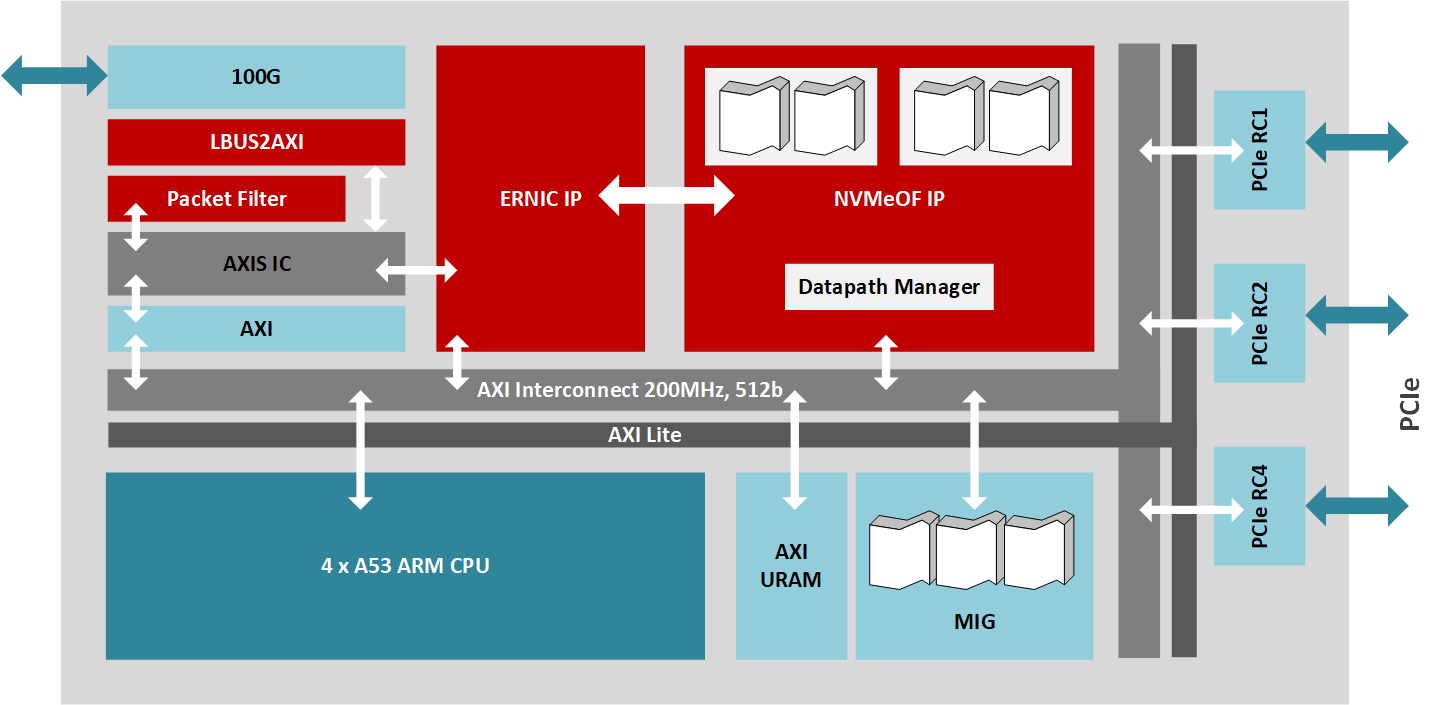

该设计实现了RoCE v2的NVMe-oF目标(符合NVMe 1.2和NVMe-oF 1.0规范),支持明确的拥堵管理。针对MPSoC的IP使用了几个赛灵思的IP库块,所有的数据面都是通过512位AXI总线以200MHz的速度互连的。赛灵思嵌入式RDMA NIC处理100Gb/s的网络流量,而PCIe root complex IP核管理与驱动多达24个驱动器的JBOF电路的16通道PCIe 3.0接口的连接,而DMA核控制AXI总线上的高速数据传输。此外,NVMe-oF目标核心通过100Gb/s的数据路径管理多达256个队列,而运行在四核A53 ARM处理器上的固件处理存储节点的高级管理。

最大限度地提高性能

MPSoC PL可以容纳数据路径的最大带宽。因此,为了展示整个系统的最大能力,主机必须产生尽可能接近100Gb/s的网络流量。为了进行基准测试,几个NVMe-oF主机连接到一个网络交换机,然后可以将最大的数据吞吐量输送到JBOF中运行NVMe-oF目标的250-SoC MPSoC卡。该参考设计显示了大约2.5 MIOPS的随机读取性能和超过1.1M的随机写入性能,同时显示了105us的应用延时。

可重新配置的硬件解决方案的优势

与软件(CPU+外部网卡+SPDK)或RNIC解决方案(CPU+集成网卡)相比,基于MPSoC的NVMe-oF解决方案具有若干优势。如果基于MPSoC的解决方案与其他产品相比具有相对较高的成本和功耗,那么从带宽、可配置性和延迟的角度来看,这种技术要优于竞争对手。类似地,对于RNIC解决方案,MPSoC的NVM-oF将使网络接口的吞吐量达到饱和。然而,MPSoC的硬件实现提供了其他解决方案所不具备的灵活性和适应性水平。因此,这种自适应硬件可以针对特定领域的应用,允许系统架构师将客户定义的功能(RAID,或随着规范发展的新NVMe功能)与主IP相结合,并增强整个系统的功能集。另一个选择是添加自定义加速器,如加密或压缩,以在一个盒子里结合两种功能。最后,解决方案供应商可以创建针对特定用途的硬件产品,如视频处理(例如,视频编解码器)或人工智能工作负载进行优化。通过将存储管理等IT功能与通常由昂贵的计算节点执行的任务相结合,CPU从不得不执行高带宽的IO传输中解脱出来,被重新用于更多的计算关键操作。从延迟的角度来看,基于MPSoC的解决方案提供了比CPU驱动的替代品更低和可预测的延迟。

总结

随着NVMe在过去几年的成熟,它为NVMe-oF铺平了道路,现在它为分解的存储环境提供了与NVMe类似的好处(Weaver,2019)。该技术提高了计算和存储节点的利用率,同时提高了数据中心的敏捷性和性能(Waever,2019)。NVMe-oF允许开发人员以新颖的方式瞄准应用程序,例如,需要在庞大的数据集(几百PB)上随机读取的人工智能工作负载将大大受益于这项技术(Hemsoth,2019)。FPGA和MPSoC在NVMe-oF协议的基础上提供了一个额外的创新层;这些设备中的可编程逻辑允许设计能够处理高带宽数据传输、低延迟的系统架构,同时还可以为优化或特定应用定制而保持可配置。BittWare提供一系列的NVMe加速选项,包括NVMe-oF--请与我们联系以了解更多。

参考文献

- Burgener E. (2019).三家高性能存储互连NVMe over TCP供应商被评为IDC创新者。美联社新闻。2019年5月6日,从APNews.com检索。

- Gibb S. (2018).使用NVMe-over-Fabrics的FPGA加速器分解。SNIA。2019年7月1日,检索自SNIA.org

- Gupta R. (2018).什么是NVMe™,为什么它很重要?一个技术指南。西部数据博客。2019年6月24日,从Blog.WesternDigital.com检索。

- Hemsoth N. (2019).现有的存储基础设施是人工智能的瓶颈。Next Platform.2019年5月6日,从NextPlatform.com检索。

- Robinson D. (2019).VAST数据公司保证无停机,无数据丢失。Blocks & Files.2019年5月6日,从BlocksAndFiles.com检索。

- Rouse M. (2019).计算性存储。Tech Target.2019年6月24日,从SearchStorage.TechTarget.com获取。

- Weaver E. (2019).M&E现在需要NVMe的五大原因。媒体与娱乐服务联盟。2019年5月6日,从mesalliance.org检索。