백서

2D FFT 가속화

Stratix 10 MX에서 HBM2 및 oneAPI 사용

개요

알고리즘에 "코너 턴"이 포함될 때 HBM2 메모리가 있는 FPGA가 GPU 칩보다 빠릅니다. 이는 FPGA가 코너 턴 연산을 계산과 겹칠 수 있어 지연 시간 측면에서 "자유롭기" 때문입니다. 2D FFT를 사용하여 이 기술을 시연하고 아래 소스 코드를 제공합니다. "공정성"을 유지하기 위해 이 코드는 GPU에서도 지원하는 데이터 유형을 사용합니다. FPGA는 모든 데이터 유형을 쉽게 처리할 수 있습니다.

비트웨어는 이전에 인텔의 OpenCL 컴파일러를 사용하여 FPGA용 2D FFT 커널을 만들었습니다. 이제 이 코드를 다시 작성하여 인텔의 oneAPI 프로그래밍 모델, 특히 DPC++ 프로그래밍 언어를 활용했습니다. 520N-MX 카드에서도 비슷한 성능을 달성했습니다. 인텔은 GPU 또는 FPGA 가속이 필요한 애플리케이션을 위한 최고의 툴체인으로 oneAPI를 홍보하고 있습니다.

2D FFT를 구현한 이유는 무엇인가요?

2D FFT는 FPGA IP 라이브러리에서 흔히 볼 수 있으므로 프로그래머가 일반적으로 직접 구현하는 것은 아닙니다. 그러나 병렬 하드웨어에서 2D FFT를 구현하는 일반적인 전략에는 CPU와 GPU에서 주요 성능 병목 현상을 일으키는 '코너 턴' 또는 '데이터 전치' 단계가 포함됩니다.

무료 코너 회전

이 데모에서 강조하는 인사이트는 FPGA 구현이 계산과 병렬로 데이터 전치를 수행할 수 있어 지연 시간 측면에서 거의 '무료'라는 점입니다.

GPU 아키텍처는 HBM2/GDDR6 메모리를 건드리지 않고 중간 결과를 파이프라인화할 수 있는 충분한 메모리가 GPU 내부에 없기 때문에 동일한 작업을 수행할 수 없습니다.

oneAPI를 사용하여 FPGA에서 HBM2 사용

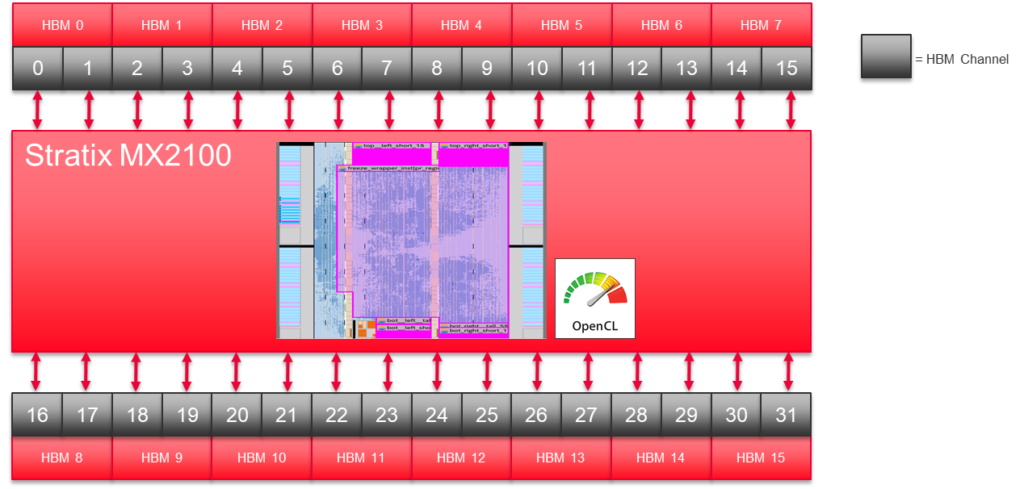

Stratix 10 MX에는 32개의 의사 HBM2 메모리 채널이 있습니다. 유니티의 2D FFT 구현은 이 채널의 절반을 사용합니다.

Stratix 10 MX에는 32개의 의사 HBM2 메모리 채널이 있습니다. 유니티의 2D FFT 구현은 이 채널의 절반을 사용합니다.

- 칩에 두 개의 2D FFT 커널을 배치할 수 있습니다. 한 커널은 칩의 북쪽에 있는 모든 의사 채널 인터페이스를 사용합니다. 다른 하나는 남쪽의 채널을 사용합니다.

- 단일 2D FFT에서 32개 채널을 모두 사용하려고 하면 데모 코드에서 다루고 싶지 않은 라우팅 문제가 발생합니다.

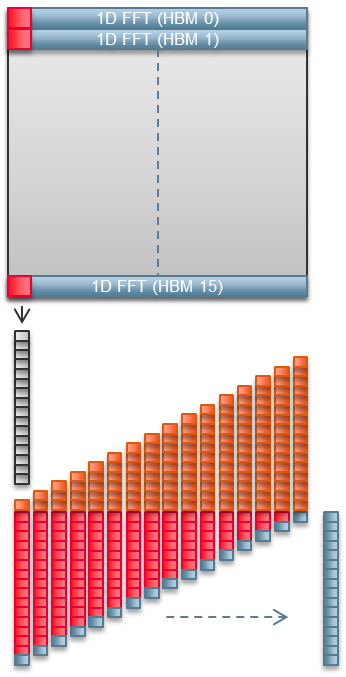

FPGA HBM2 채널당 1열

2D FFT는 여러 개의 1D FFT를 사용하여 구현됩니다. 단일 1D FFT는 사용하는 HBM2 채널을 포화시킵니다. 16개의 HBM2 채널로 2D FFT를 구현하면 1024행 매트릭스의 16행이 병렬로 처리됩니다. 하이엔드 GPU는 아마도 1024 행을 모두 한 번에 처리할 수 있을 것입니다. FPGA는 64개의 패스가 필요합니다. 그러나 두 경우 모두 HBM2/GDDR6 대역폭이 제한 요소이므로 패스 수는 중요하지 않습니다.400MHz Fmax면 충분합니다

최적의 32바이트 버스트를 수행하는 각 HBM2 채널을 포화 상태로 만들려면 400MHz OpenCL 클럭 주파수가 필요합니다. 더 빨라지는 것은 가치가 없습니다. 느리게 가는 것도 최적이 아닙니다. 인텔의 현재 DPC++ 구현은 비트웨어의 기존 OpenCL 보드 지원 패키지를 활용합니다. 따라서 두 구현 모두 FPGA에 대한 OpenCL처럼 보입니다. 두 구현 모두 400MHz를 달성하기 위해 동일한 조정이 필요합니다. 이러한 조정은 소스 코드에서 다르게 표현될 뿐입니다.1D FFT 출력

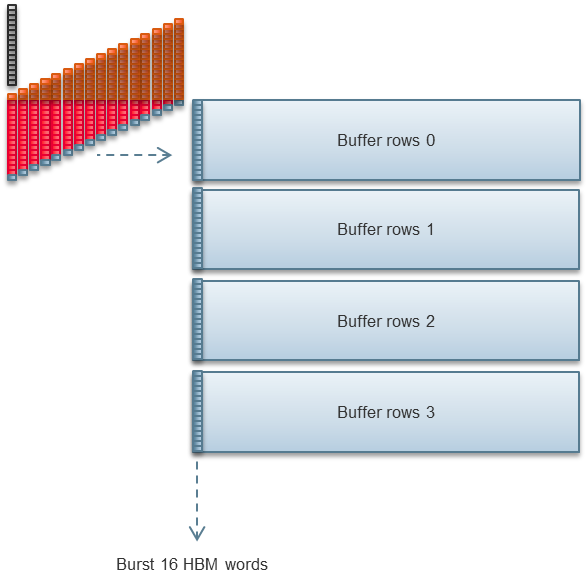

1D FFT는 결과를 HBM2로 직접 출력하지 않습니다. 대신 FPGA 내부 메모리에 기록합니다. 추가 FPGA 로직은 여러 1D FFT의 결과를 수집하고, 그 결과를 코너링한 후 계산과 병행하여 HBM2에 다시 씁니다.1D FFT 지연 시작

16개의 1D FFT를 동일한 클록 주기로 시작하지 않습니다. 대신 시작 지점을 각각 하나의 복잡한 요소씩 엇갈리게 배치합니다. 이렇게 하면 1D FFT 결과를 코너 턴 로직으로 파이프라인화할 수 있습니다.

32바이트 버스트

전치된 데이터를 32바이트 청크로 HBM에 쓰기 위해서는 4개의 1D FFT가 출력될 때까지 기다려야 합니다.

oneAPI를 사용한 프로그래밍의 용이성

BittWare의 개발팀은 RTL(Verilog 및 VHDL), HLS(대부분 C++), OpenCL, 그리고 현재 DPC++를 사용하고 있습니다. 이전에 RTL과 HLS를 비교하는 백서를 발행한 적이 있습니다. 이 프로젝트는 OpenCL과 DPC++를 비교하는 첫 번째 기회였습니다.

FPGA용 OpenCL 코드에서 FPGA용 DPC++로 쉽게 전환할 수 있었다는 점을 기쁘게 생각합니다. FPGA와 HBM2 온-패키지 메모리에 특화된 적응은 OpenCL 버전과 매우 유사했습니다. 호스트 컴퓨터에서 데이터 이동도 간단했습니다. 심지어 OpenCL 버전에서는 한 번도 시도하지 않았던 2D FFT 커널을 NumPy에서 호출하기도 했습니다.

FPGA 가속을 위한 oneAPI 개요 비디오

추가 세부 정보

내부 메모리 여유 공간

512개의 M20K 메모리(MX2100의 12.5%)를 사용하고 있습니다.

2D FFT 파라미터

FPGA에 구현되는 FFT의 길이는 일반적으로 비트스트림 컴파일 시간에 설정됩니다.

- 이 데모에서는 복잡한 32비트 부동 소수점 숫자로 구성된 1024×1024 고정 행렬을 사용합니다.

- FFT 구현은 복소수의 구성 요소를 인터리빙합니다(별도의 실수 행렬과 허수 행렬을 사용하는 것과는 대조적으로).

- 데이터가 HBM 메모리로 복사되어 32바이트 정렬이 되므로 정렬은 크게 중요하지 않습니다.

1D FFT 구현

(다른 사람의 FPGA IP 라이브러리를 사용하는 대신) 자체적으로 1D FFT를 구현했습니다. 1D FFT는 기수 2이며 완전히 파이프라인화되어 있습니다. 제자리에 있지 않습니다.

성능

2D FFT 성능은 항상 HBM2 대역폭에 의해 제한됩니다. 따라서 우리는 HBM2 대역폭을 최대화할 수 있는 알고리즘을 찾는 데 초점을 맞추고 있습니다. 이는 또한 HBM2 대역폭 벤치마크를 사용하여 FFT 성능을 정확하게 추정할 수 있다는 의미이기도 합니다.

동일한 디바이스에서 두 개의 독립 커널을 사용하는 배치 1 구현의 최대 HBM2 성능은 초당 291GBytes입니다. 파이프라이닝/배치 시 최대 대역폭은 초당 337GBytes가 가능합니다.

결론

2D FFT를 OpenCL 버전에서 oneAPI로 빠르게 포팅할 수 있게 되어 기뻤습니다. HBM2 지원 FPGA 카드에 대한 접근 방식을 최적화하는 작업은 이미 완료되었지만, OpenCL 기반 사용자가 최소한의 영향만으로 BittWare 하드웨어에서 oneAPI로 전환할 수 있는 훌륭한 경로를 제공합니다.

FPGA에서 HBM2를 사용하면 여기에서 살펴본 것과 같은 특정 애플리케이션에서 몇 가지 중요한 이점을 얻을 수 있습니다. 제시된 코드에 대한 자세한 정보가 필요하신 경우 아래 양식을 통해 문의하여 구입 가능 여부를 문의하거나 BittWare의 520N-MX FPGA 카드에 대해 자세히 알아보시기 바랍니다.

소스 코드 요청하기

이 양식을 작성하여 오픈 소스 TAR 파일을 요청할 수 있습니다. 받게 될 코드에는 오픈 소스 범례가 포함되어 있습니다.

코드 사용 방법:

OneAPI 2D FFT를 Linux 동적으로 연결된 공유 객체 라이브러리로 컴파일합니다. "cmake ."를 입력하면 해당 라이브러리가 생성됩니다.

간단한 NumPy 스크립트에서 해당 라이브러리를 호출하여 일부 입력 데이터를 생성한 다음 출력의 유효성을 검사하거나 플롯합니다. 그래프를 보려면 "python runfft.py"를 입력하세요.

위의 소프트웨어는 MX2100 FPGA를 호스팅하는 BittWare 520N-MX 카드를 사용하여 Centos 8에서 인텔 OneAPI 도구 베타 10 릴리스와 함께 테스트되었습니다. 해당 카드에 대해 릴리스된 OpenCL 보드 지원 패키지를 사용하면 OneAPI도 작동할 수 있습니다.

"*"는 필수 필드를 나타냅니다.