동적 신경 가속기

ML 프레임워크

엣지코어텍스 동적 신경 가속기(DNA)는 높은 컴퓨팅 성능, 초저지연, 확장 가능한 추론 엔진을 갖춘 딥 러닝 추론을 위한 유연한 IP 코어로, Agilex FPGA를 탑재한 BittWare 카드에 탑재되어 있습니다.

스트리밍 및 고해상도 데이터(배치 크기 1)를 사용한 추론에 특별히 최적화된 DNA는 특허받은 재구성 가능한 IP 코어로, EdgeCortix의 MERA™ 소프트웨어 프레임워크와 결합하여 점점 더 복잡해지고 컴퓨팅 집약적인 오늘날의 AI 워크로드를 원활하게 가속화하는 동시에 90% 이상의 배열 활용률을 달성할 수 있도록 지원합니다.

통합 컴파일 라이브러리와 런타임을 제공하는 MERA 프레임워크로 보완된 이 전용 IP 코어를 통해 소프트웨어 엔지니어는 파이토치 및 텐서플로우와 같은 표준 프레임워크에서 벗어나지 않고도 표준 CPU 또는 GPU의 드롭인 대체품으로 비트웨어 IA-840f 및 IA-420f FPGA 카드를 사용할 수 있습니다. Agilex용 DNA 비트스트림은 스트리밍 데이터에 대한 추론 지연 시간을 현저히 낮추고 경쟁 FPGA에 비해 2배에서 6배의 성능 우위를 제공하며 다른 범용 프로세서에 비해 전력 효율성이 우수합니다.

통합 컴파일 라이브러리와 런타임을 제공하는 MERA 프레임워크로 보완된 이 전용 IP 코어를 통해 소프트웨어 엔지니어는 파이토치 및 텐서플로우와 같은 표준 프레임워크에서 벗어나지 않고도 표준 CPU 또는 GPU의 드롭인 대체품으로 비트웨어 IA-840f 및 IA-420f FPGA 카드를 사용할 수 있습니다. Agilex용 DNA 비트스트림은 스트리밍 데이터에 대한 추론 지연 시간을 현저히 낮추고 경쟁 FPGA에 비해 2배에서 6배의 성능 우위를 제공하며 다른 범용 프로세서에 비해 전력 효율성이 우수합니다.

최대 20 TOPS @ 400MHz

INT8 추론

(FP32의 99%

정확도)

50개 이상의 모델 테스트 MERA 프레임워크

엣지에서의 AI 추론

알테라 개요 비디오

비디오 데모

동적 신경 가속기에 대해 에지코틱스 CEO 사캬 다스굽타의 이야기를 들어보세요.

마커스 웨들, 비트웨어

안녕하세요, BittWare의 Marcus입니다. 오늘은 엣지코틱스의 머신러닝 프레임워크에 대해 논의할 예정이지만, 시작하기 전에 약간의 배경 지식을 알려드리고 싶었습니다.

오늘날 거의 모든 곳에서 인공 지능에 대해 이야기하는 것을 볼 수 있지만, 사실 이러한 추세는 지난 10년 동안에야 시작되었습니다. 인공지능을 사용한다는 아이디어는 이보다 훨씬 오래된 것 같은데, 그렇다면 이러한 트렌드가 시작된 이유는 무엇일까요? 정답은 하드웨어 가속, 특히 GPU와 FPGA, 그리고 최근에는 전용 ASIC입니다. 이러한 장치는 새로운 기술과 상업용 애플리케이션을 개발하는 연구자들이 수요를 창출할 수 있는 AI 분야를 실제로 열었습니다.

그리고 가장 흥미로운 점은 AI 기술, 하드웨어 기능, 사용 사례 확장이라는 긴 성장 곡선의 한가운데에 있을 뿐이라는 점입니다.

즉, AI는 거대한 주제이므로 오늘은 클라우드나 데이터센터 환경 외부의 사용 사례인 엣지에서의 머신 러닝에 초점을 맞추고 있습니다.

앞으로 살펴보겠지만 엣지 디바이스에서는 효율성이 매우 중요합니다. 엣지코어틱스는 워크로드에 맞게 조정할 수 있는 FPGA의 고유한 장점과 무엇보다도 재교육이 필요 없는 적응성이 뛰어난 소프트웨어를 활용하여 이러한 부분에 집중하고 있습니다.

이 자리에는 에지코어틱스의 창립자이자 CEO인 사캬 다스굽타(Sakya Dasgupta)가 함께했습니다. 환영합니다!

Sakya Dasgputa, 박사, EdgeCortix 설립자 겸 CEO

감사합니다, Marcus는 여러분과의 대화를 고대하고 있습니다.

Marcus

예를 들어 클라우드나 데이터센터에서 모든 ML 추론을 수행하지 않는 이유는 무엇일까요? 굳이 엣지에서 할 필요가 있을까요?

Sakya

당연하죠. 따라서 머신 러닝 추론 솔루션을 배포하는 데 클라우드나 데이터 센터만 사용하는 것은 5가지 주요 과제로 인해 크게 제한됩니다.

이를 클라우드에서 정보를 처리하는 데 필요한 비용으로 세분화할 수 있습니다. 두 번째는 전력 또는 전력 효율 또는 에너지 효율이라고 부르는 것입니다. 셋째, 가장 큰 문제는 모델 측면입니다. 이러한 신경망 자체의 복잡성입니다.

네 번째 중요한 과제는 클라우드에서 정보를 보존하고 처리하려는 데이터의 프라이버시와 관련된 것입니다. 그리고 근본적으로 지연 시간이나 대역폭에 대한 제한이 있습니다.

이제 이를 조금 더 세분화해 보겠습니다.

비용

비용 측면에서 보면, 순수 클라우드 네이티브 솔루션은 컴퓨팅뿐만 아니라 대량의 데이터를 저장하는 데에도 많은 비용이 발생한다는 한계가 있습니다. 그리고 대부분의 경우 페타바이트 단위의 데이터에 대해 이야기하고 있습니다.

엣지를 살펴보면, 머신 러닝에 흥미로운 데이터라고 할 수 있는 거의 모든 데이터의 75%가 클라우드에 직접 저장되어 있으며, 이러한 엣지 디바이스 또는 엣지 서비스라고 부르는 것과 거의 비슷합니다. 따라서 이러한 데이터를 모두 클라우드로 옮긴 다음 처리하고 계산하는 것은 엄청난 비용 문제가 됩니다.

전력 효율성

클라우드에 있는 대부분의 시스템이 전력 소비량이 킬로와트 수준이고 머신 러닝이나 AI 추론 자체가 많은 컴퓨터 리소스를 소비한다는 점에서 전력 및 전력 효율성은 병목 현상이 됩니다.

모델 복잡성

앞서 언급했듯이 모델은 매우 복잡하기 때문에 대부분의 모델은 클라우드에서 학습되었습니다. 따라서 기본적으로 복잡한 모델을 엣지로 가져가려고 하면 해당 디바이스의 제한된 리소스 측면에서 병목 현상이 발생합니다. 따라서 순수한 클라우드 기반 배포를 고려하는 경우에는 적합하지 않습니다.

개인 정보 보호

그리고 근본적으로 모든 데이터를 엣지에서 가까운 곳으로 옮겼다가 다시 클라우드로 옮기는 경우, 예를 들어 의료 애플리케이션이나 기타 유사한 시나리오에서 데이터의 프라이버시가 손실될 가능성이 있습니다.

지연 시간

그리고 근본적으로 대량의 데이터를 이동하고 이 모든 것을 클라우드에서 처리하는 데에는 많은 지연 시간이 발생합니다. 대부분의 실시간 애플리케이션은 7~10밀리초 미만의 처리 시간을 필요로 합니다. 따라서 거의 모든 실시간 요구 사항 애플리케이션에 대해 순수 클라우드 네이티브 솔루션을 사용한다면 이는 큰 문제가 될 수 있습니다.

이러한 이유로 클라우드 기반 솔루션으로만 머신러닝을 제한하는 것은 이상적인 시나리오가 될 수 없습니다.

Marcus

네, 그 말이 맞습니다. 배포 플랫폼 중 하나로 FPGA로 범위를 좁힌 방법, 즉 공동 탐색이라는 프로세스를 사용하셨다는 글을 읽었습니다.

그리고 엣지 추론에 적합한 FPGA의 구체적인 이점에 대해 설명해 주시겠습니까?

Sakya

물론 좋은 질문입니다. 머신 러닝 추론, 특히 심층 신경망을 살펴볼 때 FPGA 자체는 완전한 유연성이라는 큰 이점을 제공합니다. 여러 계층으로 구성된 신경망을 보면 하드웨어 플랫폼의 동작을 완전히 변경할 수 있고, 신경망의 단일 계층 내에서도 많은 이질성이 있을 뿐만 아니라 서로 다른 네트워크 간에 비교하는 경우에도 마찬가지입니다.

둘째, 거의 모든 신경망 연산은 CPU의 경우처럼 중앙에서 제어되지 않습니다. 폰 노이만 방식이 아니라 데이터 흐름 그래프로 가장 잘 표현할 수 있는 여러 수준의 병렬성을 포함하고 있습니다.

결과적으로 공동 설계 또는 공동 탐색이라고 하는 이러한 접근 방식은 일반적인 신경망 또는 심층 신경망의 정확도 요구 사항과 지연 시간, 메모리, 전력과 같은 관심 있는 하드웨어 메트릭 간의 균형을 맞추기 위해 노력하며, 이러한 고유한 병렬성을 활용하도록 프로세서 아키텍처를 실제로 맞춤화할 수 있으므로 대부분의 경우 하드웨어의 전체 활용도를 훨씬 더 효과적으로 높일 수 있게 해줍니다. 특히 GPU나 CPU와 같은 범용 프로세서와 비교한다면 더욱 그렇습니다.

그래서 저희는 이러한 접근 방식을 채택하여 동적 신경 가속기 IP와 MERA 소프트웨어를 공동 설계 방식으로 설계했습니다.

또한 근본적으로 동일한 접근 방식을 사용하면 이러한 다양한 모델의 높은 정확도를 유지하는 데 필요한 정보를 처리하는 정밀도 또는 해상도 사이의 균형을 맞추는 동시에 모델의 메모리 풋프린트를 줄여 FPGA 칩의 제한된 메모리 용량에 최적으로 맞출 수 있습니다. 이것이 바로 우리가 INT8 비트를 결정한 이유이며, 정확도를 원래와 비슷하게 유지하면서 추론을 최적으로 수행할 수 있을 뿐만 아니라, 온보드에 직접 필요한 메모리 양을 최적화하고 FPGA에서 칩 밖으로 나가는 데이터 전송량에 제약을 받지 않도록 작업을 제한하는 절충안으로 삼았습니다.

결과적으로 전반적으로 FPGA는 이러한 공동 설계 또는 공동 탐색 프로세스를 통해 프로세서 설계를 조정할 수 있는 유연성과 이러한 컴퓨팅 효율성을 제어하는 것 사이에서 좋은 균형을 제공합니다.

Marcus

워크로드가 변화하거나 다른 하드웨어 기능에 전용 DSP 블록이 포함될 수 있기 때문에 향후 INT8에서 멀어질 수 있을까요?

Sakya

네, 물론이죠. 이 프로세스를 시작할 때만 해도 INT8 비트 표현이 현재 지원하는 유일한 정밀도가 아니었다는 것을 알고 계셨을 겁니다. 기본적으로 부동 소수점 16, INT8 비트 등 다양한 범위의 정밀도를 지원하는 아키텍처가 있으며, 신경망의 가중치나 매개변수에 대한 표현과 활성화를 저장하는 데 사용하는 정밀도에 따라 달라질 수 있습니다.

기본적으로 이 공동 디자인 프로세스는 배포 단계 내내 계속되는 살아있는 프로세스입니다.

기본적으로 공동 설계를 수행하는 경우 프로세서 아키텍처를 더 이상 변경할 수 없습니다. 그러나 예를 들어 신경망 모델이 변경되거나 업데이트가 발생하는 경우에도 정확도, 지연 시간 요구 사항에 더 잘 맞도록 프로세서 아키텍처의 특정 측면을 재설계할 수 있습니다.

이전 질문으로 돌아가서 FPGA의 장점은 원하는 경우 프로세서 아키텍처를 유연하게 변경할 수 있다는 점입니다. 반면 ASIC이나 다른 유형의 하드웨어는 한 번 제작하거나 제조하면 완전히 고정되어 있기 때문에 더 이상 그런 수준의 유연성을 확보할 수 없습니다.

Marcus

이제 구체적인 하드웨어에 대해 이야기해 보겠습니다. 비트웨어는 인텔 애질렉스 기반 카드에서 사용할 수 있는 프레임워크로서 엣지코어텍스 IP와 소프트웨어를 함께 제공합니다. Agilex의 성능과 확장된 PCIe Gen4 대역폭의 이점에 대해 설명해 주시겠어요?

Sakya

물론이죠. 저희의 AI 가속 IP와 새로운 인텔 애자일렉스 카드를 결합하면 많은 이점이 있습니다. 특히 두 가지 폼 팩터인 비트웨어 더블 와이드 FPGA 카드와 로우 프로파일 FPGA 카드를 지원한다는 점을 고려하면, 사용자가 컴퓨팅, 전력, 비용 사이에서 이상적으로 선택할 수 있으며, 특히 TeraBox 서버와 번들링하는 경우 더욱 그렇습니다. 이를 통해 특히 엣지 애플리케이션에 요구되는 까다로운 열악한 환경에서도 FPGA 가속을 배포할 수 있습니다.

기본적으로 인텔 애자일렉스는 인텔의 최신 세대 실리콘입니다. 이러한 각 FPGA는 중요한 FPGA 리소스와 전력을 절약하는 강화된 PCIe 프로토콜을 지원하며, 이는 AI가 다른 유형의 FPGA 가속과 공존하는 많은 애플리케이션에 매우 중요할 수 있습니다.

인텔 애질렉스도 살펴보면 2세대 하이퍼플렉스 아키텍처를 기반으로 합니다. 이를 통해 강화된 DSP 블록이 제공되어 수천 개의 INT8 오퍼레이터를 장착할 수 있고 IP를 쉽게 확장할 수 있는 통합 구조가 가능합니다.

또한, 이러한 FPGA 카드의 PCIe Gen 4 지원은 기본적으로 이전 세대인 PCIe Gen 3에서 사용할 수 있는 대역폭에 비해 30% 이상 개선된 성능을 제공합니다. 이는 머신 러닝 추론에 매우 큰 영향을 미칠 수 있는데, 주로 호스트에서 FPGA로 고해상도 데이터를 자주 주고받는 머신 러닝 추론에 매우 큰 영향을 미칩니다. 따라서 더 많은 대역폭을 사용할 수 있게 되면 오히려 속도가 빨라져 전반적인 효율성이나 성능에 큰 영향을 미칠 수 있습니다.

그리고 근본적으로 DDR4 지원 측면에서 사용할 수 있는 메모리 용량도 충분히 많습니다. 최대 128기가바이트에 달하는 이중 폭 FPGA 카드를 살펴보면, 이러한 FPGA 자체의 비교적 많은 양의 온칩 BRAM과 결합하면 많은 애플리케이션에 매우 우수한 확장성 옵션을 제공할 수 있습니다.

전반적으로 인텔 애자일렉스를 살펴본 결과, 우리의 IP를 장착하면 최대 20조 개의 연산, 즉 20 TOPS의 전용 AI 컴퓨팅이 가능해져 현재 시장에 나와 있는 다른 경쟁 FPGA 가속 솔루션에 비해 이 카드에서 우리의 IP를 사용하여 6배 더 나은 성능 이점을 제공할 수 있다고 믿습니다.

Marcus

이제 BittWare 카드를 다른 솔루션과 비교한 그래프를 보겠습니다. 로우 프로파일 IA-420F 카드가 6~7배 더 우수하고 IA-840F는 그보다 훨씬 더 높습니다. 매우 인상적입니다. 이 차트에서 GPU를 볼 수 있는데, 현재 Agilex에서 20개의 TOPS를 사용하고 있다고 언급하셨는데, 과거에 GPU의 TOPS 활용 방식에 차이가 있다고 말씀하신 적이 있는 것으로 알고 있습니다. 그 차이는 정확히 무엇이며 단순히 TOPS를 명시하는 것 외에 성능을 더 잘 비교하려면 어떻게 해야 하나요?

Sakya

물론이죠. 그것도 좋은 질문입니다. 따라서 일반적으로 TOPS를 비교하면 FPGA 또는 모든 컴퓨팅 프로세서의 전반적인 성능을 완전히 대표하지는 않습니다.

예를 들어, 이 사례에서 두 개의 디바이스(이 경우 20 TOPS의 FPGA)를 예로 들면, DNA IP를 지원하는 20 TOPS BittWare FPGA와 20 TOPS의 GPU를 비교하는 것입니다.

기본적으로 GPU는 사용 가능한 컴퓨팅의 총량을 잘 활용하지 못합니다. 우리는 이를 활용률이라고 부릅니다.

대부분의 최신 GPU, 심지어 CPU도 사용 가능한 전체 연산 능력에서 최대 20%에서 30% 정도를 사용하고 있습니다.

따라서 TOPS가 20개라면 특정 시점에 그 중 20%가 활용된다는 점에서 실제로는 표면만 긁어모은 것에 불과합니다.

이제 이를 DNA IP 지원 FPGA와 비교해 보면, IP의 런타임 재구성 기능 덕분에 컴퓨팅의 거의 90%(이 경우 20개의 TOPS 중 90%가 특정 AI 워크로드 또는 애플리케이션에 활용되고 있습니다.)를 활용할 수 있게 됩니다.

그 결과, 효율(와트당 초당 프레임 수)은 동급의 GPU 또는 FPGA 솔루션에 비해 유니티 솔루션을 사용할 때 훨씬 더 높습니다.

Marcus

TOPS에 대해 설명해 주셔서 감사합니다. 이제 MERA 소프트웨어에 대해 이야기하고 싶었습니다. 말씀하신 것처럼 FPGA에서 실행되는 IP를 DNA라고 하는데, 이는 매우 높은 효율성을 제공하지만, MERA 소프트웨어 자체는 표준 프레임워크를 사용하고, 예를 들어 GPU에서 온 경우 재교육이 필요하지 않는 등 시간을 크게 절약할 수 있는 이점을 제공합니다. MERA의 이러한 소프트웨어 장점에 대해 자세히 설명해 주시겠어요?

TOPS에 대해 설명해 주셔서 감사합니다. 이제 MERA 소프트웨어에 대해 이야기하고 싶었습니다. 말씀하신 것처럼 FPGA에서 실행되는 IP를 DNA라고 하는데, 이는 매우 높은 효율성을 제공하지만, MERA 소프트웨어 자체는 표준 프레임워크를 사용하고, 예를 들어 GPU에서 온 경우 재교육이 필요하지 않는 등 시간을 크게 절약할 수 있는 이점을 제공합니다. MERA의 이러한 소프트웨어 장점에 대해 자세히 설명해 주시겠어요?

Sakya

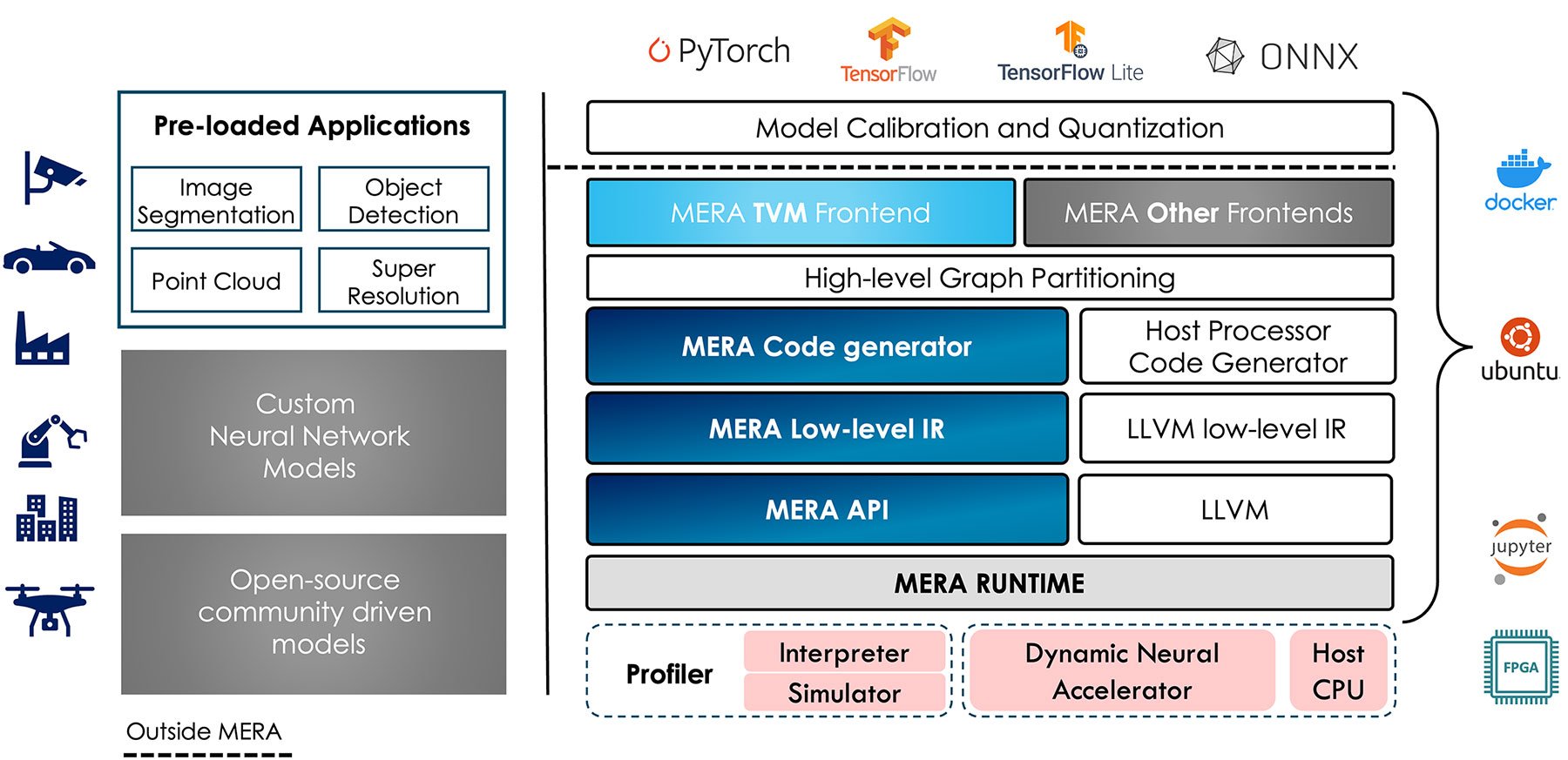

네, 맞습니다. 그래서 우리는 머신 러닝 엔지니어의 유연성을 염두에 두고 AI 가속을 위해 FPGA를 사용할 때 문제가 되었던 FPGA 관련 기술을 필요로 하지 않는 MERA 프레임워크를 설계했습니다.

결과적으로 MERA의 근본적인 장점 중 하나는 플러그 앤 플레이에 가까운 환경이라는 점입니다:

첫째, 이미 GPU에서 사전 학습된 기존 딥 뉴럴 네트워크 애플리케이션을 재학습이나 아키텍처 변경 없이 DNA IP가 지원되는 이 FPGA로 원활하게 이식할 수 있습니다.

둘째, MERA는 공개 PyPi 리포지토리를 사용하여 설치할 수 있으므로 기본적으로 pip에 액세스할 수 있는 사람이라면 누구나 다운로드할 수 있으며, 오히려 활성화된 경우 FPGA가 실행되는 장치에서 직접 MERA를 다운로드할 수 있고, 파이썬 또는 C++를 기본적으로 지원하며 Pytorch, TensorFlow 및 TensorFlow Lite와 같은 모든 주요 머신 러닝 프레임워크도 기본으로 지원할 수 있다는 뜻입니다.

셋째, 매우 인기 있는 딥 러닝 컴파일러인 오픈 소스 Apache TVM에 대한 지원도 내장되어 있습니다. 이를 통해 사용자는 선택한 머신 러닝 프레임워크 내에서 간단한 보정 및 정량화 단계를 거쳐 사전 학습된 딥 뉴럴 네트워크 모델을 배포할 수 있습니다.

기본적으로 IP별 모델, 정량화 또는 가지치기가 필요하지 않습니다.

이는 경쟁 솔루션이나 애플리케이션별 하드웨어뿐만 아니라 FPGA를 사용하는 다른 인프라에 비해 큰 장점입니다.

이러한 거의 모든 프로세스는 하드웨어에 따라 특정 수준의 미세 조정이 필요하므로, 이러한 완전한 측면을 제거함으로써 머신 러닝 엔지니어가 이미 GPU에서 작동하는 코드를 원활하게 전송할 수 있도록 훨씬 더 많은 자율성을 부여하고 있습니다.

넷째, 심층 신경망 운영자에 대한 다양한 지원이 있습니다. 따라서 대부분의 최신 DNN 또는 심층 신경망을 즉시 배포할 수 있습니다. 또한 사용자가 다양한 애플리케이션에서 사용할 수 있도록 사전 테스트를 거친 50개 이상의 모델 모음을 제공하고 있습니다.

다섯째, 내장된 시뮬레이터 인터프리터와 같은 프로파일링 도구도 제공되어 사용자가 실제로 솔루션을 FPGA 자체에 배포하지 않고도 매우 빠르게 성능을 테스트할 수 있습니다. 이를 통해 모델 정확도를 확인할 수 있을 뿐만 아니라 성능을 비교적 빠르게 예측할 수 있습니다.

이것이 바로 프레임워크로서 MERA의 장점 중 일부라고 할 수 있습니다.

Marcus

지금까지 하드웨어에 대해 알아보았습니다. 이제 소프트웨어에 대해 살펴보았습니다. 이제 몇 가지 사용 사례에 대해 살펴보겠습니다. 제가 흥미로웠던 몇 가지 사례를 소개해드리겠습니다. 첫 번째는 초해상도입니다. 초해상도란 무엇이며 EdgeCortix 프레임워크는 이를 통해 어떤 성능을 발휘하나요?

Sakya

초해상도란 이미지나 동영상 프레임의 해상도를 크게 높이거나 낮출 수 있는 기능을 말합니다.

예를 들어, 픽셀 밀도가 매우 작은 360p 정도의 해상도에서 4K와 같은 매우 높은 해상도로 이동하는 것을 말합니다. 이는 해상도를 크게 높이거나 그 반대로 해상도를 4K에서 360p로 낮추는 것과 같습니다.

이러한 해상도 간 이동 기능이 필요한 애플리케이션이나 대역폭을 보존하려는 애플리케이션에 적합합니다. 예를 들어 비디오로 특정 스트리밍 애플리케이션을 수행하는 경우 더 낮은 해상도로 내려가 데이터를 전송한 다음 사용자 측에서 해상도를 다시 가져와 대역폭을 보존하고 싶을 수 있습니다.

기존에는 초고해상도를 구현하기 위해 손실률이 매우 높은 고전적인 방법을 사용했습니다. 그 결과 이미지의 많은 정보 콘텐츠가 손실되어 매우 작은 해상도에서 고해상도로 전환할 때 픽셀화가 발생하게 됩니다.

이러한 이미지와 동영상에 대해 학습된 신경망을 사용하여 해당 정보 내용을 추정할 수 있으므로 대부분의 정보를 거의 무손실 상태로 보존할 수 있습니다.

결과적으로 이러한 외삽을 통해 기존의 비머신러닝 기반 방법에서 볼 수 있는 픽셀화 수준 없이도 많은 정보를 보존할 수 있습니다.

엣지코어틱스의 프레임워크의 경우, 이러한 비교적 복잡한 초고해상도 모델을 매우 높은 해상도로 FPGA에서 직접 실행할 수 있습니다.

그 결과, 작은 360p 또는 480p 해상도에서 밀리초 이내에 4K로 바로 전환할 수 있어 비디오 스트리밍 애플리케이션에 필요한 대용량의 데이터를 전송할 수 있습니다.

Marcus

훌륭하군요. AI의 새로운 애플리케이션에 적응할 수 있다는 것을 보여주는 좋은 예라고 생각합니다. 또 다른 흥미로운 사용 사례는 이미지 기반이 아닌 센서 데이터를 사용하는 것입니다. 무선 주파수 데이터를 실제로 지문으로 인식하여 위치나 기기 식별과 같은 것을 예측하는 데 AI를 사용할 수 있습니다. 작동 방식에 대해 자세히 알아보세요.

Sakya

흥미로운 질문입니다. 일반적으로 데이터가 생성되는 위치 또는 정보가 전송되는 위치의 출처를 식별해야 하는 애플리케이션은 국방 통신뿐만 아니라 소비자 애플리케이션에 걸쳐 여러 가지가 있습니다. 그리고 일반적으로 무선 주파수라고 부르는 것을 사용하여 이를 수행합니다. 사람에게 지문이 있는 것처럼 이제 무선 주파수를 캡처하여 데이터가 생성되는 위치에 대한 고유한 지문을 생성할 수 있습니다. 라우터일 수도 있고 휴대폰 기지국일 수도 있습니다. 또는 하나의 휴대폰일 수도 있습니다. 이제 이 모든 데이터를 가져와 이미지로 변환한 다음 심층 신경망(이 경우 컨볼루션 신경망)을 학습시켜 이러한 고유한 특징을 식별하고 대부분의 경우 해당 디바이스가 실제 디바이스인지 여부를 분류할 수 있습니다. 예를 들어, 알려진 디바이스라면 해당 정보의 출처가 어디인지 분류하거나 위치를 파악할 수도 있습니다.

FPGA에서 이러한 신경망을 수행하거나 실제로 처리할 수 있는 기능을 갖추면 신호가 생성되는 위치의 소스 인증은 물론 매우 구체적인 위치 파악이나 식별이 필요한 국방 또는 통신 분야뿐만 아니라 인프라 에지 전반에 걸친 다양한 유형의 애플리케이션에 적용할 수 있는 길이 열립니다.

따라서 확실히 성장하는 분야이며 국방 및 소비자 부문 모두에 걸쳐 많은 애플리케이션이 적용되고 있습니다.

Marcus

이렇게 새로운 사용 사례를 보게 되어 반갑습니다. 그래서 마지막 질문은 엣지 AI의 다음 단계는 무엇인가요? 하드웨어나 사용 사례가 변화하거나 등장함에 따라 공동 탐색의 반복이 계속될 것으로 보십니까? 엣지에서 유연성과 효율성 사이에서 어떻게 균형을 맞추고 계신가요?

Sakya

네, 좋은 질문이고 이 분야는 완전히 열려 있다고 생각합니다. 신경망을 공동 설계하는 것부터 시작해서 신경망이 실행될 하드웨어 플랫폼과 관련하여 이제 막 표면을 긁기 시작했을 뿐입니다. 특히 원래 질문으로 돌아가서 FPGA는 처음부터 제대로 설계하지 않으면 프로세서 아키텍처의 특정 측면을 미세 조정할 수 있는 적절한 유연성 기반을 제공합니다.

동시에 완전히 새로운 유형의 모델이 지속적으로 발명되고 있습니다. 이전에는 컨볼루션 신경망이 비디오와 이미지에 매우 인기가 많았습니다. 이제는 이러한 컨볼루션 모델과는 약간 다른 트랜스포머와 같은 모델이 등장했습니다. 따라서 특정 시점에 더 잘 작동하는 신경망과 실행될 하드웨어 플랫폼에 따라 서로 다른 세대의 신경망이 더 긴밀하게 통합되고 적합해지길 원할 것입니다.

모든 종류의 시나리오에 맞는 획일화된 솔루션을 원하지는 않을 것입니다. 신경망의 기능이나 병렬 처리 정도에 따라 이를 실행할 기판의 유연성이 매우 중요하기 때문입니다.

전반적으로 유연성과 효율성 사이의 트레이드오프는 오랫동안 지속되어 온 문제입니다. 특히 항상 리소스가 제한되어 있고, 전력의 제약이 있으며, 많은 경우 이동성의 제약이 있는 엣지에 대해 생각해 보면 성능을 높이기 위해 돌릴 수 있는 유일한 손잡이나 손잡이는 효율성 또는 리소스 관리입니다.

따라서 저는 이 공동 탐험의 모든 영역이 앞으로 더욱 성장할 것으로 예상합니다.

Marcus

많은 이야기를 나눠주셔서 정말 감사합니다.

Sakya

만나서 반가웠습니다. 고마워요.

Marcus

에지코틱스의 창립자이자 CEO인 사캬 다스굽타와의 대담을 시청해 주셔서 감사합니다.

제품 설명

DNA IP 코어의 일부인 EdgeCortix 딥러닝 컴퓨팅 엔진은 Bittware IA-840f 및 IA-420f 카드에 최적화되어 있으며 바로 사용할 수 있는 비트스트림으로 배송됩니다. EdgeCortix 솔루션 제품군은 공용 핍 리포지토리에서 설치할 수 있는 MERA™ 프레임워크와 함께 제공되므로 업계 표준 프레임워크로 개발된 표준 또는 맞춤형 컨볼루션 신경망(CNN)을 원활하게 컴파일하고 실행할 수 있습니다.

MERA는 통합 DNA 비트스트림을 사용해 심층 신경망 그래프를 컴파일하고 추론하는 데 필요한 컴파일러와 소프트웨어 툴 키트로 구성되어 있습니다. 오픈 소스 Apache TVM 컴파일러 프레임워크를 기본적으로 지원하며, 간단한 보정 및 양자화 단계를 거쳐 사전 훈련된 심층 신경망을 배포하는 데 필요한 도구, API, 코드 생성기 및 런타임을 제공합니다. MERA는 파이토치나 텐서플로우릿과 같은 딥 러닝 프레임워크에서 직접 모델을 정량화할 수 있도록 지원합니다.

특징

초저지연 AI 추론 IP 코어:

- 최대 24576 MAC 및 400MHz에서 비컨볼루션 연산을 위한 전용 벡터 엔진

- INT8 매개변수 및 활성화에 최적화된 데이터 흐름 배열 기반 아키텍처

- 특허받은 런타임 재구성 가능 인터커넥트

강력한 오픈 소스 MERA 소프트웨어 프레임워크:

- MERA 컴파일러 1.0은 다양한 형태의 병렬 처리를 활용하고 컴퓨팅 활용도를 극대화합니다.

- Pytorch 및 TensorFlow Lite 모델에 대한 기본 지원

- MERA 프레임워크에 내장된 프로파일러

- 오픈 소스 Apache TVM과 통합됨

데이터 시트 및 제품 세부 정보

자세한 기능 목록

다양한 운영자 지원:

- 표준 및 깊이별 컨볼루션

- 보폭 및 확장

- 대칭/비대칭 패딩

- 최대 풀링, 평균 풀링

- ReLU, ReLU6, LeakyReLU, H-Swish

- 업샘플링 및 다운샘플링

- 잔여 연결, 분할 등

GPU 드롭인 교체:

- Python 및 C++ 인터페이스

- PyTorch 및 TensorFlow-lite 지원

- 재교육 필요 없음

- 고해상도 입력 지원

INT8 비트 양자화:

- 교육 후 정량화

- 딥러닝 프레임워크에 내장된 퀀타이저 지원

- 높은 정확도 유지

FPGA 카드 주문 옵션

| IA-420F-0010 | EdgeCortix 기반 BittWare IA-420f 카드® 동적 신경 가속기 |

| IA-840F-0014 | EdgeCortix® 동적 신경 가속기 기반 BittWare IA-840f 카드 |

회사 소개

AI 추론을 위한 동급 최고의 효율성과 지연 시간을 제공하는 데 중점을 둔 소프트웨어 우선 접근 방식을 사용하는 에지-AI 중심의 팹리스 반도체 설계 회사입니다.

가격이나 자세한 정보가 궁금하신가요?

기술 영업팀에서 가용성 및 구성 정보를 제공하거나 기술 관련 질문에 답변해 드립니다.

"*"는 필수 필드를 나타냅니다.