阿克维尔

DPDK/AXI Aware Data Mover IP核

在 FPGA 逻辑和主机内存之间无缝传输数据,单向传输速度高达 60 GBytes/s(480 Gbps)。Arkville 在主机内存和 FPGA 结构逻辑之间提供了一个高吞吐量、低延迟的通道,从而卸载了 CPU 内核的使用,消除了内存拷贝,提高了整体效率。

通过PCIe Gen 5,速度高达480Gbps

以任何线速运行,最高可达400GbE

DPDK和AXI标准

特点

- 将服务器周期卸载到FPGA门上

- 将您基于FPGA的数据包处理解决方案快速推向市场

- 用DPDK和AXI标准证明你的GPP/FPGA应用的未来性

- 线路速率无关:可在任何线路速率下运行,包括 1/5/10/25/40/50/100/400 GbE

- 使用 Gen5 x16 接口,速度高达 480 Gbps 和 500 Mpps

- 与 FPGA 供应商无关的 RTL

- 支持 Intel/PSG 和 AMD/Xilinx FPGA 设备

- DPDK 23.11 中的开源 "net/ark "Arkville 驱动程序

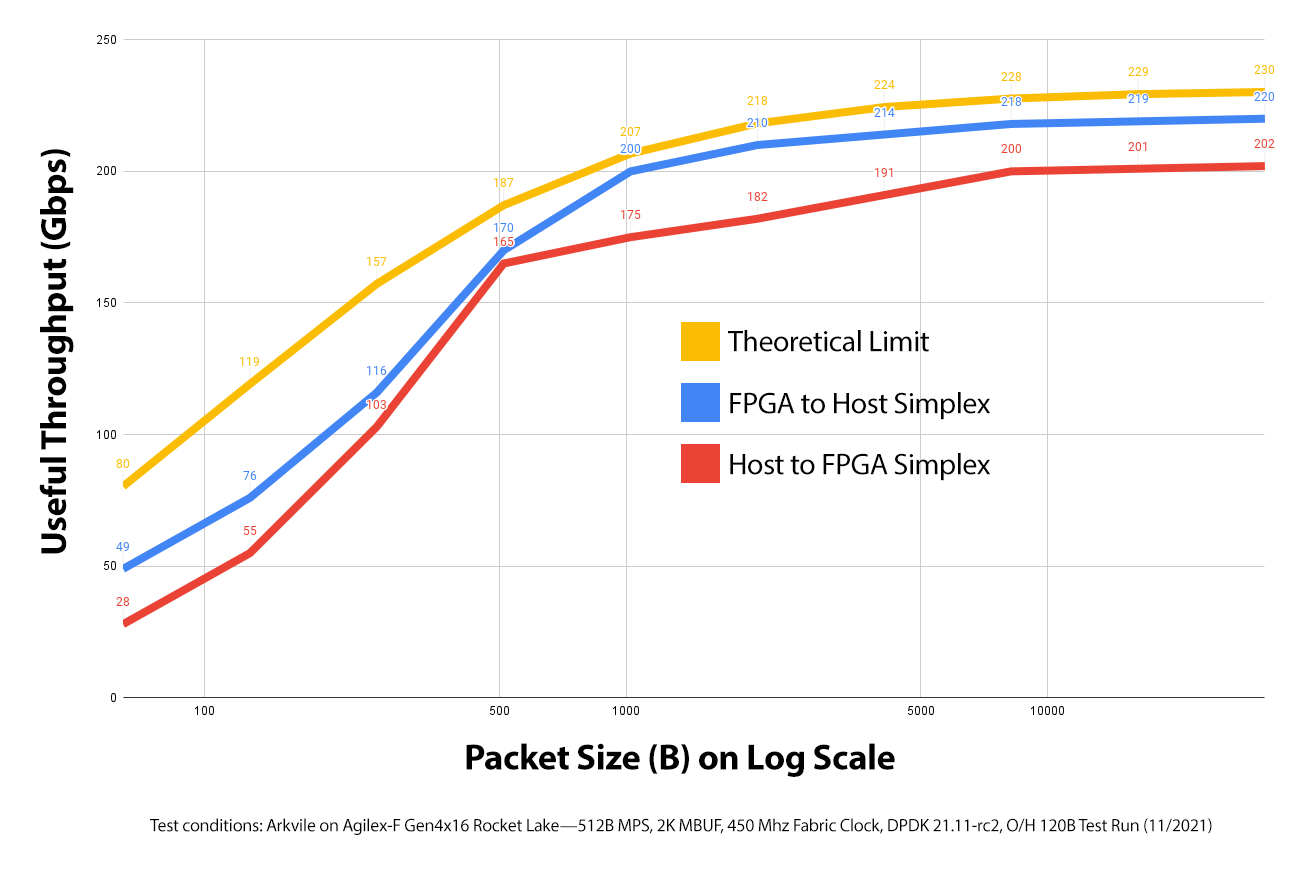

Arkville PCIe Gen4 x16的吞吐量(Gbps)。

视频

查看Arkville 17.05性能图的演示。

方框图、数据表和产品细节

产品操作

空标题

如框图所示,Arkville有硬件和软件两个部分。硬件组件是一个驻留在FPGA中的IP核,产生和消费AXI数据包流,使其进入或退出。软件组件是一个DPDK PMD "net/ark",即Arkville DPDK轮询模式驱动器。Arkville是FPGA逻辑和主机用户存储器之间的通道,用于批量数据移动或单个数据包。

总之,Arkville解决方案在软件上看起来就像一个 "普通的 "线速无关的基于FPGA的网卡(没有任何特定的MAC)。DPDK应用不需要做出重大改变,就能享受到FPGA硬件加速的优势。

空标题

空标题

详细功能列表

总的来说

- FPGA/GPP 数据包移动的即用型解决方案

- 标准配置为 4 个物理队列对(RX/TX);最多 128 个物理队列对

- 单个PCIe物理功能(PF)支持多个端口

- 并发、全双工上下行数据传输

GPP/软件专用

- DPDK 23.11 中的 DPDK Arkville PMD

- 使用 Jenkins CI/CD 进行了大量测试

- 用于 FPGA 应用的未支配应用 BAR (ABAR)

FPGA/硬件专用

- 用于数据包移动的AXI流接口

- 高达 1 Tbps 的突发流量(两个 128 字节宽、500 MHz、AXI 流)

- 用于 FPGA 应用的专用应用 BAR (ABAR) AXI4 主站

空标题

空标题

参考实例

Atomic Rules提供了Arkville示例设计,可以作为你自己解决方案的起点。这些例子包括:

- 四端口、四队列10 GbE实例(Arkville + 4×10 GbE MAC)。

- 单端口、单队列100GbE实例(Arkville + 1×100GbE MAC)。

实施结果样本

| 器材 | 速度 | 6LUTs | FFs | M20k | Fmax |

|---|---|---|---|---|---|

| 英特尔Agilex F系列 | -2 | 81K | 220K | 250 | 500 |

关于公司

为网络和时间质量提供FPGA IP组件和解决方案。IP产品包括Arkville数据转换器,用于主机存储器和FPGA结构逻辑之间的高吞吐量、低延迟的通信。

对价格或更多信息感兴趣?

我们的技术销售团队随时准备提供可用性和配置信息,或回答您的技术问题。

"*"表示必填项目