Arkville

DPDK/AXI 인식 데이터 무버 IP 코어

FPGA 로직과 호스트 메모리 간에 각 방향으로 최대 60GB/s(480Gbps)의 속도로 데이터를 원활하게 전송합니다. Arkville은 호스트 메모리와 FPGA 패브릭 로직 간에 처리량이 높고 지연 시간이 짧은 통로를 제공하여 CPU 코어 사용량을 오프로드하고 메모리 복사본을 제거하며 전반적인 효율성을 개선합니다.

최대 480Gbps, PCIe 5세대 지원

최대 400GbE의 모든 회선 속도에서 작동합니다.

DPDK 및 AXI 표준

특징

- 서버 사이클을 FPGA 게이트로 오프로드

- FPGA 기반 패킷 처리 솔루션의 신속한 시장 출시

- DPDK 및 AXI 표준으로 GPP/FPGA 애플리케이션의 미래 보장

- 회선 속도에 구애받지 않음: 1/5/10/25/40/50/100/400GbE를 포함한 모든 회선 속도에서 0퍼센트 작동합니다.

- Gen5 x16 인터페이스로 최대 480Gbps 및 500Mpps 지원

- FPGA 공급업체에 구애받지 않는 RTL

- 인텔/PSG 및 AMD/엑실링스 FPGA 디바이스 모두 지원

- DPDK 23.11의 오픈 소스 "net/ark" Arkville 드라이버

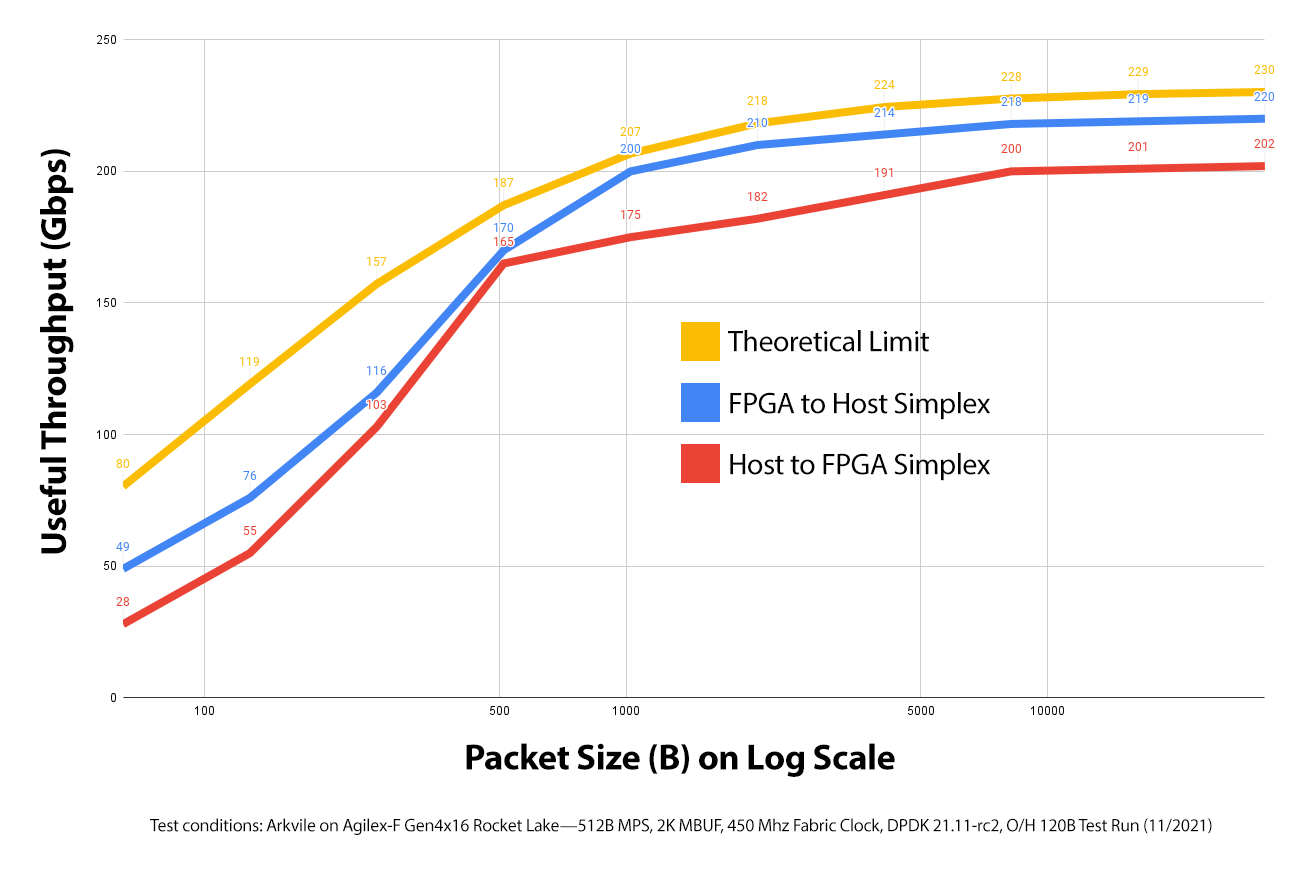

아크빌 PCIe Gen4 x16 처리량(Gbps)

비디오

아크빌 17.05 성능 플롯 데모 보기.

블록 다이어그램, 데이터 시트 및 제품 세부 정보

제품 운영

빈 제목

블록 다이어그램에서 볼 수 있듯이 아크빌은 하드웨어와 소프트웨어 구성 요소를 모두 갖추고 있습니다. 하드웨어 구성 요소는 FPGA에 상주하는 IP 코어로, 패킷의 AXI 스트림을 생성하고 소비하여 수신 또는 발신합니다. 소프트웨어 컴포넌트는 아크빌 DPDK 폴링 모드 드라이버인 DPDK PMD "net/ark"입니다. 아크빌은 대량 데이터 이동 또는 개별 패킷을 위한 FPGA 로직과 호스트 사용자 메모리 사이의 통로입니다.

아크빌 솔루션은 특정 MAC이 없는 "바닐라" 회선 속도에 구애받지 않는 FPGA 기반 NIC와 같은 소프트웨어로 보입니다. FPGA 하드웨어 가속의 이점을 누리기 위해 DPDK 애플리케이션을 크게 변경할 필요가 없습니다.

빈 제목

빈 제목

자세한 기능 목록

전체

- FPGA/GPP 패킷 이동을 위한 즉시 사용 가능한 솔루션

- 4개의 물리적 대기열 쌍(RX/TX) 표준, 최대 128개의 물리적 대기열 쌍

- 여러 포트를 지원하는 단일 PCIe 물리적 기능(PF)

- 동시 전이중 업스트림 및 다운스트림 데이터 이동

GPP/소프트웨어별

- DPDK 23.11의 DPDK 아크빌 PMD

- Jenkins CI/CD로 광범위하게 테스트 완료

- FPGA 애플리케이션을 위한 방해받지 않는 애플리케이션 바(ABAR)

FPGA/하드웨어별

- 패킷 이동을 위한 AXI 스트리밍 인터페이스

- 최대 1Tbps 버스트 트래픽(128바이트 폭, 500MHz, AXI 스트림 2개)

- FPGA 애플리케이션을 위한 전용 애플리케이션 바(ABAR) AXI4 마스터

빈 제목

빈 제목

참조 예제

아크빌은 자체 솔루션의 시작점으로 사용할 수 있는 아크빌 예제 디자인을 제공합니다. 여기에는 다음이 포함됩니다:

- 4포트, 4쿼터 10GbE 예시(아크빌 + 4×10GbE MAC)

- 단일 포트, 단일 대기열 100GbE 예시(아크빌 + 1×100GbE MAC)

샘플 구현 결과

| 장치 | 속도 | 6LUT | FF | M20k | Fmax |

|---|---|---|---|---|---|

| 인텔 애자일렉스 F-시리즈 | -2 | 81K | 220K | 250 | 500 |

회사 소개

네트워킹 및 시간 품질 향상을 위한 FPGA IP 구성 요소 및 솔루션 제공업체입니다. IP 제품에는 호스트 메모리와 FPGA 패브릭 로직 간의 높은 처리량, 짧은 지연 시간 통신을 위한 Arkville 데이터 무버가 포함됩니다.

가격이나 자세한 정보가 궁금하신가요?

기술 영업팀에서 가용성 및 구성 정보를 제공하거나 기술 관련 질문에 답변해 드립니다.

"*"는 필수 필드를 나타냅니다.