BittWare 웨비나

차세대 인텔® 애자일렉스™ FPGA를 통한 고성능 컴퓨팅

바르셀로나 슈퍼컴퓨팅 센터의 애플리케이션 예시 소개

이제 온디맨드 이용 가능(녹화된 Q&A 포함)

FPGA는 전력 효율성 및 특정 워크로드에 대한 적응성 등의 장점 덕분에 더 많은 고성능 컴퓨팅 애플리케이션에 도입되고 있습니다. 이 웨비나에서는 차세대 I-시리즈 및 M-시리즈 디바이스를 포함한 최신 인텔® 애자일렉스™ FPGA에 대해 집중적으로 다룹니다.

이번 웨비나의 특별 게스트로는 바르셀로나 슈퍼컴퓨팅 센터의 가속 프로젝트와 최근 발표한 논문에서 FPGA를 사용한 사례를 설명하는 세자르 곤잘레스(César González)가 참여합니다. 저분자 구조 규명에 대한 그의 연구는 OpenCL 하이레벨 프로그래밍을 활용했습니다. 세자르는 인텔의 마우리치오 파올리니와 함께 이 코드를 인텔 애자일렉스 FPGA가 탑재된 비트웨어 IA-840f 카드의 oneAPI로 포팅하여 233배의 속도 향상을 달성한 결과를 발표할 예정입니다.

또한 PCIe Gen5, CXL 및 HBM2e와 이러한 장치를 지원하는 BittWare 카드가 포함된 차세대 Agilex FPGA에 대해서도 살펴봅니다.

HPC 분야에서 일하고 계시거나 최신 FPGA가 어떻게 새로운 수준의 가속 성능을 제공하는지 관심이 있으신 분들은 이 웨비나에 꼭 참여하세요!

패널과의 녹화된 Q&A를 포함하여 온디맨드 방식으로 즉시 시청하세요!

스피커

Christian Stenzel | EMEA 기술 영업 전문가, 인텔

크레이그 페트리 | 마케팅 부사장, 비트웨어

마우리치오 파올리니 | 현장 애플리케이션 엔지니어 - 클라우드 및 엔터프라이즈 가속 사업부, EMEA, 인텔

세자르 곤살레스 | 바르셀로나 슈퍼컴퓨팅 센터, 카탈로니아 첨단 화학 연구소 - CSIC

비디오 대본

Marcus)

안녕하세요, "차세대 인텔 애자일렉스 FPGA를 이용한 고성능 컴퓨팅" 웨비나에 오신 것을 환영합니다. 바르셀로나 슈퍼컴퓨팅 센터의 애플리케이션 예시를 소개합니다. 저는 BittWare의 호스트 Marcus Weddle입니다.

발표자와 발표 내용을 소개하는 것부터 시작하겠습니다.

첫 번째 발표자는 인텔 출신의 Christian Stenzel입니다. 그는 자일링스에서 FAE부터 고객 관리 및 비즈니스 개발까지 다양한 직무를 수행하며 16년간 경력을 쌓았고, 2015년에 알테라에 합류했습니다. 인텔 인수 이후에는 클라우드 및 엔터프라이즈 기술 영업 전문가로 자리를 옮겨 EMEA 클라우드 및 엔터프라이즈 시장에서 인텔 FPGA 가속화 전략을 추진했습니다. Christian은 왜 HPC용 FPGA가 필요한지부터 설명합니다. 그리고 인텔 애질렉스 디바이스 제품군에 대해서도 소개할 예정입니다.

다음은 비트웨어의 크레이그 페트리입니다. 엔지니어로 시작해 제품 관리 및 전략을 이끌고 현재 영업 및 마케팅 부사장으로 재직 중인 크레이그는 FPGA 분야에서 수십 년의 경력을 쌓았습니다. 크레이그는 Agilex FPGA가 탑재된 BittWare의 제품, BittWare의 새로운 파트너 프로그램인 oneAPI에 대한 지원, 그리고 CXL에 대한 소개로 강연을 마무리할 예정입니다.

HPC 애플리케이션 섹션에서는 인텔의 FAE인 마우리치오 파울리니와 특별 초청 연사인 세자르 곤잘레스가 두 명의 발표자로 나서게 됩니다. Cesar는 바르셀로나 슈퍼컴퓨팅 센터에서 FPGA를 사용한 작업의 애플리케이션 측면을 설명하고, Maurizio는 최근 Agilex의 BittWare 카드에 대한 Cesar의 애플리케이션을 oneAPI로 포팅한 것을 포함하여 oneAPI에 대한 자세한 내용을 설명할 것입니다.

라이브 세션 중 하나를 시청 중이신 경우 질문 기능을 사용하여 질문하시면 마지막에 패널에게 질문이 전달될 것입니다.

자, 이제 인텔의 크리스티안 스텐젤과 함께 시작하겠습니다!

(기독교인)

오늘 초대해 주셔서 감사합니다. 먼저 인텔 법적 고지 사항을 알려드리고자 합니다. 이 고지 사항은 편한 시간에 읽어보실 수 있습니다.

이제 고성능 컴퓨팅에 대해 이야기해 보겠습니다. HPC는 광범위한 시장이며 가장 큰 것뿐만 아니라 가장 작은 것에 대한 이해를 높이는 데 사용됩니다. 우주 탐사, 청정 에너지 연구, 날씨 및 기후 모델링부터 양자 물리학, 생물 정보학, 분자 역학, 핵 연구 등에 이르기까지 다양한 분야에서 활용되고 있습니다.

연구자와 과학자들은 점점 더 많은 양의 데이터로 인해 더 복잡한 문제에 직면하고 있으며, 데이터를 처리하고 시뮬레이션을 실행하기 위해 더 많은 컴퓨팅을 요구하고 있습니다. 다시 말해, HPC 고객들은 성능 경쟁에 뛰어들고 있습니다.

일반적인 HPC 데이터센터에서는 CPU를 기본 옵션으로 사용하여 계산을 실행하고, 병렬 문제를 위한 최고의 가속기인 GPU를 함께 사용합니다. 이제 FPGA는 CPU와 GPU가 잘 처리하지 못하는 문제를 해결하기 위해 HPC 시스템을 보완하는 세 번째 요소이며, 항상 FPGA에서 가장 잘 실행되는 워크로드가 있습니다.

역사적으로 FPGA는 프로그래밍하기 어려웠고, 특별한 RTL 프로그래밍 기술이 필요했습니다. 마우리치오가 세션 후반부에서 oneAPI를 통해 RTL 기술 없이도 FPGA 프로그래밍이 가능한 방법에 대해 설명합니다.

FPGA의 고유한 기능을 살펴보겠습니다.

앞서 언급했듯이 HPC에서는 성능이 매우 중요합니다. 데이터 처리 방식이나 특정 알고리즘을 아키텍처에 맞게 조정해야 하는 거의 고정된 아키텍처를 가진 CPU나 GPU와 달리, FPGA는 완전한 유연성을 제공합니다. 내부 FPGA 하드웨어 아키텍처는 관심 있는 알고리즘에 가장 적합하도록 구축("구성"이라고 표현)할 수 있으므로 지연 시간은 짧고 성능은 높습니다. 예를 들어, 이더넷 회선을 통해 들어오는 데이터나 메모리에서 직접 들어오는 데이터를 호스트 CPU를 호출하지 않고 실시간으로 처리할 수 있습니다. 이것이 인라인 또는 "범프 인 더 와이어" 가속 사용 사례입니다. 또는 전체 알고리즘을 FPGA로 오프로드하고 결과를 호스트 CPU에 다시 기록할 수 있습니다. 이것이 바로 룩-어사이드 가속 사용 사례입니다.

FPGA를 변경하거나 현장 프로그래밍 기능을 사용하여 워크로드를 즉시 변경함으로써 고급 확장성을 달성할 수 있습니다. 또한 FPGA는 여러 워크로드를 서로 간섭하지 않고 병렬로 실행할 수 있습니다. FPGA는 본질적으로 풍부한 IO를 제공하며 가속 카드에는 다양한 인터페이스가 있습니다. 여러 FPGA에 워크로드를 분산하거나 고속 칩 간 통신으로 처리 단계를 활성화하기 위해 FPGA를 클러스터링하면 성능을 확장하는 데 사용할 수 있습니다.

인텔 오픈 가속 스택을 통해 기존 서버에 FPGA 가속 카드를 쉽게 설치하고 애플리케이션을 가속화하도록 시스템을 구성하는 간단한 방법을 제공함으로써 생산성이 향상되고 있습니다.

HPC 데이터센터에서는 전력 소비가 매우 중요합니다. FPGA를 사용하면 하드웨어가 CPU 및 GPU에 비해 더 적은 클럭 주기와 더 낮은 클럭 주파수로 기능을 실행할 수 있으므로 전력 소비가 줄어듭니다. 전력 소비가 낮다는 것은 에너지 절약을 의미하며, 이는 곧 운영비용(OpEx)과 총소유비용(TCO) 지출을 줄일 수 있다는 것을 의미합니다.

다음은 가격입니다. 표준 클러스터용 FPGA 가속 카드에는 다양한 옵션이 있습니다. 클러스터의 성능을 향상시키기 위해 FPGA 가속 카드를 설치하는 것이 성능 목표를 달성하기 위해 클러스터를 업그레이드하거나 갱신하는 것보다 더 비용 효율적일 수 있습니다.

슬라이드 4로 이동 - Agilex: 데이터 중심 세상을 위한 FPGA

이제 10nm 공정 기술을 기반으로 구축된 TI의 FPGA 제품군인 Agilex에 대해 살펴보겠습니다. 첫째, 우리 모두는 글로벌 공급 제약으로 인해 어려움을 겪고 있습니다. Agilex는 인텔 팹에서 제조되었습니다. 둘째, 인텔이 의존성을 줄이기 위해 팹 구축에 투자하고 있다는 발표를 보셨을 것입니다.

애자일렉스로 돌아갑니다. Agilex에는 다양한 기능을 갖춘 여러 하위 제품군이 있지만 오늘은 자세히 설명할 시간이 없습니다. 자세한 내용은 인텔에 문의하거나 intel.com/agilex로 이동하세요.

이전 FPGA 세대와 비교했을 때 최대 40% 더 높은 성능과 최대 40% 더 낮은 전력을 제공하며 더 높은 트랜시버 데이터 속도를 달성할 수 있는 Agilex의 몇 가지 특징이 있습니다. 또한 Agilex는 최대 40 TFLOPS의 DSP 성능을 제공합니다. Agilex는 차세대 HBM인 DDR5와 PCIe Gen5, 그리고 특히 HPC 고객들이 관심을 가질 만한 CXL(Compute Express Link)을 지원합니다.

제가 언급한 핵심 메시지로 강연을 마무리하겠습니다: HPC 고객들은 성능 경쟁에 뛰어들고 있습니다. FPGA는 성능을 향상시키고 전체 TCO를 절감할 수 있는 고유한 기능을 제공하여 시스템을 보완할 수 있습니다.

이제 데이터센터에서는 Agilex FPGA만으로는 사용할 수 없으며, 물론 필요한 모든 인터페이스와 메모리와 같은 보드에 필요한 구성 요소를 갖춘 FPGA를 호스팅하는 엔터프라이즈급 카드가 있어야 합니다. 비트웨어의 도움으로 데이터센터 성능을 향상시킬 수 있는 Agilex 기반 가속 카드가 시중에 나와 있습니다. 이제 크레이그의 차례입니다.

(크레이그)

감사합니다, Christian, 그리고 오늘 웨비나를 시청해주신 모든 분들을 환영합니다.

잘 모르시는 분들을 위해 설명하자면, BittWare는 고성능 컴퓨팅을 비롯한 다양한 시장에서 주요 고객에게 서비스를 제공하는 세계 최대의 설계 및 제조 회사 중 하나인 Molex의 계열사입니다.

비트웨어는 몰렉스의 데이터센터 그룹에 속해 있습니다.

BittWare는 최신 및 최고의 FPGA를 갖춘 엔터프라이즈급 가속 제품을 설계 및 제조하는 업체로, 오늘 웨비나에서는 인텔 애자일렉스 FPGA에 대해 집중적으로 다룹니다.

이러한 고성능 프로그래머블 가속기를 통해 고객은 인텔 FPGA 기반 솔루션을 신속하고 낮은 위험으로 개발 및 배포할 수 있습니다.

저희 제품은 신속한 프로토타이핑과 벤치마킹에 사용되지만 궁극적으로는 비용 효율적인 대량 배포를 위한 것입니다.

고성능 컴퓨팅이라는 용어는 세 가지 주요 애플리케이션 영역으로 나뉩니다: 컴퓨팅, 네트워크, 스토리지입니다.

여기에는 FPGA에 적합한 다양한 워크로드가 있습니다. 예를 들어 자연어 인식, 추천 엔진, 네트워크 모니터링, 추론, 보안 통신, 분석, 압축, 검색 등이 있습니다.

비트웨어는 인텔 FPGA에서 이러한 워크로드를 구현하는 데 드는 비용, 노력, 위험을 줄이기 위해 노력하고 있습니다.

이를 위한 첫 번째 방법은 FPGA 디바이스(이 경우 인텔 애자일렉스 FPGA)를 가져와 플랫폼 제품을 만드는 것입니다.

주로 HHHL, FHHL 및 듀얼 슬롯 GPU를 포함한 폼 팩터의 PCI Express 카드를 지원하지만, U.2를 포함한 일부 스토리지 폼 팩터도 지원합니다.

각 카드 또는 모듈은 기존 및 신규 인프라와의 호환성을 보장하기 위해 공식 사양을 준수합니다.

카드는 개별적으로 구매하거나 FPGA에 최적화된 서버에 재통합되어 제공될 수 있으며, 이를 TeraBox라고 부릅니다. 유니티는 종종 슬라이드에 나열된 업체와 같은 선도적인 공급업체의 서버를 활용합니다.

현재 다음과 같이 세 가지 인텔 애자일렉스 제품을 출시하고 있습니다.

GPU 크기의 IA-840f 카드는 현재 주력 제품입니다. AGF-027, DDR4 메모리 뱅크 4개, 네트워크 포트, 확장 포트가 특징입니다. 스트라틱스 10 MX 카드에서는 몇 년 전부터 oneAPI를 지원해왔지만, 840f는 한API 툴플로우를 지원하는 최초의 Agilex 기반 카드입니다.

인텔의 oneAPI는 통합 소프트웨어 프로그래밍 모델을 도입하는 대담하고 환영할 만한 이니셔티브입니다. 고객은 oneAPI를 사용하여 아키텍처 전반에서 네이티브 고급 언어 성능을 갖춘 단일 코드 기반에서 프로그래밍할 수 있습니다.

oneAPI에는 직접 프로그래밍 언어가 포함되어 있습니다: 데이터 병렬 C++와 API 기반 프로그래밍을 위한 라이브러리 세트가 포함되어 있어 아키텍처 간 개발을 보다 쉽게 할 수 있습니다.

Data Parallel C++는 친숙한 C++를 기반으로 하며, 크로노스 그룹의 SYCL을 통합합니다. 이를 통해 여러 아키텍처에서 코드 재사용을 획기적으로 간소화하고 가속기를 위한 맞춤형 튜닝이 가능합니다.

기본적으로 일반적으로 x86 또는 GPU 기술을 사용하는 소프트웨어 고객에게 FPGA를 개방합니다. Agilex에서 하나의 API로 개발 및 벤치마킹을 하고자 하는 모든 고객은 BittWare '840f 카드를 고려해야 합니다.

비트웨어는 인텔 스트라틱스 10 카드에서 oneAPI 지원을 개척했습니다. 이러한 구현을 위해 보드 지원 패키지로 OpenCL 계층을 사용했습니다. 예제 설계 및 백서는 웹사이트의 리소스 섹션에서 확인할 수 있습니다.

인텔 애자일렉스 기반 제품의 경우, oneAPI 구현은 인텔 오픈 FPGA 스택 또는 "OFS"를 사용합니다.

FPGA 프로그래밍을 완전히 포기하고 싶은 고객은 BittWare 파트너 프로그램을 통해 Atomic Rules, Edgecortix, Eideticom과 같은 도메인 전문가로부터 애플리케이션 코드가 사전 프로그래밍된 FPGA 가속기 카드를 구매할 수 있습니다.

2023년 이후의 새로운 기술을 앞두고 있는 지금, 고성능 컴퓨팅의 미래를 위해 CXL보다 더 중요한 것은 없을 것입니다.

컴퓨트 익스프레스 링크의 약자인 CXL은 새로운 가속기 링크 프로토콜입니다. 호스트와 가속기 간의 일관된 통신을 가능하게 함으로써 기존 PCIe 프로토콜을 기반으로 하고 그 이상의 기능을 추가합니다. 이 경우 인텔 애자일렉스 FPGA가 이에 해당합니다. 이를 통해 CXL 링크를 이기종 컴퓨팅을 위한 룩-어사이드 또는 인라인 가속기와 함께 사용할 때 효율적이고 지연 시간이 짧은 고대역폭 성능을 구현할 수 있습니다.

비트웨어가 CXL을 지원하는 새로운 FPGA 가속기 카드 3종을 발표했습니다. '440i 및 '640i는 단일 폭 HHHL 및 FHHL 카드로, Agilex FPGA의 I-시리즈를 지원합니다.

400기가비트 이더넷을 위한 인상적인 F-Tile 지원과 PCI Express Gen 5 x16을 위한 R-Tile 지원을 활용했습니다.

GPU 크기의 '860m 카드에는 획기적인 M 시리즈 Agilex FPGA가 탑재되어 있으며, 패키지 내 최대 32GB의 HBM2 메모리와 외부에서 DDR5 메모리를 지원합니다. 고성능 컴퓨팅, 특히 메모리를 많이 사용하는 애플리케이션을 위한 놀라운 장치입니다.

비트웨어가 CXL을 지원할 수 있는 이유는 Agilex I-시리즈 및 M-시리즈 FPGA 제품군 모두 하드 IP를 탑재하고 있어 FPGA 리소스 사용을 최소화하면서 5세대 x16 구성의 전체 대역폭을 지원할 수 있기 때문입니다.

2023년 1분기에 첫 번째 CXL 지원 FPGA 카드를 출시할 계획입니다.

그렇다면 CXL이 중요한 이유는 무엇일까요? 고객들은 애플리케이션 내에서 다양한 메모리에 액세스할 수 있는 더 높은 성능, 더 나은 에너지 효율성, 컴퓨팅 기능이 필요하다는 점을 명확히 인식하고 있습니다.

CXL은 FPGA를 사용하는 이기종 컴퓨팅 아키텍처에 새로운 차원의 성능을 제공할 것이라는 데 의견이 일치합니다.

인텔 애질렉스 FPGA는 경쟁 솔루션보다 포트당 4배의 CXL 대역폭과 포트당 2배의 PCIe 대역폭을 제공합니다.

클라우드 컴퓨팅이 더욱 보편화됨에 따라 고객은 더 빠르고 효율적인 데이터 처리를 위해 아키텍처를 발전시켜야 합니다.

이는 앞서 언급한 세 가지 주요 애플리케이션 영역에서의 혁신을 의미합니다. 구체적으로 컴퓨팅 집약적인 워크로드를 위한 가속기 기술, 데이터를 즉시 처리할 수 있는 네트워크 영역 내 SmartNIC, 스토리지 플레인 내에서 저장된 방대한 양의 데이터를 처리할 수 있는 컴퓨팅 스토리지의 긴밀한 결합이 바로 그것입니다.

컴퓨팅, 네트워크, 스토리지 기술은 이미 PCI Express를 통해 연결되지만, 애플리케이션 성능의 획기적인 변화를 달성하려면 CXL의 이점을 활용해야 합니다.

CXL 프로토콜은 CXL 연결 디바이스에 대한 세 가지 사용 구성을 설명합니다.

유형 1 장치는 가속기가 자체 메모리에 대한 호스트 액세스 없이 프로세서의 메모리에 일관되게 액세스해야 하는 SmartNIC와 같은 스트리밍 및 지연 시간이 짧은 애플리케이션에 사용할 수 있습니다.

유형 2 장치는 세 가지 CXL 하위 프로토콜을 모두 처리하기 때문에 가장 복잡한 구현입니다: 이 유형은 AI 추론, 데이터베이스 분석 또는 스마트 스토리지와 같은 복잡한 작업에 사용하기 위한 것입니다.

타입 3 장치를 사용하면 호스트가 CXL 장치에 연결된 모든 메모리에 일관되게 액세스할 수 있습니다. 이 경우에도 FPGA는 고유한 압축 및 암호화 알고리즘과 같은 특수 FPGA 로직을 구현할 수 있어 여전히 유용한 이점을 제공할 수 있습니다.

잘 모르시는 분들을 위해 설명하자면, 인텔 FPGA CXL IP는 하드 IP와 소프트 IP의 조합으로 제공됩니다.

인텔의 CXL IP를 사용하여 애플리케이션을 설계하려면 고객은 별도의 IP 라이선스를 구매해야 합니다.

인텔 CXL 라이선스를 활성화하면 쿼터스 프라임 도구에서 인텔 IP를 찾을 수 있습니다.

Agilex R-Tile용 CXL 하드 IP가 활성화되면 적절한 소프트 IP가 설계에 추가됩니다.

BittWare의 PCIe 카드에 탑재되어 출시되는 Agilex I 시리즈 FPGA는 CXL 1.1 및 2.0을 지원합니다.

더 나아가 인텔은 PCIe Gen 6 사양과 연계된 CXL 3.0을 지원하기 위한 로드맵을 가지고 있습니다.

따라서 CXL이 중요해질 것입니다. 이 웨비나를 시청하는 사람 중 새로운 기술을 이해하고 평가하는 업무를 하는 사람이라면 누구나 CXL을 고려해야 합니다.

이를 지원하기 위해 비트웨어는 완벽한 CXL 개발 및 벤치마킹 플랫폼을 구축하고 있습니다.

인텔 사파이어 래피즈 제온 CPU가 탑재된 2U 랙 마운트 서버로 구성됩니다. 비트웨어의 인텔 애자일렉스 I 시리즈 FPGA 카드도 사전 통합되어 있습니다.

개발을 시작하는 데 필요한 인텔 쿼터스 및 CXL 라이선스와 함께 Linux 운영 체제가 사전 설치됩니다.

고객이 매우 빠르게 속도를 낼 수 있도록 이 번들에는 CXL을 활용한 애플리케이션 예제 레퍼런스 디자인이 포함되어 있습니다.

기술 지원 서비스와 함께 서버 및 FPGA 하드웨어를 포괄하는 기술 지원 및 포괄적인 보증이 포함되어 있습니다.

이는 저희가 제공하는 기능의 일부일 뿐입니다. 자세한 내용은 추후 발표될 예정입니다. 그 동안 자세한 내용은 BittWare에 문의하시기 바랍니다.

그럼 이제 다음 웨비나를 마우리치오에게 넘겨드리겠습니다. 감사합니다.

(마우리치오)

고마워요, 크레이그.

이제 이 사례 연구에 사용된 프로그래밍 모델인 oneAPI에 대해 살펴보겠습니다.

IA-840f와 같은 프로그래밍 가능한 가속 카드는 이기종 컴퓨팅 아키텍처를 위한 강력한 빌딩 블록입니다. 고성능 컴퓨팅에서 이기종 아키텍처가 인기를 끌고 있는 이유는 모든 워크로드가 동일하지 않고, CPU, GPU, FPGA, 전용 가속기 등 모든 워크로드에 적합한 단일 컴퓨팅 아키텍처가 존재하지 않기 때문입니다. 프로그래머는 이기종 아키텍처를 채택함으로써 처리량, 지연 시간, 전력 효율성 측면에서 각 워크로드에 가장 적합한 아키텍처를 선택할 수 있습니다.

그러나 이기종 아키텍처용 코드를 개발하는 것은 간단한 작업이 아니며 상당한 어려움을 수반합니다. 오늘날 각 데이터센터 아키텍처는 서로 다른 언어와 라이브러리를 사용하여 프로그래밍해야 합니다. 즉, 별도의 코드 베이스를 유지 관리해야 하며 플랫폼 간 포팅에는 상당한 노력이 필요합니다. 또한 플랫폼 간에 일관되지 않은 도구 지원은 개발자가 다양한 도구 세트를 학습하는 데 시간을 낭비해야 한다는 것을 의미합니다.

즉, 각 하드웨어 플랫폼에 맞는 소프트웨어를 개발하려면 별도의 투자가 필요하며, 해당 작업을 다른 아키텍처에 맞게 재사용할 수 있는 기능이 거의 없습니다.

이 문제에 대한 인텔의 솔루션은 CPU 및 가속기 아키텍처 전반에 걸쳐 통합 소프트웨어 개발 환경을 제공하는 프로젝트인 oneAPI입니다.

이 프로젝트는 독점적인 프로젝트가 아닙니다. 그 대신 생태계 전반에서 호환 가능한 구현 개발을 목표로 사양 공동 개발을 위한 개방형 업계 이니셔티브를 기반으로 합니다.

그런 다음 인텔은 프로그래밍 모델을 다음 슬라이드에서 설명할 툴킷 세트로 구현했습니다.

oneAPI 프로그래밍 언어는 데이터 병렬 C++입니다. 이는 데이터 병렬 프로그래밍 생산성을 위해 설계된 고수준 언어입니다. 광범위한 호환성을 위해 C++ 언어를 기반으로 하며, GPU 소프트웨어 개발자에게 익숙한 프로그래밍 모델을 사용하여 독점 언어에서 코드 마이그레이션을 간소화합니다.

언어의 출발점은 업계 컨소시엄인 크로노스 그룹에서 개발 중인 SYCL입니다. 인텔과 커뮤니티는 표준으로 추진될 확장을 통해 언어의 격차를 해소하고 있습니다.

데이터 병렬 C++를 사용하면 다양한 하드웨어 대상에서 코드를 재사용할 수 있습니다: CPU, GPU 또는 FPGA. 하지만 성능을 극대화하기 위해 각 아키텍처에 맞게 조정해야 합니다.

앞서 언급했듯이 인텔의 oneAPI 레퍼런스 구현은 툴킷 세트입니다.

툴킷에는 다음이 포함됩니다:

- CPU, GPU 및 FPGA를 대상으로 하는 데이터 병렬 C++ 컴파일러로, 검증된 LLVM 컴파일러 기술과 인텔의 컴파일러 리더십의 역사를 활용합니다.

- CUDA로 작성된 기존 코드가 있는 개발자가 DPC++로 쉽게 전환할 수 있도록 소스 코드에서 소스 코드로의 포팅 툴입니다.

- API 기반 프로그래밍의 경우, 가속의 이점을 누릴 수 있는 여러 워크로드 도메인에 걸쳐 다양한 성능 라이브러리가 있으며, 라이브러리 기능은 각 대상 아키텍처에 맞게 사용자 정의 코딩되므로 개발자가 지원되는 아키텍처 간에 코드를 마이그레이션할 때 개발자의 튜닝이 필요하지 않습니다.

- 마지막으로, 향상된 버전의 VTune 프로파일러 및 Advisor 성능 도구를 포함한 분석 및 디버그 도구가 제공됩니다.

현재 FPGA의 API 기반 프로그래밍 지원은 제한되어 있다는 점에 유의하세요.

FPGA에서 데이터 병렬 C++ 코드 빌드 및 실행을 시작하려면 다음과 같이 구성된 개발 소프트웨어 스택을 다운로드하여 설치해야 합니다:

- 보고서 생성을 통해 코드 에뮬레이션 및 정적 성능 분석을 지원하는 인텔 oneAPI 기본 툴킷입니다.

- 인텔 쿼터스 프라임을 포함한 oneAPI 베이스 툴킷용 인텔 FPGA 애드온은 FPGA 비트스트림 컴파일 및 FPGA에서의 코드 실행을 지원합니다.

- 마지막으로 사용 중인 카드에 대한 보드 지원 패키지가 필요합니다. 이는 카드 공급업체에서 제공합니다. 이 사례 연구에 사용된 IA-840f 카드의 경우 보드 지원 패키지는 BittWare에서 제공합니다.

oneAPI 개발 스택은 기존의 RTL 기반 FPGA 설계 방법론에 익숙하지 않은 소프트웨어 프로그래머도 FPGA 플랫폼에 쉽게 액세스할 수 있도록 해줍니다. RTL로 설계하려면 FPGA 아키텍처 세부 사항과 타이밍 클로저와 같은 고급 주제에 대한 깊은 이해가 필요합니다. oneAPI를 사용하면 이러한 세부 사항은 컴파일러와 BSP에서 처리되며, FPGA 프로그래밍에 필요한 노력은 다른 플랫폼과 동일해집니다.

이제 세자르가 오늘 소개할 사례 연구에 대해 소개해 드리겠습니다.

(세자르)

안녕하세요, 저는 바르셀로나 슈퍼컴퓨팅 센터의 Cesar Gonzalez입니다. 저희 센터에서 FPGA 장치를 사용하고 있는 연구에 대해 소개해드리고자 합니다.

먼저 저희 슈퍼컴퓨터를 소개해드리겠습니다: "마레노스트럼." 바르셀로나를 방문하신다면 이곳을 방문하실 수 있습니다(물론 사그라다 파밀리아 같은 기념물도 방문하실 수 있습니다).

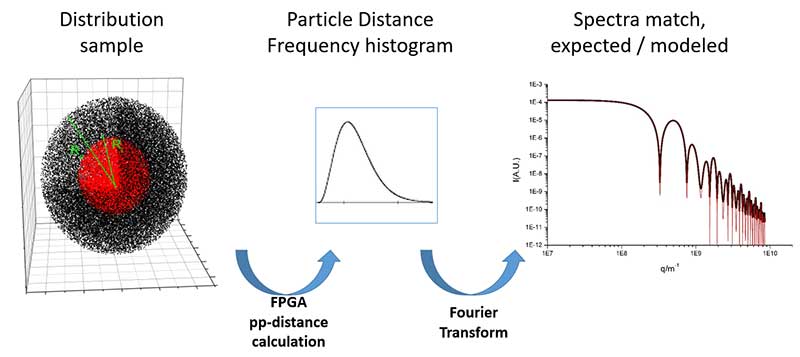

연구 목적: 다른 어떤 시스템으로도 결정할 수 없는 작은 분자의 구조를 결정하려고 합니다. 방법: 분자의 스펙트럼을 사용하여 구조를 알아내려고 합니다. 분자의 스펙트럼이 있다면 어떻게 구조를 찾을 수 있을까요?

그래서 우리는 지난 세기에 입증된, 즉 3D 공간에서 분자 모델을 구축한 다음 나중에 이 이론적 모델의 스펙트럼을 구축하고 이 스펙트럼을 실제와 비교할 수 있는 방법을 사용합니다.

스펙트럼이 동일하다면 구조를 확보한 것입니다. 그렇지 않은 경우 모델을 다시 구성하여 새 스펙트럼을 계산하여 실제 스펙트럼과 일치하는지 확인할 수 있습니다.

좋아요, 그럼 처음에 우리가 뭘 하고 있었나요? 그게 진짜인지 확인하기 위해 테스트를 했습니다. 이중 밀도 구에 200만 개의 전자를 넣어 테스트했는데, 여기 슬라이드에서 보실 수 있습니다.

따라서 이 이중 구의 스펙트럼의 분석 해를 알고 있으므로 이 구의 이론적 스펙트럼을 계산하고 나중에 스펙트럼의 분석 해와 비교합니다.

이 모델의 스펙트럼을 계산하려면 (테스트처럼 사용하는) 이 모델에서 두 입자의 모든 거리를 계산해야 합니다.

입자 수가 매우 많으면 모든 거리에서 수행하는 데 걸리는 시간이 매우 길어지기 때문에 고성능 컴퓨팅이 필요한 곳입니다. 따라서 여기에는 2백만 개의 전자의 샘플 분포가 테스트 대상입니다.

이 두 밀도 구 모델의 히스토그램을 계산했습니다. 좋아요.

두 입자를 가져와서 거리를 계산하고 [첫 번째] 입자의 밀도에 두 번째 입자의 전자 밀도를 곱한 다음 이 가중치를 히스토그램의 거리 위치에 넣습니다.

예를 들어 두 입자의 거리는 100옹스트롬입니다: 따라서 이 쌍의 전자 무게를 여기 히스토그램의 100 옹스트롬...x [축]...에 넣습니다. 좋아요.

따라서 200 옹스트롬 거리가 있으면 반대쪽을 넣습니다. 200앵스트롬 거리 중 한두 개가 더 있으면 히스토그램에 더하고 히스토그램을 취합니다. 여기서는 FPGA 거리 계산을 사용하고 있습니다.

나중에 전체 히스토그램을 가지고 푸리에 변환을 수행하면 계산한 것, 즉 여기 빨간색 선이 분석 해(다른 선)와 동일한지 확인할 수 있으며 이것이 일치하는 것을 볼 수 있습니다. 그래서 우리는 지난 세기의 이론이 사실임을 증명했습니다.

그래서 우리는 구조를 알고 있는 실제 분자를 가지고 이 분자의 이론적 모델을 만든 다음, 나중에 이것이 분자의 스펙트럼과 실제로 일치하는지 확인하는 또 다른 단계에 들어갑니다.

다음은 실버 베헤네이트 세포입니다. 이 세포에는 두 개의 베헤네이트은 분자가 있습니다. 실버 베헤네이트의 실제 구조를 알고 있기 때문에 이 모델을 만들었고 나중에 모델을 만들었습니다. 여기 모델이 있습니다-무엇을 사용했나요? 세포를 25×25로 3번 반복하는 것입니다. 그리고 FPGA를 사용하여 이론적 스펙트럼을 수행합니다.

여기 뭐가 있나요?

녹색 선은 실버 베헤네이트의 실제 스펙트럼입니다. 파란색은 하트트리-복의 양자 분포를 사용한 전자를 사용한 계산입니다.

검은색 선은 전자가 무작위로 분포된 것이고 빨간색 선은 전자가 아닌 원자로 성능을 계산하는 장치입니다.

우리가 사용하는 또 다른 테스트는 실제 모델과 일치하는지 확인하기 위한 것입니다. 따라서 하트트리 포크의 양자 분포를 사용하면 장치와 일치하는 것을 볼 수 있습니다.

우리에게 중요한 것은 봉우리가 어디에 있는지가 중요하기 때문에 녹색 선이 일치하는지 확인하기 위해 녹색 선을 이동합니다. 피크가 제 위치에 있으면 구조를 알 수 있습니다.

보시다시피 전자의 무작위 분포를 사용하면 그래프 끝의 실제 스펙트럼과 전자의 양자 분포 밀도를 사용하는 하트트리-복의 분포로 풀어낸 그래프 사이에 차이가 있습니다.

따라서 인텔과 카탈로니아 첨단 화학 연구소, 그리고 실버 베헤네이트의 스펙트럼을 연구해 온 ALBA 싱크로트론에도 감사의 말씀을 전하고 싶습니다.

이 프레젠테이션을 봐주신 모든 분들께 감사드리며, 이 DOI 참조에서 볼 수 있는 저희의 과학 논문과 바르셀로나 슈퍼컴퓨팅 센터의 초록집에서 저희의 연구 상황을 보시도록 초대하고 싶습니다. 감사합니다, 안녕히 가세요.

(마우리치오)

고마워요, 세자르.

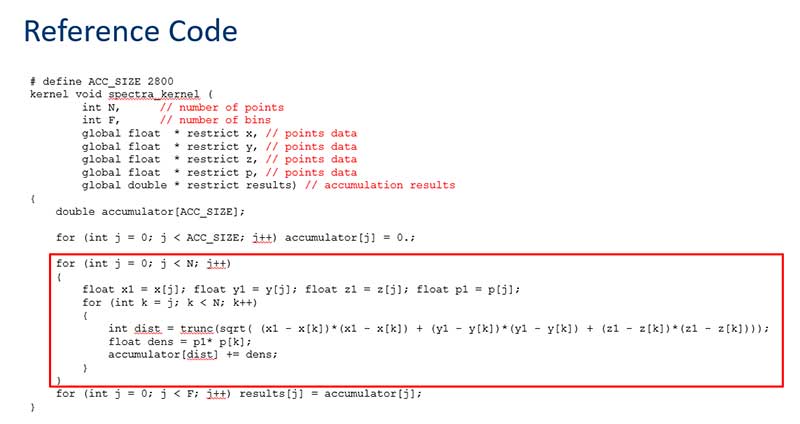

이제 이 사례 연구에서 구현된 알고리즘을 살펴보겠습니다. 이를 입자 쌍 거리 알고리즘 또는 pp-거리 알고리즘이라고 하며 다음과 같이 설명할 수 있습니다.

3차원 공간에 위치한 N개의 입자 집합이 주어졌을 때, 가능한 각 입자 쌍에 대해 입자 사이의 거리를 계산합니다.

이 사례 연구에서는 각 쌍의 전력 밀도가 계산된 거리에 해당하는 구간차원에 누적됩니다. 거리는 단정밀도 부동 소수점을 사용하여 계산한 다음 정수로 변환하여 비닝하고, 누적은 배정밀도 부동 소수점을 사용하여 수행합니다.

이 문제의 복잡도는 N점 집합의 점 쌍 수가 동일한 계수로 스케일링되기 때문에 N제곱입니다.

이 알고리즘은 원래 OpenCL로 구현되어 두 가지 프로그래밍 가능 가속 카드인 Intel Arria 10 GX 카드(Intel Arria 10 1150 FPGA 기반)와 Intel D5005 카드(Intel Stratix 10 SX 2800 FPGA 기반)에서 테스트되었습니다. 그런 다음 이 알고리즘을 DPC++로 포팅하여 BittWare IA-840f 카드(Intel Agilex AGF027 FPGA 기반)에서 구현했습니다.

이 구현에 사용된 툴체인은 oneAPI 릴리스 2022.2와 쿼터스 프라임 프로 21.4입니다. 이 프레젠테이션의 뒷부분에서 위의 모든 구성에 대해 달성한 결과를 살펴보겠습니다.

이제 이 알고리즘에 대한 참조 구현을 간단히 살펴보겠습니다. 이것은 집합의 점 수, 결과에 사용할 구간차원 수, 점 데이터를 저장하는 배열에 대한 포인터(좌표 및 관련 거듭제곱)를 입력으로 받아 누적된 결과의 배열을 반환하는 OpenCL 커널입니다. 커널의 핵심은 포인트 쌍의 거리가 계산되고 전력 밀도 축적이 이루어지는 두 개의 중첩 루프 집합(빨간색 상자 안)입니다.

이전 슬라이드의 레퍼런스 구현은 FPGA에서 실행하기 전에 적절하게 최적화되었습니다. 앞서 Christian이 언급했듯이 FPGA에서는 내부 아키텍처가 구현할 알고리즘에 맞게 구성됩니다.

따라서 FPGA용 코딩은 컴퓨팅 데이터 경로의 아키텍처를 형성하는 것을 의미하며, 이는 컴퓨팅 아키텍처가 고정되어 있는 CPU 및 GPU의 경우와 다릅니다. 프로그래머는 FPGA에 최적화할 때 oneAPI 툴체인에서 제공하는 정보(코드 정적 분석 및 동적 프로파일링 보고서)를 사용하여 구현된 데이터 경로에서 성능 병목 현상을 식별하고 코딩 기술을 사용하여 이를 제거하거나 완화합니다. FPGA용 코드 최적화에 대해 더 자세히 알고 싶다면 인텔 및 GitHub 웹 사이트에서 문서, 교육 자료, 튜토리얼 및 설계 예제를 확인할 수 있습니다.

저희의 경우 메모리 액세스 및 계산 효율성을 개선하기 위해 원본 코드에 몇 가지 최적화를 적용했습니다. 그 결과 원본 코드에 비해 성능이 천 배 이상 향상되었습니다.

이전 슬라이드에서 이 코드가 원래 OpenCL로 작성되어 DPC++로 포팅된 과정을 설명했습니다. 코드 포팅은 매우 간단한 작업이었으며, 아주 제한적인 변경만 필요했습니다. 기본적으로 커널 코드 아키텍처를 DPC++ 코딩 스타일에 맞게 조정해야 했기 때문에 커널 자체에 람다 함수를 사용하고, 데이터 이동을 위한 접근자를 정의하고, 프라그마 및 어트리뷰트의 구문을 새로운 언어에 맞게 조정해야 했습니다. 반면에 호스트 코드는 크게 간소화되었는데, OpenCL에서 명시적으로 관리해야 하는 많은 세부 사항이 DPC++의 런타임에 의해 자동으로 처리되기 때문입니다. 그 결과 DPC++ 호스트 코드는 OpenCL 호스트 코드의 절반 크기입니다.

이제 결과를 살펴보겠습니다.

FPGA 코드는 파라메트릭이라는 점에 유의하세요. 이를 통해 사용자는 구현의 아키텍처 공간을 탐색하고 목표 커널 클럭과 주파수 및 데이터 병렬 처리 간의 최적의 절충점, 즉 언롤 팩터를 찾을 수 있습니다.

이 표의 결과는 각 사례에 대해 찾은 최적의 절충안을 보여줍니다.

첫 번째 줄은 호스트 CPU(즉, 제온 아이스 레이크 프로세서)에서 단일 스레드 코드로 실행되는 알고리즘을 순차적으로 구현한 것을 나타냅니다. 이 구현은 9,600초, 즉 2시간 40분 동안 200만 개의 포인트 데이터 세트를 처리합니다.

IA-840f 카드에서 실행되는 DPC++ 구현은 배정밀도 부동 소수점으로 모든 누적을 수행할 때 순차적 구현보다 157배 빠른 61초 만에 동일한 양의 데이터를 처리합니다. 부분 누적을 위해 40비트 정수를 사용하면 처리 시간이 41초로 233배 빨라집니다.

또한 이전 세대의 하이엔드 FPGA와 비교할 때 Agilex FPGA는 더 높은 클럭 주파수와 더 높은 데이터 병렬 처리가 가능하여 성능이 두 배 향상됩니다.

이상으로 프레젠테이션을 마칩니다. 함께 해주셔서 감사합니다. 이제 Q&A 세션으로 넘어가겠습니다.

(Marcus)

그럼 마커스가 Q&A를 위해 다시 돌아왔으니 그 전에 다시 한 번 정리해 보겠습니다. 많은 정보가 들어왔고 이미 몇 가지 질문이 들어왔습니다. 패널에게 질문이 있으시면 질문 기능을 사용하여 입력해 주시면 패널에게 전달해 드리도록 하겠습니다.

특히 마우리치오와 세자르의 프레젠테이션과 바르셀로나 슈퍼컴퓨팅 센터에서의 HPC 작업에 대한 자세한 설명에 감사드리고 싶었습니다.

이 새로운 Agilex FPGA 제품군은 HPC 워크로드에 적합한 성능과 기능의 탁월한 조합을 제공합니다. 그리고 한API 프로그래밍 모델은 코드 이식성, 유연성, 그리고 마우리치오가 이야기한 것들을 가능하게 해주기 때문에 HPC에 종사하는 사람이라면 누구나 한 번쯤은 고려해야 할 사항이라고 이야기했습니다.

OpenCL을 사용하여 Arria 10 기반 카드에서 Stratix 10으로 코드를 포팅한 다음 마우리치오가 BittWare의 새로운 IA-840f Agilex 카드에서 oneAPI를 사용하여 포팅한 결과 매우 빠르고 원활하게 워크플로를 변경할 수 있었으며, 이것이 바로 장점 중 하나였습니다.

그리고 마지막에 들었던 성능도 마찬가지입니다. Agilex 장치에서 이 HPC 워크로드에서 매우 인상적인 성능과 가속 수치를 보였습니다.

그리고 CXL에 대한 이야기도 들었는데, 크레이그는 곧 출시될 비트웨어의 새로운 CXL 개발 번들에 대해 언급했습니다. 이에 대해 더 자세히 알고 싶으시면 연락주세요.

그럼 이제 질문으로 넘어가겠습니다.

먼저 세자르에게 물어보고 싶었습니다. 사용하신 FPGA에 대해 이야기했는데, 특정 애플리케이션에 FPGA를 사용하기로 결정하게 된 계기는 무엇인가요?

(세자르)

사실 저는 C CUDA를 사용한 GPU로 먼저 프로그래밍을 했고, 팀원 모두가 고성능 컴퓨팅 구성 요소의 작동 원리를 직접 이해하고 있기 때문에 FPGA를 사용했습니다. 그리고 모든 사람이 커널, 즉 OpenCL 커널을 이해하는 것이 매우 중요했습니다.

또한 여러분이 가진 모든 경험, FPGA로 하는 모든 일을 나중에 GPU로 구현할 수 있습니다. 어쨌든 GPU를 사용하면 몇 가지 제한, 사용 제한, 편리함 또는 불편함이 있습니다. 예를 들어 모델이 10배 크면 GPU의 시간은 2배가 됩니다. 반면 FPGA의 시간은 동일합니다. 그렇다고 해서 FPGA가 GPU보다 낫다는 의미는 아닙니다. 우리에게는 다른 환경이 있습니다. 저희는 FPGA가 더 낫습니다. 박사 과정 초기에 저는 디지털, 디지털, 미안하지만 인텔에 한 가지 질문을 했었습니다: "화성에 간다면 무엇을 가지고 갈 것인가? GPU 아니면 FPGA?" (웃음)

(Marcus)

네, 좋은 질문입니다. 좋은 비유를 해주셔서 감사합니다.

간단히 요약해 주시겠어요? 사용하신 프로세스에 대해 자세히 설명해 주셨는데 최종 결과는 무엇인가요? 처음에 말씀하신 것은 알지만...이 결과를 어떤 용도로 사용할 것인지에 대한 사용 사례는 무엇인가요?

(세자르)

분자의 구조를 바로 거기에서 결정할 수 있다면 아픈 사람들을 위한 치료법이나 알약 등을 만들 수 있습니다. 그래서 우리는 생물 의학의 기반과 나노 기술의 기반에서 일하고 있습니다. 따라서 의사와 다른 사람들이 이 분자나 다른 분자를 어떻게 차단할 수 있는지 알고 싶어 할 때 이것은 매우 중요합니다. 이것은 매우 중요합니다.