FPGA服务器

TeraBox X5000TT

用于高性能计算和网络处理的多FPGA系统

过时产品通知:

该产品已过期,无法再购买。请联系 BittWare以获取推荐的更新产品。

概述

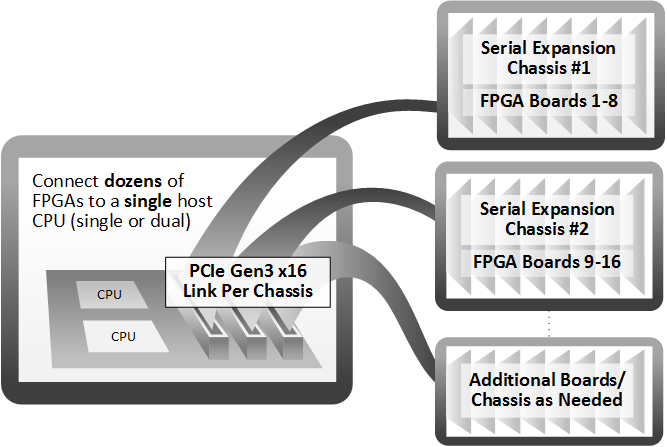

高性能计算(HPC)和网络/包处理应用需要高功率处理和低延迟的I/O。BittWare的串行扩展机箱提供了这两点,具有高达4.6 Terabits/sec的I/O和多达8个大型FPGA的处理能力。它是一个可扩展的、高性能的FPGA平台,是一个交钥匙的解决方案,经过测试和配置,可以让你开始开发你的应用。将多个TeraBox X5000TT扩展机箱连接到服务器上,如BittWare的TeraBox 4000S,你可以有几十个FPGA连接到同一个主机上。

主要特点

至多

32个QSFPs

用于64x 100G或256x 10/25G

5U

在一个5U的服务器上有8个FPGA

支持BittWare的全系列FPGA卡

底盘主要规格

- 5U,深度18英寸(457毫米)

- 主机卡:PEU8039 x16 PCIe主机卡

- 扩展电缆:128Gb/s,1或3米

- 插槽:8x PCIe Gen3 x16

- 电源:1200W微冗余

FPGA卡

TeraBox X500TT最多支持8块BittWare PCIe板。从各种基于UltraScale+或Stratix 10 FPGA的板卡中选择。系统规格会有很大的不同,这取决于你选择的FPGA板。例如,使用8块BittWare XUP-P3R PCIe板,每块板支持高达512Gbytes的DDR4,机箱可以支持多达4TB的内存,内存带宽为4.9 Terabits/sec。使用四块Stratix 10板,每个机箱支持1680万个逻辑元素。

发展支持

BittWare为TeraBox X5000TT系统中的PCIe板提供完整的开发支持。使用BittWare的BittWorks II Toolkit - 一组库和应用程序,提供完整的硬件和FPGA接口 - 与BittWare的FPGA实例一起用于传统的HDL FPGA开发。或者使用SDAccel或OpenCL来实现类似于软件的高级FPGA开发流程。

TeraBox的优势

选择TeraBox FPGA服务器意味着您将得到一个预先配置和测试的解决方案。这包括设置和安装您的FPGA卡和相关硬件,您选择的操作系统和开发工具。您的TeraBox到货后即可使用,使您的团队有更多时间进行开发和部署。

方框图、数据表和规格

系统配置实例

TeraBox X5000TT支持BittWare的许多基于Achronix、Intel或Xilinx FPGA的PCIe卡。下表列出了其中一些卡的规格*:

| FPGA | 服务器中的卡片 | 记忆 | 输入/输出 | 处理 | |

| S7t-VG6 | 速腾7t | 4 | 32组GDDR6(高达32GBytes)。 | 1.8 泰比特/秒 24x 100/50/40/25/10 GbE | 275万个6输入查找表(LUT)。 750 Mbits的嵌入式RAM |

| 520N-MX | Stratix 10 MX | 4 | 8组DDR4(最高可达1兆字节) 16组QDRII+(高达2.3Gbits)。 | 1太比特/秒 16x 100/50/40/25/10 GbE | 840万个系统逻辑元素 64GBytes HBM2 |

| XUP-VV8 | UltraScale+ VU13P | 4 | 16组DDR4(高达2兆字节)。 32组QDRII+(高达9.2Gbits) | 2.3 Terabits/sec 32x 100/50/40/25/10 GbE | 1520万个系统逻辑单元 多达49.152个DSP片断 |

服务器规格

特伦顿系统TTX5100

- PCIe Gen2扩展系统(Gen3即将推出)。

- 5U机架式机箱:19.0"/483毫米(宽)x 8.75"/222毫米(高)x 18.0"/457毫米(深)。

- 通过机箱上的前面板USB接口,为机箱中的所有板卡提供单一USB接口。

- PEU8039 PCIe主机卡用于PCIe over cable I/O

- PED8044 PCIe目标卡用于PCIe over cable I/O

- 1U微型冗余的1200W ATX电源

- 支持多达8个双宽的Gen2 x16板卡

- 128 Gb/s主机总线到扩展系统的带宽(所有板卡共享)。

- 一米或三米的扩展电缆

对价格或更多信息感兴趣?

我们的技术销售团队随时准备提供可用性和配置信息,或回答您的技术问题。

"*"表示必填项目