白皮书

BittWare用于网络包处理的SmartNIC外壳介绍

概述

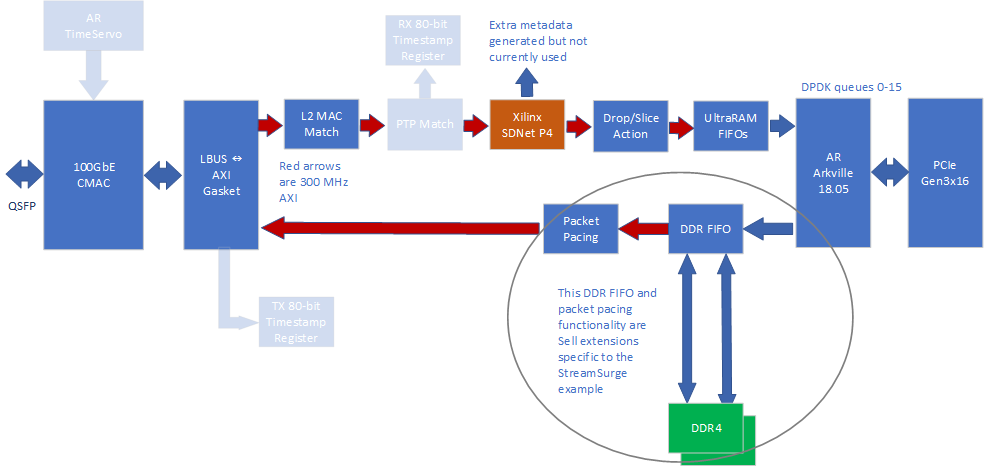

SmartNIC Shell是一个完整的工作网卡,在BittWare FPGA板上实现,作为一个起点,用户将FPGA的价值加入其中。你可以使用SmartNIC Shell来快速部署网络功能(NFV)、网络监控、专门的数据包代理或其他任何操作数据包的功能。Shell提供DPDK卸载,与主机应用进行交互;它以FPGA项目源和全功能位流的形式交付。

关于SmartNIC Shell

SmartNIC Shell包括什么?

- Arkville™ DPDK/AXI感知的数据转换器(原子规则)

- PCIe硬IP(赛灵思)

- 带有AN/LT的100G以太网子系统(赛灵思)。

- 数据包节奏(帧间间隙)块(BittWare)。

- UltraRam FIFO块(BittWare)

- 掉落/切片块(BittWare)。

- Lbus-to-AXI核心 (BittWare)

- DDR4 FIFO (BittWare)

- 二级匹配/行动过滤器(BittWare)。

- 基于HLS的解析器(BittWare)。

- 基于HLS的RSS(BittWare)。

支持的产品

SmartNIC Shell支持以下BittWare产品:

- XUPP3R: 3/4长度的PCIe,带有VU9P FPGA,速度等级为2,启用四个QSFP中的一个。

许可证制度

Loopback的FPGA位流包含几个组件。每个组件的输入和输出都有一个AXI4-Stream接口,共同作为数据平面使用。位流的控制平面使用AXI4-Lite接口连接到物理PCIe接口。

设计流程

- BittWare从Atomic Rules获得Arkville™ DPDK和TimeServo™内核的许可,并对其进行再分配。BittWare在Arkville之上增加价值,作为BittWare的SmartNIC Shell的一部分。

- FPGA项目必须有 "Xilinx 100G以太网子系统与AN/LT "的许可证才能构建。

- 该FPGA项目需要Vivado 2018.3

标题

空标题

DPDK

SmartNIC外壳如何实施DPDK

DPDK是在BittWare卡的FPGA中实现的。BittWare与Atomic Rules的合作是第一个在FPGA内实现的DPDK。

BittWare板使用Atomic Rules PMD的一个补丁版本。基本的PMD包含在DPDK发行版中。BittWare提供必要的补丁作为我们源码发行的一部分。BittWare用DPDK进行的所有测试都使用uio_pci_generic驱动,它取代了BittWorks II驱动。然而,一些BittWorks II的工具仍然可以工作。

用户会收到以下信息:

- 一个放在FPGA内的 "数据移动器",一边连接AXI总线,另一边连接PCIe接口。它采用赛灵思或英特尔的加密许可方案交付。这包括利用每个公司的选项来提供一个有时间限制的评估

- 一个开源的DPDK轮询模式驱动(PMD),用于连接DPDK和上述数据转换器。这个PMD从DPDK 17.05开始成为官方DPDK版本的一部分,名称为 "Arkville"

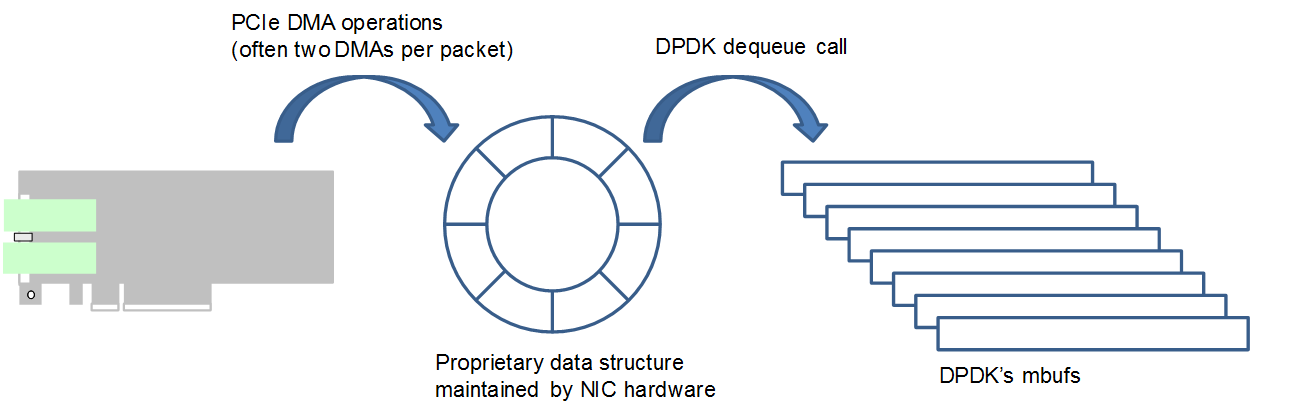

大多数ASIC和FPGA DPDK的实现都是进行一次复制:

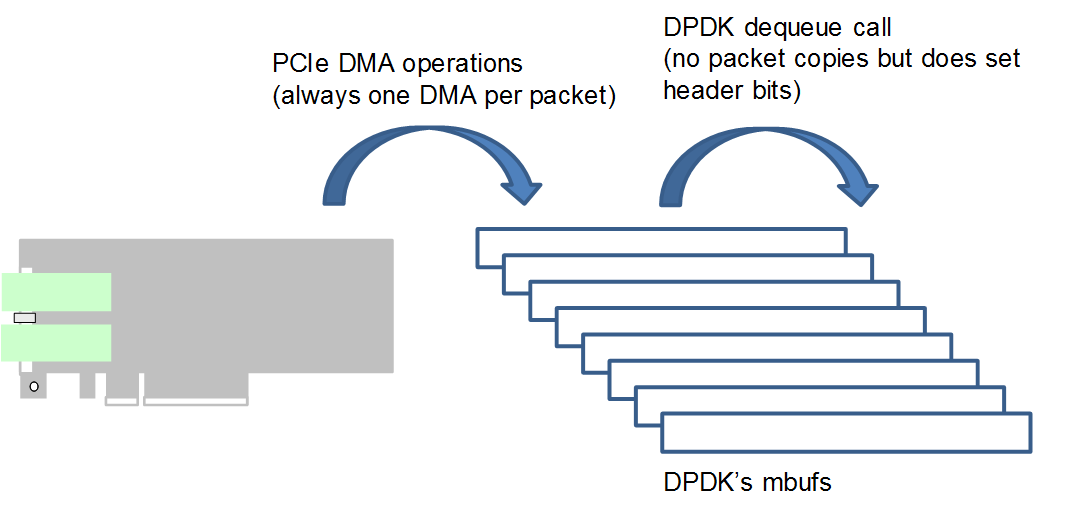

相比之下,SmartNIC Shell的DPDK IP核总是直接DMA到DPDK mbufs,从不要求CPU复制数据包。元数据不需要第二次DMA,减少了CPU开销、延迟和主机内存需求。这确实消除了一些PCIe优化的机会,如将小数据包凝聚到较少的DMA中,或将数据预先格式化为PCAP记录。如果需要,你的应用程序代码可以在DPDK内核上面的FPGA中做这些事情。

还有更多内容要读:获取SmartNIC外壳应用说明

要求下载PDF文件

你在这个页面上看到的是BittWare的SmartNIC Shell介绍。在完整的应用说明中有更多的细节!请填写表格,请求访问PDF版本的完整应用说明。

"*"表示必填项目