XUP-VV8 PCIe Card with Xilinx VU13P FPGA

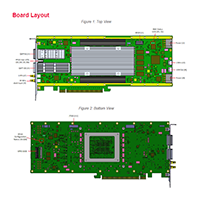

PCIe FPGA Card XUP-VV8 UltraScale+ FPGA PCIe Board with 4x QSFP-DDs 8x 100GbE Network Ports and VU9P/13P FPGA Need a Price Quote? Jump to Pricing

The S7t-VG6 VectorPath accelerator card offers a 7nm Achronix FPGA that is optimized for high-speed networking and fast, high-capacity memory access. Featuring a QSFP-DD (double-density) cage, the board supports up to 1x 400GbE or 4x 100GbE using the 56G PAM4-enabled Speedster®7t device. An additional QSFP port supports 2x 100GbE, and a 4x MCIO connector for expansion. Sixteen channels of GDDR6 graphics DRAM handle high-bandwidth memory requirements, providing up to 448GB/s.

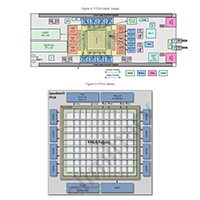

The FPGA offers large logic and memory resources—up to 692K 6-input lookup tables (LUTs), and 189 Mb embedded RAM. It also provides 2,560 MLPs (machine-learning blocks).

QSFPs for 1x 400G or 6x 100G

16GB GDDR6 up to 448GB/s

7nm FPGA with 56Gbps SERDES

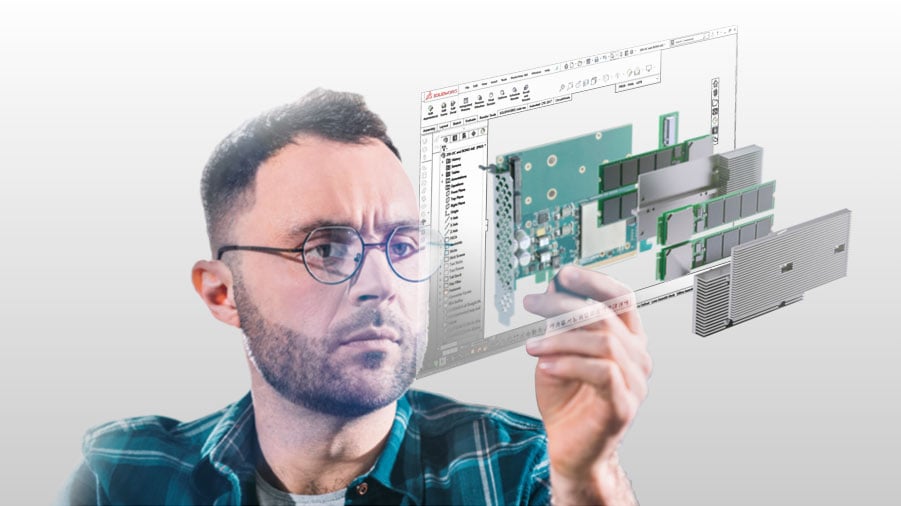

Craig Petrie gives a detailed explanation of the card's key features.

Generation 5.0

The HRG gives you much more detail about the card such as block diagrams, tables and descriptions.

r4 v2

Our technical sales team is ready to provide availability and configuration information, or answer your technical questions.

"*" indicates required fields

PCIe FPGA Card XUP-VV8 UltraScale+ FPGA PCIe Board with 4x QSFP-DDs 8x 100GbE Network Ports and VU9P/13P FPGA Need a Price Quote? Jump to Pricing

FPGA Server TeraBox 2000D Reliable, Proven 2U FPGA Server Legacy Product Notice: This is a legacy product and is not recommended for new designs. It

Article Two Approaches to Rapidly Developing Customized FPGA Solutions How BittWare reduces risk over the complete customized solution lifecycle Overview While FPGAs in the datacenter

IA-780i 400G + PCIe Gen5 Single-Width Card Compact 400G Card with the Power of Agilex The Intel Agilex 7 I-Series FPGAs are optimized for applications