Arkville

DPDK/AXI Aware Data Mover IPコア

Arkville 、ホスト・メモリとFPGAファブリック・ロジック間に高スループット、低レイテンシーのコンジットを提供し、CPUコアの使用をオフロードし、メモリ・コピーを排除し、全体的な効率を向上させます。

PCIe Gen 5で最大480Gbps

最大400GbEまでのあらゆる回線速度で動作可能

DPDKと AXI規格

特徴

- サーバーサイクルをFPGAゲートにオフロード

- FPGAベースのパケット処理ソリューションの迅速な市場投入を実現

- DPDKとAXI規格でGPP/FPGAアプリケーションを未来につなげる

- ラインレートにとらわれない:1/5/10/25/40/50/100/400 GbEなど、どのラインレートでも動作可能

- Gen5 x16インターフェースで最大480Gbps、500Mpps

- FPGAベンダーに依存しないRTL

- Intel/PSGおよびAMD/Xilinx FPGAデバイスの両方をサポート

- DPDK 23.11のオープンソース "net/ark"Arkville ドライバ

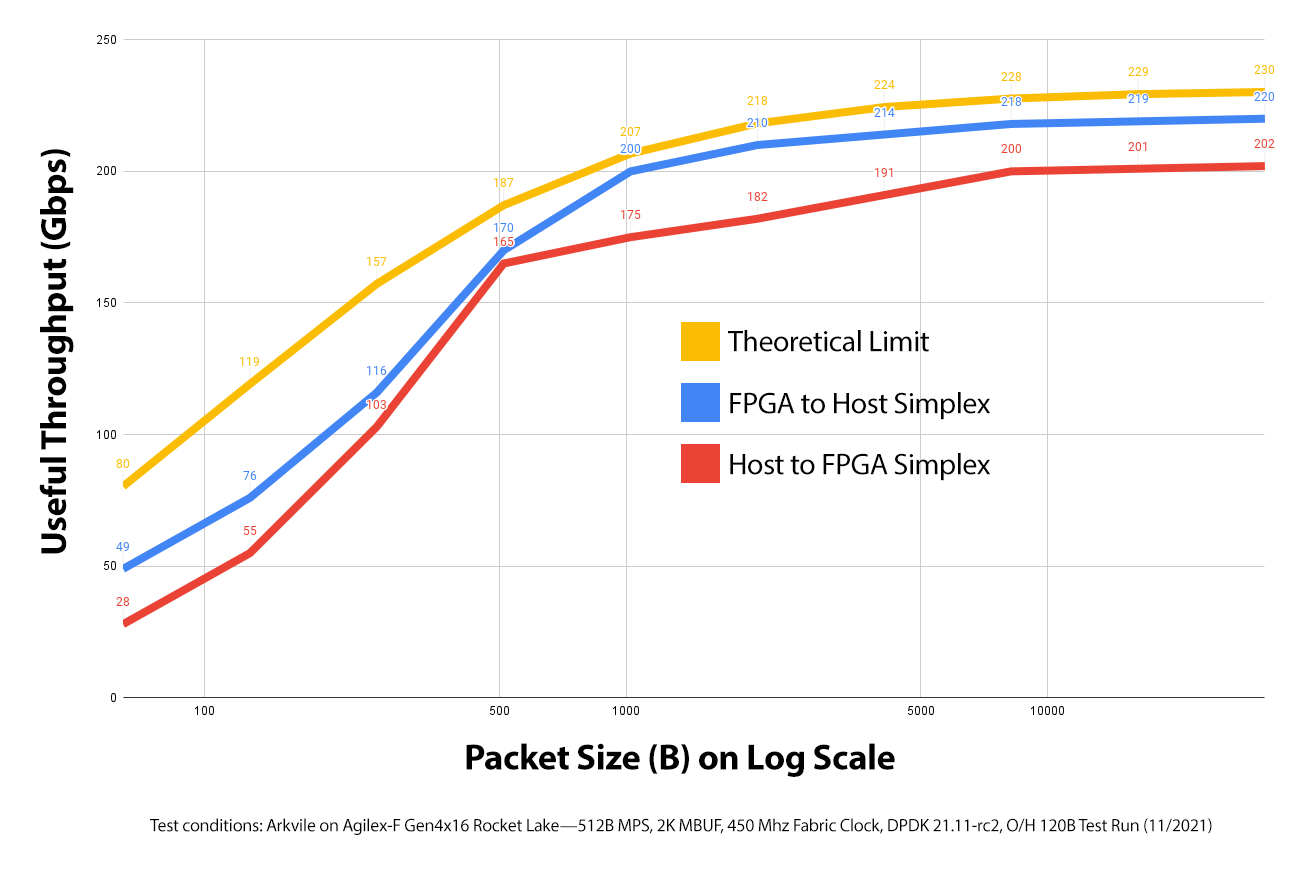

Arkville PCIe Gen4 x16スループット(単位:Gbps

動画

Arkville 17.05のパフォーマンスプロットのデモを見ることができます。

ブロック図、データシート、製品詳細

製品操作

空の見出し

ブロック図に示すように、Arkville には、ハードウェアとソフトウェアの両方のコンポーネントがあります。ハードウェアコンポーネントは、FPGAに存在するIPコアで、イングレスまたはイグレスを行うパケットのAXIストリームを生成および消費する。ソフトウェアコンポーネントはDPDKのPMD「net/ark」、Arkville DPDKポールモードドライバです。Arkville 、FPGAロジックとホストユーザメモリ間のコンジットで、バルクデータの移動や個々のパケットを行います。

Arkville ソリューションは、ソフトウェア上ではラインレートに依存しない FPGA ベースの NIC のように見えます(特定の MAC を使用しない)。DPDK のアプリケーションは、FPGA ハードウェアアクセラレーション の利点を享受するために、大きく変更する必要はありません。

空の見出し

空の見出し

機能詳細について

全体

- FPGA/GPPパケット移動のすぐに使えるソリューション

- 標準4物理キュー・ペア(RX/TX)、最大128物理キュー・ペア

- 複数のポートをサポートする単一のPCIe物理機能(PF)。

- 上流と下流の同時全二重データ移動

GPP/ソフトウエア固有

- DPDKArkville DPDK 23.11のPMD

- Jenkins CI/CDを使った広範囲なテスト

- FPGAアプリケーション用のアンエンコード・アプリケーション・バー(ABAR)

FPGA/Hardware Specific

- パケット移動のためのAXI Streamingインターフェース

- 最大1Tbpsバースト・トラフィック(2つの128バイト幅、500MHz、AXIストリーム)

- FPGAアプリケーション専用アプリケーションバー(ABAR)AXI4マスター

空の見出し

空の見出し

参考例

Atomic Rulesは、Arkville 、独自のソリューションの出発点として使用することができるサンプルデザインを提供します。以下のようなものがあります:

- 4ポート4キューの10GbE例(Arkville + 4×10 GbE MAC)

- シングルポート、シングルキュー100GbEの例(Arkville + 1×100 GbE MAC)

サンプル実施結果

| デバイス | スピード | シックスルーツー | エフエフエス | M20k | エフマックス |

|---|---|---|---|---|---|

| インテルAgilex Fシリーズ | -2 | 81K | 220K | 250 | 500 |

会社について

ネットワークとQoTのためのFPGA IPコンポーネントとソリューションのプロバイダーです。ホストメモリとFPGAファブリックロジック間の高スループット、低レイテンシ通信を実現するArkville データムーバーなどのIPを提供する。

価格や詳細についてご興味のある方は、こちらをご覧ください。

当社のテクニカルセールスチームは、在庫状況や構成情報を提供したり、技術的な質問に答えたりする準備ができています。

"*"は必須項目