带有Intel Stratix 10 MX FPGA的520R-MX PCIe卡

带有HBM2和480Gbps光学输入的PCIe FPGA卡520R-MX Stratix 10 FPGA板,针对具有大量实时数据采集要求的传感器处理应用进行了优化

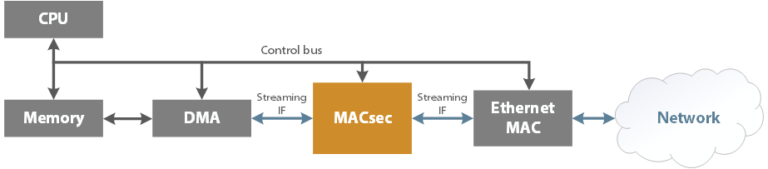

Xiphera MACsec系列提供高速IP核,实现IEEE标准802.1AE-2018中的MACsec(媒体访问控制安全)协议。MACsec协议定义了第2层(根据OSI模型)流量的安全基础设施,确保收到的帧是由声称要发送它的发射站发送的。站点之间的通信也被加密以提供数据的保密性,并被认证以提供数据的完整性。

典型的 MACsec 应用需要 10G、25G、40G 或 100G 等高数据带宽,基于 FPGA 的加速通常能使其受益匪浅。Xiphera MACsec IP 可在 BittWare 的 IA-840f 和 IA-420f Agilex FPGA PCIe 卡上运行。

资源要求适中:

性能:

符合标准:

测试载体的合规性:

OSI网络模型

Xiphera MACsec IP 使用伽罗瓦计数器模式(AES-GCM)的 256 位密钥高级加密标准来保护数据保密性、数据完整性和数据来源验证。XIP1213H 最适合 25 Gbps 链路上的数据流量,XIP1213E 适合 100 Gbps 链路上的流量。

MACsec的最初用例是保护有线局域网中的通信。MACsec还可用于以下方面:

为了保护通信网络中的关键控制信息

为了保护工业自动化应用中的敏感测量数据

为确保点对点视频链接的安全

随附加密源代码、全面的 VHDL 测试平台和详细的数据表。MACsec IP 有四种变体:

| RS-XI-1213B | MACsec AES256-GCM |

| RS-XI-1213H | MACsec AES256-GCM,高速 |

| RS-XI-1213E | MACsec AES256-GCM 极速 |

使用标准化加密算法的基于硬件的安全解决方案。

我们的技术销售团队随时准备提供可用性和配置信息,或回答您的技术问题。

"*"表示必填项目

带有HBM2和480Gbps光学输入的PCIe FPGA卡520R-MX Stratix 10 FPGA板,针对具有大量实时数据采集要求的传感器处理应用进行了优化

来自Atomic Rules的PCIe Gen4数据移动器IP。使用BittWare的PCIe Gen4卡实现高达220 Gb/s的速度,当你需要比标准DMA更多的性能时,可以节省你的开发团队。特点:DPDK和AXI标准,与数据包或任何其他数据格式一起工作,在任何线速下运行,最高可达400GbE。

IA-440i 400G + PCIe Gen5单宽卡 具有Agilex功能的紧凑型400G卡 英特尔Agilex 7 I系列FPGA针对应用进行了优化。