配備PCIe Gen 4的全新IA-220-U2

FPGA 計算儲存處理器 (CSP)

第 4 代 PCIe NVMe

Eideticom NoLoad 支援

BittWare的 IA-220-U2 通過作為另一個U.2模組來加速NVMe FLASH SSD。

Legacy Notice and Recommendation

This is a legacy product and is not recommended for new designs. It is still available for purchase, but development tools and software are no longer maintained for compatibility with the latest FPGA tools and operating systems. Minimum order quantities (MOQs) may apply.

Need a Price Quote?

什麼是計算存儲?

SNIA定義了幾個統稱為「計算存儲」的元件。對於典型的 IA-220-U2 部署,加速任務稱為 CSS(計算存儲服務)。

例如,IA-220-U2的Agilex FPGA可以比CPU更快地執行壓縮,甚至超過存儲系統透明壓縮的傳輸速率。

什麼是雲解決方案供應商?

CSP(如IA-220-U2)與快閃記憶體一起工作,通過執行計算(如壓縮或加密)提供加速計算存儲服務(CSS)。這使用戶可以使用 標準 SSD 構建存儲,而不是被鎖定在單個供應商的快閃記憶體中。

哪些功能使 IA-220-U2 成為功能強大的 CSP?

- PCIe Gen4 介面的頻寬是基於 Gen3 的解決方案的兩倍。

- 可選的 NoLoad 提供了Eideticom的可隨時部署的解決方案。

- 採用 1.4M 邏輯元件的英特爾敏捷 ® FPGA 。

4.0代

帶寬翻倍!

IA-220-U2 採用最新的PCIe Gen4介面構建,可以傳輸高達 Gen3 設備的兩倍頻寬。

解決方案功能:Eideticom的 NoLoad™

NoLoad 將 IA-220-U2 轉變為易於部署的強大 CSP

- 可部署的企業級解決方案

- 可選擇使用者空間或內核空間實現,以盡量減少軟體更改

FPGA 硬體 元件

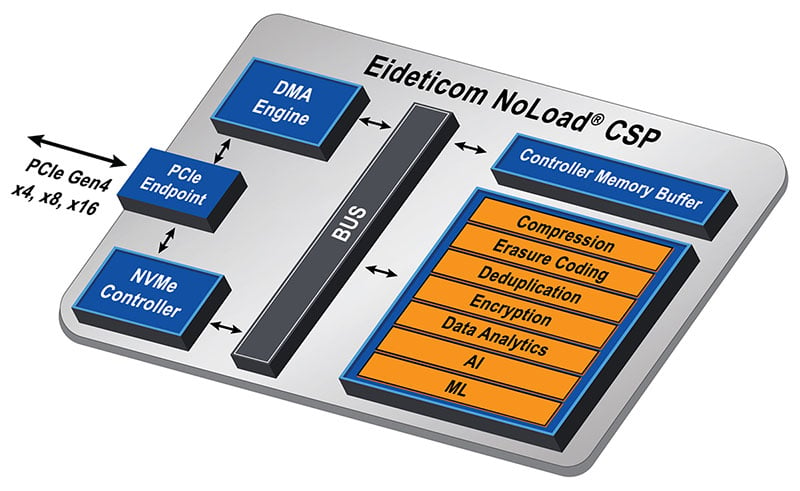

NoLoad 提供 FPGA IP 和主機組件。對於 FPGA IP,您可以在圖表中看到主要元件。更多詳情如下:

- NVMe 前端。 PCIe 端點、NVMe 控制器和 DMA 引擎都在硬體中實現,並支援 IA-220-U2 標準 U.2 介面的 PCIe Gen4 x4。

- CSS 函數。 橙色元件是硬體加速計算存儲服務 (CSS),例如壓縮或加密。

主機 軟體 元件

作為一個完整的解決方案,NoLoad 為主機軟體提供了多種實現選擇:

- libnoload。 通過修改應用程式以使用 libnoload 庫,操作系統可以保持不變。

- 無負載FS。另一種選擇使用 NoLoad FS(文件系統)作為傳統文件系統之上的填充程式。這樣做的好處是使用者應用程式無需更改即可利用加速存儲。

框圖、數據表和規格

想要瞭解更多詳情?

Request the Hardware Reference Guide (HRG)

The HRG gives you much more detail about the card such as block diagrams, tables and descriptions.

Board Specifications

FPGA

- 英特爾敏捷 AGF014

- 核心速度等級 -3:I/O 速度等級 -3

- 聯繫BittWare獲取其他Agilex FPGA選項

板載 DDR4 記憶體

- 兩組 DDR4 SDRAM x 72 位

- 4GB per bank

- 傳輸速率:2400 噸/秒

Host interface

- PCIe Gen4 x4

- U.2 連接器

- 符合 SFF-8639 標準

數據中心部署

- 板載 NVMe-MI 相容 SMBus 控制器(規格 1.0a)

- 通過軟體或SMBus進行現場快閃記憶體更新

- SMBus FPGA 快閃記憶體控制:防磚、回退和多重引導

- SMBus 訪問獨特的電路板數據和溫度感測器

後面板功能

- 可訪問使用者指示燈

開發特點

- 用於訪問FPGA、快閃記憶體和調試工具的JTAG連接器

- GPIO 連接器

電源監控和報告

- 電壓監控

- 溫度監測

- 向 FPGA 報告故障狀態

冷卻

- U.2 驅動器外殼經過優化,可通過被動散熱器進行冷卻

Electrical

- 熱插拔容限

- 來自U.2電源的卡上電源

- Power dissipation is application dependent

- 典型 FPGA 功耗 ~20W

- 設計用於提供高達 25W 功耗的卡

Environmental

- Operating temperature: 5°C to 35°C

- 冷卻:強制通風

品質

- 按照 IPC-A-610 2 類製造

- 符合 RoHS 標準

Form factor

- 符合 U.2 標準的 2.5“ 驅動器外形

- 高度:15毫米

Development Tools

FPGA 開發

- BittWare SDK,包括PCIe驅動程式,庫和電路板監控實用程式(僅支援Linux)

應用開發

- 支持的設計流程 - Quartus Prime Pro(HDL,Verilog,VHDL等)

r1 v1

Ready to Buy?

貿澤電子在線訂購的產品可用性:

對定價或更多資訊感興趣?

我們的技術銷售團隊隨時準備提供可用性和配置資訊,或回答您的技術問題。

“*”表示必填欄位