白皮書

卷積神經網路的 FPGA 加速

概述

卷積神經網路(CNN)已被證明在複雜的圖像識別問題上非常有效。本白皮書討論了如何使用 BittWare 的 FPGA 加速器產品加速這些網路,該產品使用英特爾 OpenCL 軟體開發套件進行程式設計。然後,本文介紹了如何通過降低計算精度來顯著提高圖像分類性能。精度的每一次降低都允許FPGA加速器每秒處理越來越多的圖像。

咖啡整合

Caffe 是一個深度學習框架,考慮了表達、速度和模組化。它由伯克利視覺與學習中心和社區貢獻者開發。

Caffe框架使用XML介面來描述特定CNN所需的不同處理層。通過實現不同的層組合,用戶能夠快速創建新的網路拓撲以滿足其給定的需求。

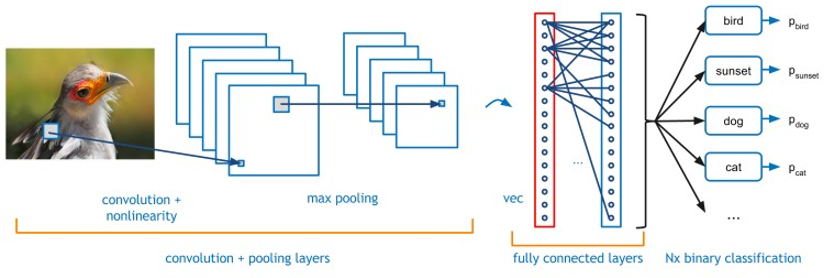

這些層中最常用的是:

- 卷積:捲積層使用一組可學習的過濾器卷積輸入圖像,每個過濾器在輸出圖像中生成一個特徵圖。

- 池化:最大池化將輸入圖像分區為一組不重疊的矩形,並針對每個此類子區域輸出最大值。

- Rectified-Linear: Given an input value x, The ReLU layer computes the output as x if x > 0 and negative_slope * x if x <= 0.

- 內部產品/完全連接:圖像被視為單個向量,每個點都貢獻新輸出向量的每個點

通過將這 4 層移植到 FPGA,絕大多數前向處理網路都可以使用 Caffe 框架在 FPGA 上實現。

圖 1:典型 CNN – 卷積神經網路的示例插圖

亞歷克斯網

AlexNet是一個眾所周知且使用良好的網路,提供免費的訓練數據集和基準。本文討論了針對AlexNet CNN的FPGA實現,但是這裡使用的方法同樣適用於其他網路。

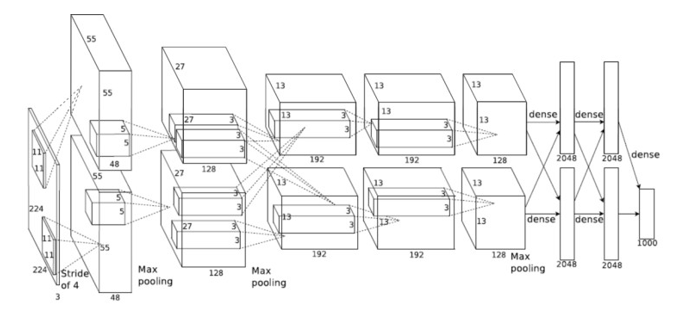

圖2說明瞭AlexNet CNN所需的不同網路層。有 5 個捲積層和 3 個全連接層。這些層佔用>該網路處理時間的99%。不同的捲積層有 3 種不同的濾波器尺寸,11×11、5×5 和 3×3。創建針對不同捲積層優化的不同層將是低效的。這是因為每層的計算時間因應用的過濾器數量和輸入圖像的大小而異。由於處理的輸入和輸出要素的數量。但是,每個捲積都需要不同數量的層和不同數量的圖元來處理。通過增加應用於更多計算密集型層的資源,可以平衡每個層以在相同的時間內完成。因此,可以創建一個流水線進程,該進程可以在任何時候運行多個圖像,從而最大限度地提高所用邏輯的效率。即大多數處理元素大部分時間都很忙。

圖2:AlexNet CNN – 卷積神經網路

表 1 顯示了 Imagenet 網路每一層所需的計算。從此表中可以看出,5×5卷積層比其他層需要更多的計算。因此,FPGA需要更多的處理邏輯才能使該層與其他層平衡。

<p”>The inner product layers have a n to n mapping requiring a unique coefficient for each multiply add. Inner product layers usually require significantly less compute than convolutional layers and therefore require less parallelization of logic. In this scenario it makes sense to move the Inner Product layers onto the host CPU, leaving the FPGA to focus on convolutions.

FPGA 邏輯領域

FPGA 元件有兩個 處理 區域:DSP 和 ALU 邏輯。DSP 邏輯是用於乘法或乘法加法運算子的專用邏輯。這是因為使用 ALU 邏輯進行浮點大(18×18 位)乘法的成本很高。鑒於DSP運算中乘法的通用性,FPGA供應商為此提供了專用邏輯。英特爾更進一步,允許重新配置 DSP 邏輯以執行浮點操作。為了提高CNN處理的性能,有必要增加FPGA中實現的乘法次數。一種方法是降低位精度。

空標題

| ImageNet 圖層 | 乘法加法 (M) |

| 卷積 (11×11) | 130 |

| 捲積 (5×5) | 322 |

| 卷積 (3×3) 1 | 149 |

| 卷積 (3×3) 2 | 112 |

| 卷積 (3×3) 3 | 75 |

| 內積 0 | 37 |

| 內積 1 | 17 |

| 內積 2 | 4 |

表1:ImageNet層計算要求

位精度

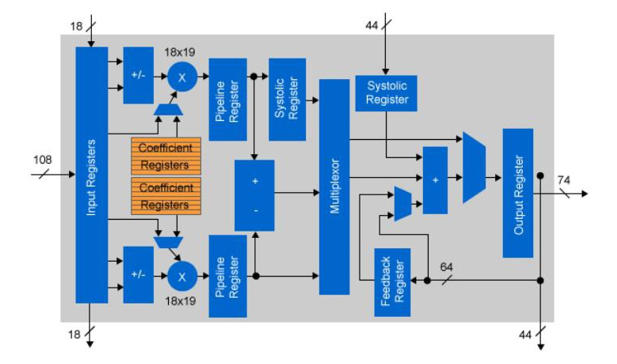

大多數CNN實現使用浮點精度進行不同的層計算。對於 CPU 或 GPGPU 實現,這不是問題,因為浮點 IP 是晶片架構的固定部分。對於 FPGA,邏輯元件不是固定的。英特爾的Arria 10和Stratix 10設備具有嵌入式浮動DSP模組,也可以用作定點乘法。實際上,每個DSP元件都可以用作兩個獨立的18×19位乘法。通過使用18位固定邏輯執行卷積,與單精度浮點數相比,可用運算子的數量增加了一倍。

層數 | 大小 | 篩檢程式尺寸 | 無篩檢程式 |

轉換 x2 | 416×416 | 3×3和 1×1 | 32,64 |

CONV x3 | 208×208 | 3×3和 1×1 | 64,128 |

CONV x5 | 104×104 | 3×3和 1×1 | 64,128 |

CONV x17 | 52×52 | 3×3和 1×1 | 128,256 |

CONV x17 | 26×26 | 3×3和 1×1 | 256,512 |

CONV x15 | 13×13 | 3×3和 1×1 | 512×1024 |

上採樣 & 路由 | 26×26 | 3×3和 1×1 | 256 |

CONV x7 | 26×26 | 3×3和 1×1 | 256,512 |

上採樣 & 路由 | 52×52 | 3×3和 1×1 | 128 |

CONV x7 | 52×52 | 3×3和 1×1 | 128,256 |

圖 3:Arria 10 浮點 DSP 配置

如果需要降低精度的浮點處理,則可以使用半精度。這需要來自FPGA結構的額外邏輯,但假設較低的位精度仍然足夠,浮點計算的數量增加了一倍。

本白皮書中描述的流水線方法的主要優勢之一是能夠在流水線的不同階段改變精度。因此,資源只在必要時使用,從而提高設計效率。

根據CNN的應用容差,位精度可以進一步降低。如果乘法的位寬可以減小到10位或更小,(20位輸出),則可以僅使用FPGA ALU邏輯有效地執行乘法。與僅使用 FPGA DSP 邏輯相比,可能的乘法次數增加了一倍。某些網路可能容忍更低的位精度。如有必要,FPGA可以處理低至一位的所有精度。

對於AlexNet使用的CNN層,確定10位係數數據是簡單的定點實現可以獲得的最小減少,同時與單精度浮點運算相比保持小於1%的誤差。

圖 4:Arria 10 定點 DSP 配置

CNN 捲積層

使用滑動窗口技術,可以創建記憶體頻寬極輕的卷積內核。

圖 5 說明了數據如何緩存在 FPGA 記憶體中,允許每個圖元多次重複使用。數據重用量與卷積內核的大小成正比。

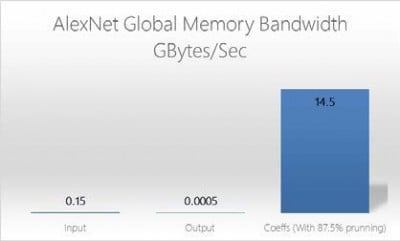

由於每個輸入層都會影響CNN捲積層中的所有輸出層,因此可以同時處理多個輸入層。這將增加載入層所需的外部記憶體頻寬。為了緩解增加,除係數外,所有數據都存儲在FPGA器件的本地M20K記憶體中。器件上的片內存量限制了可以實現的CNN層數。

圖 5:3×3 卷積的滑動視窗

圖 6:OpenCL 全域記憶體頻寬 (AlexNet)

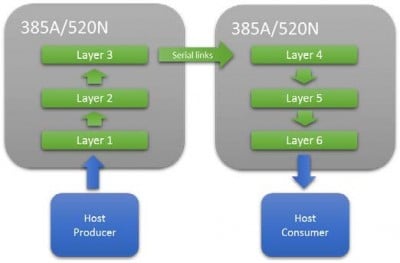

根據可用的M20K資源量,並不總是能夠在單個FPGA上安裝完整的網路。在這種情況下,可以使用高速串行互連串聯多個FPGA。這允許擴展網路管道,直到有足夠的資源可用。這種方法的一個關鍵優點是它不依賴於批處理來最大化性能,因此延遲非常低,這對於延遲關鍵應用程式非常重要。

平衡層之間的相同時間需要調整實現的並行輸入層數和並行處理的像素數。

資源 | AlexNet 5×5 捲積層(浮點數) | AlexNet 5×5 卷積 Layter(16 位) |

註冊 | 346,574 | 129,524 |

DSP 模組 | 1,203 | 603 |

RAM塊 | 1,047 | 349 |

圖 9:Alexnet 的 5×5 卷積層的資源

大多數CNN功能都可以安裝在單個 M20K 記憶體中,並且 FPGA 結構中嵌入了數千個 M20K,可用於並行捲積特徵的總記憶體頻寬約為 10 TB/秒。

資源 | GX1150系列 | GX2800型 |

邏輯元件 (K) | 1,150 | 2,753 |

資產負債管理 | 427,200 | 933,120 |

註冊 | 1,708,800 | 3,732,480 |

可變精度DSP模組 | 181,5 | 5,760 |

18×19 乘數 | 3,036 | 11,520 |

圖7:Arria 10 GX1150 / Stratix 10 GX2800資源

圖 8:在多個 FPGA 上擴展 CNN 網路

圖 9 列出了在英特爾 Arria10 FPGA 上實現單精度和 16 位定點版本的 Alexnet 5×5 卷積層所需的資源,該卷積層具有 48 個並行內核。這些數位包括 OpenCL 板邏輯,但說明了精度較低對資源的好處。

全連接層

處理全連接層需要每個元素具有唯一的係數,因此隨著並行度的增加,很快就會受到記憶體限制。跟上捲積層所需的並行度會很快使FPGA的片外記憶體飽和,因此建議輸入層的階段要麼分批,要麼修剪。

由於內部產品層的元素數量很少,因此批處理所需的存儲量與捲積層所需的存儲量相比很小。然後,批處理層允許對每個批處理層使用相同的係數,從而減少外部記憶體頻寬。

修剪的工作原理是研究輸入數據並忽略低於閾值的值。由於全連接層被放置在CNN網路的後期階段,許多可能的特徵已經被消除。因此,修剪可以顯著減少所需的工作量。

資源

網路的關鍵資源驅動因素是可用於存儲每層輸出的片上M20K記憶體的數量。這是恆定的,與實現的並行度無關。在多個FPGA上擴展網路會增加可用的M20K記憶體總量,從而增加可以處理的CNN的深度。

空標題

結論

FPGA 結構的獨特靈活性允許將邏輯精度調整到特定網路設計所需的最小值。通過限制CNN計算的位精度,可以顯著增加每秒可以處理的圖像數量,從而提高性能並降低功耗。

FPGA 實現的非批處理方法允許對象識別的單幀延遲,非常適合低延遲至關重要的情況。例如,避免客體。

將這種方法用於 AlexNet(第 1 層的單精度,其餘層使用 16 位固定),單個 Arria 10 FPGA 可以在 ~1.2 毫秒內處理每個圖像,或者使用兩個串聯的 FPGA 在 0.58 毫秒內處理每個圖像。