PCIe FPGA 卡

A10SA4

Arria 10 FPGA 薄型PCIe卡

QSFP28 和 DDR4

Obsolete Product Notice:

This is an obsolete product and is no longer available for purchase. Contact BittWare for a recommended newer product.

Need a Price Quote?

概述

BittWare的A10SA4是一款基於Intel Arria 10 GX FPGA的低調PCIe x8卡。該板專為支援大型 FPGA 負載而設計,提供具有高達 1150K 邏輯元件的 FPGA、可選的 10/40GbE 高速網路和高達 16GB 的 DDR4 SDRAM,所有這些都使其成為基於伺服器的應用的理想選擇。OpenCL 支援支援類似軟體的高級開發流程,從而大大簡化了 FPGA 開發。

A10SA4採用BittWare的Spider平台設計,這是一個針對散熱性能優化的低調PCIe平臺。Spider平臺結合了用於高密度的薄型PCIe外形,運行更大負載的能力以及專為伺服器設計的強大無源散熱器選項。

主要特點

英特爾阿里亞 10 GX 1150

QSFP28 用於 10/40 Gbps

OpenCL BSP

視頻

了解有關 A10SA4 卡主要功能的更多資訊。

框圖、數據表和規格

想要瞭解更多詳情?

Request the Hardware Reference Guide (HRG)

The HRG gives you much more detail about the card such as block diagrams, tables and descriptions.

規格

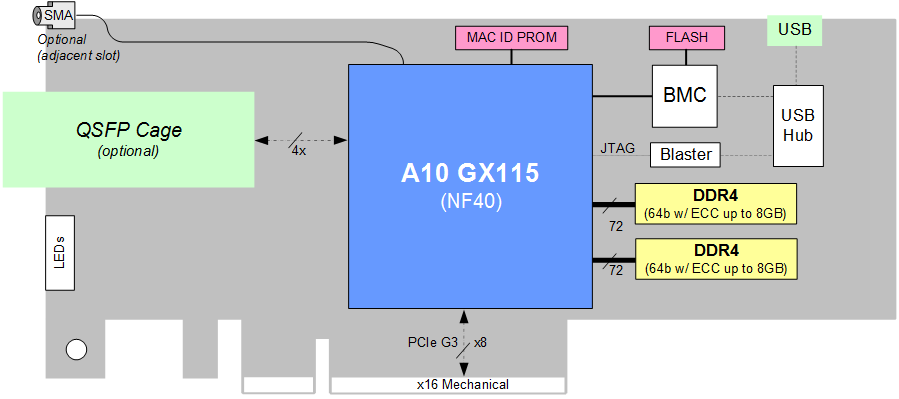

FPGA

- 英特爾阿里亞 ® 10 GX115 FPGA

- 提供高達 1150K 的邏輯元件

- 多達 3,300 個 18x19 可變精度乘法器

- 高性能、多千兆位收發器 @ 高達 17 Gbps

板載記憶體

- 兩個帶 ECC 的 DDR4 組,每個組最多 8 GB (x72)

- 支援多個啟動映像的快閃記憶體

- 用於訪問主機板 MAC ID 的 PROM

PCIe 介面

- x8 第 1 代、第 2 代、第 3 代

- x16 機械介面

USB

- USB 2.0 介面,用於 FPGA 和快閃記憶體 的 除錯和程式設計

- 內置英特爾 USB 衝擊波

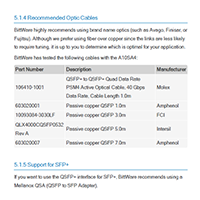

QSFP 保持架

- 前面板可選 QSFP 保持架,支援 40GbE 或 4 個 10GbE

- 可選擇用作 SFP+

電路板管理控制器

- 電壓、電流、溫度監控

- 電源排序和複位

- 現場升級

- FPGA 配置和控制

- 時鐘配置

- I2C 總線接入

- USB 2.0 和 JTAG 訪問

- 電壓超控

大小

- 薄型(半高、半長)PCIe 插槽卡;x16 機械

- 168毫米 x 68.9毫米

- 最大元件高度:14.47mm

Development Tools

系統開發

- BittWorks II Toolkit - 用於BittWare硬體的主機,命令和調試工具

FPGA 高密度脂蛋白開發

-

- FPGA 開發套件 - 範例 Quartus 專案

- 英特爾工具 - Quartus II 軟體

開放CL開發

-

- OpenCL 開發人員捆綁包 - BittWorks II 工具包、主機板支援包、面向 OpenCL 的英特爾 SDK、英特爾 Quartus II

對定價或更多資訊感興趣?

我們的技術銷售團隊隨時準備提供可用性和配置資訊,或回答您的技術問題。

“*”表示必填欄位