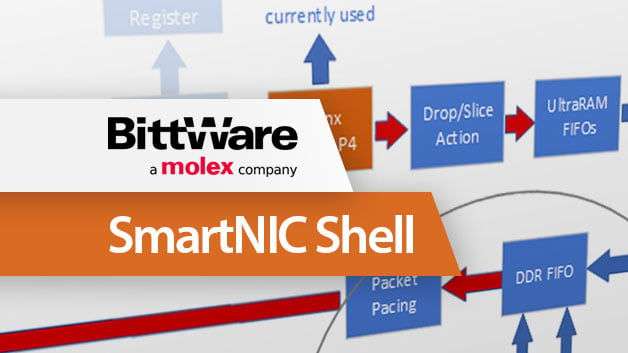

Introduction to BittWare’s SmartNIC Shell for Network Packet Processing

White Paper Introduction to BittWare’s SmartNIC Shell for Network Packet Processing Overview SmartNIC Shell is a complete working NIC that is implemented on a BittWare

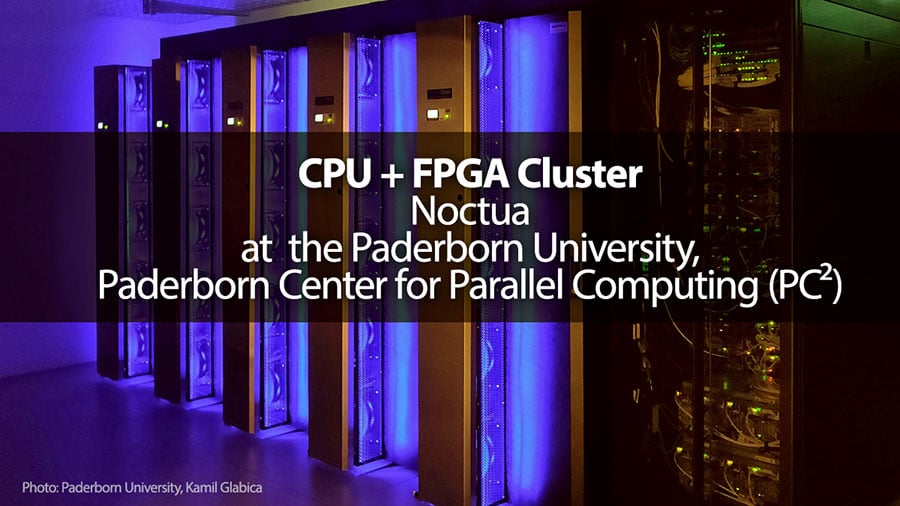

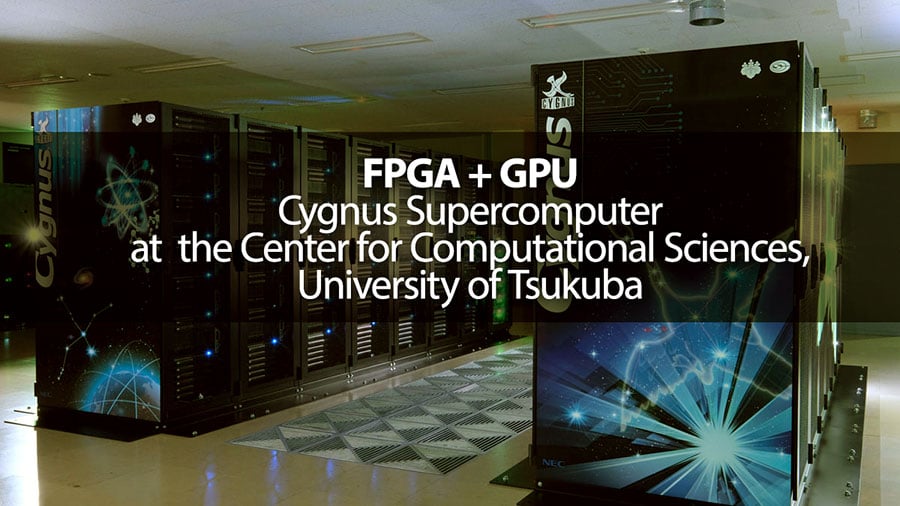

FPGAs offer high performance, workload flexibility and energy-efficient operation for a range of HPC applications.

The FPGA value proposition for HPC has strengthened significantly in recent years.

These are key advantages emerge as demonstrated in our BWNN white paper:

Working alongside CPUs, FPGAs provide part of a heterogeneous approach to computing. For certain workloads, FPGAs provide significant speedup versus CPU—in this case 50x faster for machine learning inference.

FPGAs have a range of tools to best tailor to the application. The hardware fabric adapts to use only what’s needed, including hardened floating-point blocks when required. For BWNN’s weights, we used only a single bit, plus mean scaling factor, and still achieved acceptable accuracy but saving significant resources.

Power per watt is not only important at the edge, it’s in the power budget of datacenters in both space and cost of power. FPGAs can uniquely deliver the latest efficient libraries yet at far lower power per watt than CPUs.

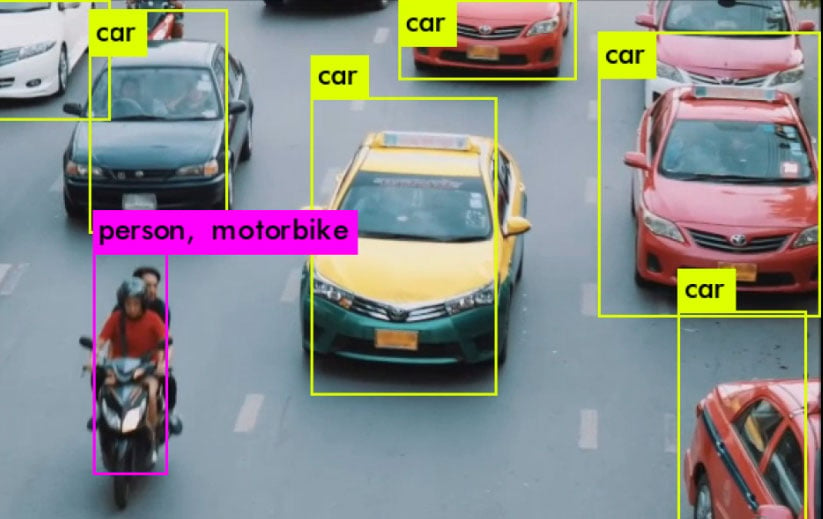

With BittWare’s exclusive optimized OpenCL BSP, you’re able to both tap into software-orientated developers and the latest software libraries. This allowed us to quickly adapt the YOLOv3 framework, which has improved performance over older ML libraries.

We target applications when demand to process storage outpaces traditional architectures featuring CPUs.

FPGAs allow customers to create application-specific hardware implementations that exhibit the following properties:

Get answers to your HPC questions from our technical staff.

"*" indicates required fields

White Paper Introduction to BittWare’s SmartNIC Shell for Network Packet Processing Overview SmartNIC Shell is a complete working NIC that is implemented on a BittWare

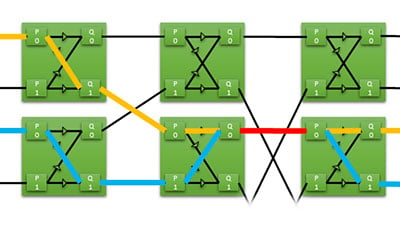

Efficient Sharing of FPGA Resources in oneAPI Building a Butterfly Crossbar Switch to Solve Resource Sharing in FPGAs The Shared Resource Problem FPGA cards usually

FPGA Server TeraBox 1400B Family Extreme Density Standard-Depth FPGA Servers Choice of AMD EPYC 7002 series or Intel 3rd Gen Xeon CPU Overview At the

Go Back to IP & Solutions TCP/IP Offload Ethernet IP The TCP/IP (Transmission Control Protocol/ Internet Protocol) is an Ethernet IP core for FPGAs that