白皮書

時間戳

概述

憑藉我們 FPGA 產品的高速功能,時間戳可能是一個挑戰。BittWare提供一系列解決方案,包括專用附加模組,如A10PL4定時套件(如圖),基卡上的同軸輸入以及對IP的支援,如原子規則 TimeServo。

許多BittWare FPGA卡提供兩個同軸輸入。一個輸入用於1 PPS時間同步信號。另一個是10 MHz參考時鐘。這種組合使得將非常準確的時間戳附加到輸入數據成為可能。BittWare還提供了由IEEE-1588 PTP協定控制的100 GbE乙太網數據包時間戳的示例實現。BittWare的SmartNIC Shell參考設計使用我們從Atomic Rules授權的FPGA內部的時間伺服器。

兩個同軸輸入是卡使用者許多時間戳系統配置所需的全部輸入。下面的段落詳細介紹了我們提供的內容以及它的準確性。

時間舵機

AMD 的乙太網 MAC 可以應用時間戳。但是,AMD IP 希望使用者提供準確的時間戳,然後 MAC 會將其與流經的每個數據包相關聯。創建和維護準確的時間戳由使用者提供的IP負責。

簡單地說,實現這一點可以很簡單,只需提供一個連接到 250 MHz 時鐘的遞增 4 納秒的計數器即可。這種實現將像電路板上的晶體一樣準確。很難與一天中的時間同步。通過允許外部 1 PPS 信號每秒複位計數器的一些最低有效位,可以提高精度和同步性。但是,如果計數器碰巧比實際時間運行得更快,則這樣做會導致時間戳向後流動。眾所周知,向後時間戳會破壞一些流行的應用程式軟體;因此,更好的解決方案是以某種方式使用1 PPS信號來減慢或加快FPGA的時間戳時鐘。這就是時間伺服的作用。

時間伺服實現可以使用外部硬體。BittWare的一些薄型卡的精確計時模組選項包含一個基於晶元的時間伺服器。但是,BittWare通常建議用戶考慮FPGA內部的原子規則時間伺服IP。

所有時間伺服器的功能(基於硬體或軟體)由與Linux內核關聯的時間伺服 API 定義。Linux 內核有一個使用者級 API,用於操作時間伺服。該 API 在 Kernel.org 中進行了說明。用戶可以設置時間,按設定的偏移量移動時間,或向上或向下調整時鐘速率。這些是任何時候伺服都應該支援的基本功能。PTP 的Linux實現使用此時鍾 API。不幸的是,BittWare的SmartNIC參考設計沒有乙太網驅動程式,因此無法啟用此Linux協定。請使用 Linux API 作為任何時間伺服實現中預期功能的文件。

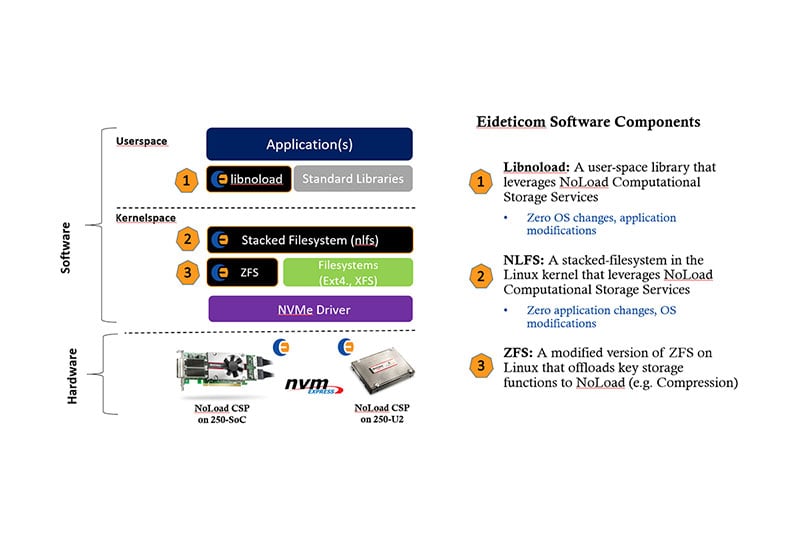

BittWare的SmartNIC支援DPDK。DPDK 具有用於操作時間伺服的使用者級 API。查找rte_eth_timesync_adjust_time、rte_eth_timesync_read_time和rte_eth_timesync_write_time的功能。原子規則為其時間伺服提供了此 DPDK API 的實現。但是,用戶還必須獲取原子規則ArkvillePCIe DMA塊才能使用它。這個DPDK API在BittWare的SmartNIC參考設計中完全實現,適用於願意許可兩個原子規則塊的客戶。最後,原子規則具有完整的PTP實現,可以在FPGA內部運行,而無需在主機上使用乙太網或DPDK。

調整正確的時鐘

我們已經看到使用者在主機上將乙太網埠專用於PTP,然後嘗試將該時間與FPGA板同步。如果您還有 1 PPS 信號進入 FPGA 卡,則此方法有效。否則,這樣做會導致非常不準確的值。問題是 PTP 正在調整 NIC ASIC 內的時間戳時鐘。PTP 不直接調整主機板時鐘。如果沒有這 1 個 PPS,就沒有一種方法可以使所有三個時鐘(NIC、主機板、FPGA)緊密同步。為了在沒有 1 PPS 的情況下獲得時間戳精度,PTP 數據包需要流過 FPGA 卡。因此,使用者需要FPGA的QSFP網路埠之一來為流向任何PTP實現(通過乙太網驅動程式的主機,通過DPDK驅動程式的主機或在FPGA內運行的原子規則PTP)的PTP數據包添加時間戳。

帶商品晶體的PTP

許多BittWare卡上的10 MHz輸入允許使用者提供其應用所需的任何品質的定時參考信號。如果沒有該信號,BittWare的FPGA卡使用具有大約20-30 ppm潛在誤差的商品晶體振蕩器(結合了穩定性,抖動和容差誤差)。因此,FPGA板的時間戳時鐘每秒可以向上或向下偏差20微秒。如果不通過外部信號(1 PPS 或 IEEE 1588)進行校正,則錯誤每天可能累積多達 1.7 秒。這意味著,如果保持(PPS信號丟失)對應用很重要,使用者應連接外部10 MHz時序基準電壓源。

20-30 ppm的潛在誤差與溫度和電壓的廣泛變化有關,這在機房中是不會經歷的。PTP時間同步協定的良好實現將隱藏晶體的容差及其長期誤差分量,使我們主要關注晶體的短期抖動。一些供應商聲稱,在機房中實現良好的PTP,無需補充1 PPS,使用商品晶體,可以實現+/- 1微秒的同步到大師。其他人則懷疑這種程度的準確性是否可以在沒有更專業的硬體的情況下實現。

無論該組合的實際準確性如何,它都可能足以滿足我們所知道的唯一法律準確性要求。歐洲ESMA對自動交易觸發的金融交易時間戳的法律要求是採用UTC,不確定性不超過100微秒。

全球定位系統精度

如果您的應用程式需要與一天中的時間同步,則大多數使用者會利用 GPS 衛星星座中提供的原子鐘。每顆衛星都包含一個銣原子鐘,每年精確到半納秒以上。但是,該時鐘和我們的FPGA板之間有很多電路和氛圍。正因為如此,在幾個小時內,GPS時間信號精確到大約14納秒。不幸的是,大氣效應會在 50 到 300 納秒的 GPS 信號中引入短期抖動。昂貴的GPS接收器可以通過將GPS信號與本地非常精確的時鐘(雙烤箱晶體或原子)混合來消除這種抖動。這樣的接收器需要打開數小時,然後才能在GPS時間信號中提供接近14 ns電位的任何信號。

為了獲得高精度,您必須在GPS接收器和FPGA板之間連接同步信號。對於大多數接收器,這是接收器的 1 PPS 輸出。您需要一個單獨的連接來接收一天中的粗略時間。這種其他連接稱為“時間碼”。最常見的時間碼是通過老式串行埠流動的專有ASCII協定。但是,一些接收器還通過具有AM或直流電平轉換 (DCLS) 傳輸協定 IRIG A、B、G 或 NASA36 的 BNC 連接器提供標準時間碼。當前的BittWare卡不提供直接接收任何時間碼所需的硬體。用戶必須通過主機板的主機傳輸時間碼。

在IEEE-1588安裝中,通常只有大師直接連接到GPS接收器。將接收器的 1 PPS 信號分發給所有 PTP 消費者的情況非常罕見,將 GPS 10 MHz 時鐘分配給 PTP 消費者的情況更是罕見。因此,在這種安裝方式中花很多錢購買雙烤箱穩定 GPS 接收器是不划算的。誰在乎大師是否將時間保持在 14 ns 以內,而 PTP 的消費者可能同步到只有幾微秒內?

同步多個 FPGA 卡

在某些應用中,使用者尋求在位於小區域(如設備機架)的多個FPGA板之間同步時間戳。在這種情況下,將相同的1 PPS校正信號和10 MHz時間基準電壓源分配給每個電路板是可行的。時間戳有多接近?

讓我們假設我們正在使用標稱時鐘頻率為 400 MHz 的原子規則時間伺服。這意味著每個時鐘週期大約為 2.5 ns。然而,在 100 GbE 時,時間伺服將其輸出異步饋送到 AMD CMAC,其運行頻率約為 322 MHz (3.1 ns)。這些異步信號是如何混合的,目前還沒有很好的記錄。但是,我們進行了實驗,發現此配置中的時間戳值往往落在卡之間的 3-4 ns 以內。

BittWare對10 MHz時鐘輸入的支援是不尋常的。專用數據包捕獲卡通常沒有任何 10 MHz 參考輸入。相反,它們包含一個更高質量的晶體振蕩器。但是,當需要多板同步時,使用公共參考時鐘會有所説明。因此,BittWare方法的準確度稍低(晶體較小),但可以變得更加準確(使用實驗室質量的參考時鐘),並且可以更準確地在多個卡之間同步時間。

智慧網卡參考設計中的時間戳

BittWare的SmartNIC 100 GbE參考設計包括對時間戳的支援。它使用原子規則時間伺服。它使用 DPDK 的 PTP 用戶端範例應用程式來處理 PTP 協定並控制時間伺服。 https://doc.dpdk.org/guides/sample_app_ug/ptpclient.html

智慧網卡管道中有一個密鑰過濾器,用於識別 PTP 數據包。目前,該篩檢程式不包含解析器,因此只能識別「附件F,通過IEEE 802.3 /乙太網傳輸PTP」數據包。此後,BittWare創建了一個解析器,可以部署以支援UDP和TCP上的PTP。

對於時間戳使用者,SmartNIC參考設計中最有用的模組可能是BittWare的CMAC LBus到AXI4-Streaming 墊圈。我們的版本處理所需的時間戳數學。

結論

借助許多BittWare FPGA卡上的現有功能,您可以擁有維護時間戳所需的一切,以達到應用所需的任何精度 - 從“足夠好”一直到“時間實驗室參考”。我們與 Atomic Rules 的合作夥伴關係提供了您的應用程式所需的所有時間戳管道,使卡使用者能夠專注於自己公司的獨特附加值。