小組討論

當今的 FPGA 如何應對數據泛濫問題

從第 5 代到 AI,從 NOC 到邊緣射頻

在下面免費觀看錄像!

揚聲器

布萊恩

感謝您今天參加我們的會議。我是Bryan DeLuca,還有Nicolette Emmino,我們今天將成為您的主持人,參加由貿澤電子,BittWare和Molex贊助的即時聊天“當今的FPGA如何馴服數據洪流問題”。

我們有一些很棒的小組成員,這是一個即時聊天,所以請確保在螢幕底部的問答中提出問題。現在到尼科萊特。

尼科萊特

嗨,夥計們。再次感謝您加入我們。我們和三位小組成員,BittWare的首席技術和戰略官Jeff Milrod一起在這裡。Steven Bates,Eideticom首席技術官。Shep Siegel,Atomic Rules首席技術官。

這三位專家將通過硬體和軟體IP的具體示例討論這些新興解決方案,重點是FPGA解決方案。

所以,讓我們潛入其中,我們將從一點背景開始。夥計們,你們怎麼看?

所以你為什麼不告訴我們——你知道,謝普、傑夫、斯蒂芬——你為什麼不告訴我們這三個組織......您合作過一個新計劃?我們為什麼不談談它如何為市場服務以及你們做什麼?

傑夫

好吧,好吧,我將開始接受它,因為BittWare幾十年來一直在使用FPGA製造硬體平臺。我們所做的本質是這些應用程式的平臺。我們是平臺方面的專家,但在應用程式和工作負載方面卻不那麼多。從歷史上看,我們一直向客戶出售我們所謂的「裸機」,他們是FPGA編碼和開發應用程序的專家。

我們發現,客戶越來越不願意做FPGA程式設計的所有艱苦而繁重的工作。我們還與IP和解決方案供應商(如Shep和 Stephen)合作,在我們的硬體平臺之上提供穩定且經過驗證的增值服務。

夏普

是的,傑夫,這很好,我會跳到這裡。因此,在Atomic Rules,我們作為FPGA社區的服務和IP供應商,它沒有硬體,我們在BittWare中沒有更好的合作夥伴,提供擁有來自所有重要供應商的尖端FPGA的平臺,以便我們的IP能夠以最好的方式展示。

Jeff和BittWare/Molex對IP的需求直接滿足了我們對擁有一個平臺來提供我們希望帶給客戶的價值的需求。斯蒂芬?

斯蒂芬

是的,我當然會跳進去。所以,一位偉大的人曾經說過,你知道,對於一台計算機......一個計算機系統要真正發光,你需要兩樣東西:你需要好的硬體,你需要好的軟體。對於那些遊戲玩家來說,一個很好的例子是你可以去構建一個很棒的遊戲PC,但是你需要遊戲開發人員編寫軟體來運行該硬體,對吧?

因此,當您擁有良好的硬體和軟體時,您將獲得客戶的最佳體驗。就像Jeff在演講時提到的那樣,我們Molex / BittWare在構建出色的硬體方面非常出色。他們可以構建市場上最好的FPGA卡,但他們和客戶越來越無法開發真正使硬體大放異彩的出色軟體。

這就是像Shep's和我這樣的公司介入的地方。因此,我們致力於開發在FPGA上運行的軟體,但不僅僅是這樣。此外,在主機系統上運行並將其連接到應用程式的軟體,無論是存儲應用程式、網路應用程式還是計算應用程式。我認為它提供了客戶真正想要的完整解決方案:能夠從像Jeff's(BittWare/Molex)這樣的公司,然後是像Shep和我的公司那樣的東西,並且有一些東西可以插入,只是工作,做一些非常非常好的事情。

布萊恩

所以,我們已經談了很多...我們已經討論了很多關於FPGA的靈活性,對嗎?FPGA 的靈活性如何?我的意思是,它們真的變得更容易程式設計了嗎——如果沒有,我們如何使用它們?傑夫,你能和他談談嗎?

傑夫

是的。我認為,它們非常靈活,增加靈活性意味著增加使用難度。而且,你知道,我只是在想,你知道,通過這個 - 我的一個舊公理,你知道,十年或二十年前的問題是“BittWare將這種裸機FPGA硬體賣給了瘋狂的邊緣。誰是真正可以捲起袖子編寫這個靈活的東西的人......現在不是賣給他們,而是與他們合作(笑)。

我會稱斯蒂芬和謝普為瘋子邊緣(笑聲)......然後我們,一起...把一些非瘋子可以以合理的方式實際消費和使用的東西放在一起。FPGA 的靈活性令人望而生畏。它可以做任何事情的事實意味著它本身什麼都不做。所以,你知道,當它打開電源時,它甚至不知道如何使用記憶體或連接到它的主機。

這就是必須做很多工作來構建框架並擁有shell或(不同的人使用不同的術語)的地方,然後應用程式和工作負載可以載入到其中。

但即便如此,應用程式和工作負載,你知道,有這些,你知道,門海(這就是,你知道,現場可程式設計門陣列是FPGA所代表的)......你知道,有數以百萬計的邏輯元素,你如何將它們連接起來做你的硬體演算法和實現是非常具有挑戰性的。隨著他們添加更多選項和強化核心,在該空間中執行特定工作負載變得更具挑戰性。這就是,你知道,我們瘋狂的邊緣夥伴進來的地方(笑)。

夏普

看,不必——傑夫我同意——但它不一定是瘋狂的邊緣。而且所有這些...在過去幾年中,有許多優秀的工具已經成熟,這使得一頭扎進數百萬FPGA的艱巨任務更易於管理。因為工具已經變得更好了,但複雜性——對於那些在應用層面出現問題的人來說,影響FPGA——幾乎是不可能的。這就是為什麼像我這樣的公司,像Stephen和其他公司都有機會在這個生態系統中建立一個平臺,在FPGA的原始蠻力之上。

我在FPGA CAD設計方面的英雄之一Alberto Santelli在ASIC出現的早期談到了基於平台的設計。但是,他在ASIC方面的宣揚和研究已經在FPGA上成為現實。我們經常會使用術語疊加來描述一種功能——也許是Eideticom製造的,也許是原子規則的,也許通話中的一些人正在製作這些疊加——而疊加層充當平臺,分層在基礎FPGA的硬體和軟體之上,使抽象更接近使用者想要實現的目標。

Atomic Rules的業務是提供提供這些平台的產品。也許有人想移動數據,也許有人想做計算存儲,也許有人有其他問題。這些IP核只是在提高交互級別,因此使用 FPGA 進行實際計算的工作不會立即投入到查找表和時序驗證中......只是...所有這些會扼殺發展的細節......但相反,我們可以談論的能力被放大,「哦,您需要將數據從網路移動到磁碟驅動器再到主機?我們知道如何做到這一點,這就是這個電話......”是的,它下面有很多事情發生,但這就是BittWare,Eideticom和Atomic Rules等公司提供的價值。

斯蒂芬

是的。所以,我不太確定我被稱為瘋子的感覺。我的一部分喜歡它,一部分我...

尼科萊特

(笑聲)傑夫,你真的觸動了那裡的神經!

斯蒂芬

我知道你做到了,不是嗎,傑夫?我喜歡說的方式,我喜歡對我的非極客朋友說的方式是,“你知道什麼是極客。好吧,如果你去和一個極客交談,告訴他們我是做什麼的,他們會說我是一個極客。(笑聲)所以我是一個極客平方或兩個極客,或者我不知道。

布萊恩

我正要說同樣的話——這就像極客的平方。

斯蒂芬

所以,我認為傑夫和謝普很好地觸及了它。我的意思是,這些工具在“我如何學習如何使用FPGA”方面變得更好了。但來自供應商的晶元的複雜性也在增加 – 可能比工具的速度更快。

我認為這些年來有很多工作要做,讓沒有FPGA經驗的人更容易讓他們做某事。但這仍然是一個難題,我認為我們從來沒有真正解決這個問題。我們嘗試過為FPGA編寫C型程式設計語言——就像Shep說的:提高抽象層。問題是你經常犧牲性能來獲得這種輕鬆。

所以我認為像Shep和我這樣的公司正在做的是嘗試做更多特定於應用程式的疊加。所以,我們正在製作一些...圍繞靈活性畫一些線。我們說你不能再做所有事情了。你做這個,這個和這個。但是,隨之而來的是高性能可程式設計性。我認為這很有趣。

我知道我們稍後會談到這一點,但我認為真正可以幫助我們的兩件事——就讓FPGA採用得比現在更快而言——是開放標準之類的東西。那麼,我們能否制定基於生態系統的FPGA討論和程式設計標準呢?因此,我們不再鎖定供應商。

然後另一個是開源的。那麼,我們能為FPGA做同樣的事情,就像Linux內核和Linux操作系統對軟體所做的那樣嗎?我們能不能有一個社區來查看代碼,可以作為一個社區來編輯代碼,他們可以讓它變得更好,對吧?我認為這兩件事——我們稍後會談到它們,這非常重要。

傑夫

我想把這個線程帶走一秒鐘斯蒂芬...所以,這是100%正確的。在硬體級別也存在。所以,你知道,現場可程式設計門陣列本身什麼都不做。有邏輯元素,然後是主機介面,記憶體介面,網路介面,BittWare提供了很多示例和shell。

抽象這些框架和基礎平台的舉措之一 - 英特爾一直在推動開放框架堆疊 - 因此BittWare代碼到開放框架堆疊規範,我們在FPGA中實例化和實現PCIe上的主機介面邏輯,網路介面,記憶體介面並構建硬體,以便當您打開它時, FPGA 可以四處行動數據。

現在,你知道,人們使用的其他模型是果凍甜甜圈,現在你知道,應用程式開發人員把果凍和英特爾有特殊的工具,現在他們稱之為 oneAPI,(就像斯蒂芬他們可能不喜歡我使用稱它們為果凍甜甜圈填充物)......還有一個 API 適用於他們的 CPU、GPU 和他們的 FPGA,如果你在硬體層下面有這個 OFS 構建。因此,現在您可以使用英特爾稱為oneAPI的高級語言進行編碼,並使應用程式在配備此開放式框架堆疊(實際上,我認為Open FPGA Stack)的FPGA硬體平臺上運行。

尼科萊特

你知道,你們已經談到了...這個問題有很多。但實際上——我是什麼——我真正想知道的,我想我們觸及了其中的一些是,你知道(我們有一些來自觀眾的問題),但我只想先解決這個問題:你知道,除了我們到目前為止提到的,在我們深入研究之前,FPGA是否有任何新的發展,我們應該在深入研究之前討論,因為有一些問題。有關係嗎?

夏普

是的,我想馬上跳到前面,因為有......有。我的意思是,FPGA長期以來一直處於工藝技術的前沿。但是現在幾年了——三年、四年或五年——我們已經與 Gen3 PCIe 相處融洽,似乎在過去的兩年裡,我們已經跳到了第 4 代,第 5 代——第 6 代指日可待——而 CXL(與這些技術相互依賴)在這方面是正確的。

從AMD/Xilinx,英特爾和其他公司(來自所有FPGA供應商)來看,我們看到SerDes技術肯定足夠成熟,可以處理Gen4,即將交付Gen5(他們的Gen5設備,也從主要供應商發貨)。所以,我想說,從原子規則的角度來看,在與我們的客戶交談時,真正領先的一件事是過去一兩年 Gen4 和 Gen5 的爆炸式增長,而 CXL 就在後面。

而且,當然,不用說,如果沒有支援它的底層SerDes技術,這是不可能的。但是我的簡短回答(我真的向我的同事道歉......我不得不走在它前面,因為它改變了我們的業務)是 Gen4 和 Gen5 今天在這裡。

斯蒂芬

是的,我想今天網路研討會的標題是馴服數據洪流。更高的速度和進給是必要的...就像其中的關鍵部分。您無法將大量數據傳入和傳出 FPGA,無論是在 PCIe 上、CXL 還是乙太網上,那麼 FPGA 做什麼都無關緊要,它就是跟不上,對吧?因此,速度和進給就像一個必要的構建塊。

但我會採取稍微不同的傾向。我認為FPGA和SoC市場真正讓我興奮的一件事是:有兩件事。其中之一是現在能夠放下ARM等公司非常有能力的應用處理器,一些FPGA正在這樣做。所以,你知道,人們...你可以在FPGA上啟動Linux,對吧?...並把它本質上變成一個小伺服器,幾乎就像一個小樹莓派。但是現在你也有靈活性,因為FPGA除了擁有硬化的ARM處理器內核外,還具有這種靈活的邏輯。這使您可以做一些非常了不起的事情。就像想像一個Raspberry Pi,您可以在其中更改Linux正在與之通信的硬體...您可以編寫驅動程式...這很有趣,你可以做一些非常了不起的事情。所以這是一個方面——將Linux引入FPGA的能力,並允許軟體開發人員與硬體進行通信......硬體團隊正在組建。

另一件真正讓我興奮的事情是小晶元技術。因此,您知道,英特爾 FPGA 團隊已經在以小晶元為基礎開展工作。AMD以其伺服器處理器中的小晶元而聞名,因此我們可以期待看到這一點。在包裝內混合和匹配不同元件的能力,以允許更廣泛的SKU風格,我認為這真的很有趣。因此,如果我有一個不需要乙太網的應用程式 - 也許乙太網在小晶元上 - 所以我不需要那個小晶元,這隻是一個打包選項。如果我想要ARM處理器,它們可以在小晶元上,這些小晶元可以存在於不同的進程節點上,從而降低成本。

我們甚至可以考慮將小晶元用於高頻寬記憶體連接等。所以,這幾乎就像...我幾乎可以在不遠的將來看到有一天,我可以去一個網站,點擊“我希望這些小晶元打包並送到我的辦公室”,我可以選擇我想要的東西,Shep可以選擇他想要的東西,Jeff可以打包——你知道它們都是與足跡兼容的——所以傑夫可以在卡片上放任何東西,我們基本上可以在不增加成本的情況下獲得更多的可變性和我認為這非常令人興奮。

傑夫

是的,當然,英特爾的土地,他們使用他們的EMIB互連將小晶元稱為「瓷磚」,他們在這方面做了很多工作。正如你所說,乙太網和速度已經急劇上升,就像Shep推出PCIe一樣,你知道,與此同時,他們正在提高乙太網網络饋送的速度,你知道,高達100千兆和NRZ......100 Gig對不起,PAM4 速度 - 所以,最多可以綁定 400 Gig。現在這甚至不是什麼大問題。

然後在記憶體方面也是如此:外部記憶體介面,DDR5s,然後,正如Steven提到的,內部高頻寬記憶體塊。因此,您可以添加,你知道 - 在一些即將推出的新FPGA上 - 並獲得32 GB的封裝記憶體,該記憶體以非常高速的本地總線連接到FPGA。

正在發生的另一個挑戰(一個值得注意的新發展)是 - 隨著這些速度和饋送,正如我們所說的,在外部晶元上繼續增加 - 在移動所有數據方面存在嚴重限制......人們並行化他們的總線,時鐘速率正在上升 - 但每個人似乎在供應商社區半導體級別採取的另一個非線性步驟是添加片上網路以更高的頻寬移動數據。

這做了兩件事:它允許您在外圍設備之間移動,還允許您在邏輯元件內移動它們。隨著這些邏輯陣列變得越來越大(有數百萬個,很快會有數千萬個邏輯元件),將數據移動到那裡進行處理是很困難的,但現在將相同的頻寬從第一個數據包處理器移動到後處理器......你必須把它一直移動到那個大陣列上——這是NOC可以進入的另一個地方(片上網络:他們稱之為NOC......N-O-C)。

夏普

如果我們轉向NOC,我想跳進去一點——也許我們稍後會回到它......因為NOC是一個大話題——至少不是因為圍繞它們的行銷,不同的FPGA製造商正在使用的強化NOC。我只想...我不想放過原子規則,當然在其他地方,我們真的受到了過去20年來Jan Gray和Nachiket Kapre開發的重裝步兵網路研究的啟發。你可以谷歌它並查找重裝步兵和圍繞它的所有工作。這是一個以軟方式調查NOC及其收益(及其成本)的絕佳平臺,我們從我們自己的軟NOC中的工作中得到了啟發,我們將其用於在沒有適合我們需求的強化NOC的好處的地方進行數據分發。

就像我之前談到的平臺一樣,NOC(硬的和軟的)可以作為該平臺的層來構建您的抽象。Jeff說:“我如何將數據從乙太網端傳輸到PCI端,再傳輸到記憶體端,再到存儲端?”絕對。我認為這隻是另一種類型的抽象,可以打包和捆綁,以減少複雜性,並基本上隱藏一些你不想知道的事情,以便獲得真正有價值的應用程式級細節。

尼科萊特

你知道,我們從觀眾那裡得到了一個關於NOC的問題,特別是一個硬化的NOC。我只想提出這個問題。你可能已經在那裡解決了這個問題,但也許我們可以在這裡填寫它。一位觀眾問道:「不同硬化外設和內部邏輯門之間的硬化NOC如何影響FPGA在過去二十年中缺乏的內部數據路徑的牢度?

傑夫

是的,這是一個詳細的硬體問題,這是一個問題。你知道,我們一直...我非正式地使用了這個術語,你知道,所有這些瘋狂的東西 - 移動所有這些數據 - 有點像管道。而且你必須把它探查起來...如果你想讓你的水進入房子:這是一回事。如果你想把它放在廚房水槽和浴室裡,你知道,你必須把它弄起來。而...這個類比確實適用於FPGA。然後,如果你想從廚房裡流出一點水,那是一回事。但是,如果你的廚房裡需要消防水帶,你需要一種不同的管道結構,對吧?

這就是硬體NOC的用武之地,也是所有供應商現在都在努力解決這個問題的地方。正如Shep所說,他們在外圍設備之間以不同程度的方式擁有它們,只是,你知道,從乙太網移動到PCIe,然後他們可以通過不同的方式將其引入結構中。正如我所提到的,所以如果你有一個 400 GB 乙太網進入一個強化的 MAC FEC......現在它的輸出,你需要在你的邏輯中做一些數據包處理......好的,附上了。現在這個邏輯的輸出,你如何把它移到某個地方?

因此,現在您需要一個可以在結構中訪問的 NOC,並且它們具有這些網路訪問埠。一些供應商正在積極整合這些,一些供應商正在計劃在下一代中整合它們。每個人都在朝著這個方向移動。當然,就像這些技術中的任何一種一樣,即使在行銷幻燈片上,它們看起來有點像仙塵,但細節中總是有魔鬼。他們並沒有解決所有的問題,他們還有其他一些問題,其中之一是你開始在巨大的頻寬和總線寬度下以千兆赫茲的速率切換......事情變得很熱。

NOC往往會增加散熱,因為您翻入的位越多,東西就越熱。而且他們走得越遠,他們的容性負載就越大。但我認為,它們是一個很好的工具,現在正在被社區利用,並且隨後將出現在所有硬體上。

斯蒂芬

而且,補充一點,你知道我喜歡的短語是“從消防水帶裡喝水”。所以,你知道,我們考慮這些令人難以置信的數據洪流速度和饋送。如果你想查看從主機傳入的每個數據包或每個位,你最好能夠使用它,對吧?否則,你實際上是在用消防水帶喝水,這不會有好結果。

所以,我們必須確保我們可以在設備內移動這些數據。我認為傑夫關於熱的觀點——比如事情升溫——這是一個很好的觀點。所以,我喜歡我們與傑夫公司合作的一大好處是,你知道,他的公司非常善於思考熱能之類的事情。

傑夫提出這個問題的事實提醒我這很重要。你知道,在我過去,我編寫過一個FPGA,它並沒有變得很酷——就像沒有風扇吹過它一樣......我炸毀了那個該死的東西!我要承認...也許我不應該(笑聲)! 但是,如果這些東西在他們努力工作時變得如此熱,所以它無所事事地坐在那裡——什麼都不做——那麼它就很高興了。然後我做到了...很多,突然間它變得非常非常熱非常非常快。傑夫,你知道,傑夫的公司也考慮過這一點。

傑夫

但是,您是否得到了足夠熱的焊點,它回流焊點並實際上從板上掉下來?

斯蒂芬

我還沒有這樣做。

傑夫

那時您就知道自己有事情要做!

布萊恩

這很熱,夥計們,這很熱。

斯蒂芬

所以,BittWare和Molex照顧事情真是太好了。這就是他們帶來的體驗,「我們如何讓這些東西保持涼爽,讓他們不知道自己不會死?是的,這真的很重要。

布萊恩

好的,我們一直在談論數據,對吧?讓我們深入瞭解一下。我們在數字領域談論了很多...讓我們也談談感測器內的數據泛濫,對吧?FPGA如何幫助類比世界。傑夫,這可能是一個硬體問題。

傑夫

是的,而且也是超級深的。所以,有兩個快速的答案。

一個是最...BittWare曾經做過很多模擬介面板,並將它們轉移到信號處理資源中......主要是FPGA。

現在有標準化了,所以我們不再這樣做了。通常,當人們在發射器中轉換類比信號或從數位信號轉換為模擬信號時,他們會在無線電頭或感測器頭的某個地方進行轉換。然後他們把它數位化,打包並移動它。

因此,我們現在大多數進行感測器介面和處理的應用——無論是JESD還是VITA49,還是新興的射頻DIFI標準——我們都會連接到一些標準分組協定,如乙太網,只是在移動數據。

另一種方式是(你知道,我們在談論 - 斯蒂芬正在談論 - 關於小晶元和瓷磚)各種供應商現在正在添加類比到數字轉換器和數模轉換器作為斯蒂芬可以只是......順序你知道,在這個顏色上帶有該功能。你可以用ADC或不用ADC來獲得它,而且你可以進行實際的直接模擬介面。

我們有 - BittWare有 - 硬件可以直接接收5 GHz的RF,並將其數位化......強化了下變頻器、上變頻器,然後將其移動到 FPGA 結構中進行後處理。所以這是正在發生的方式之一。

尼科萊特

你知道,我們有很多來自觀眾的問題。我現在要打其中一個。我看看。。。您能從成本的角度談談FPGA在邊緣計算領域的可行性嗎?FPGA 會更適合設備邊緣還是本地邊緣?

傑夫

好吧,成本是带寬和性能等因素之一......你知道,這都是相對的,你知道嗎?當斯蒂芬談論Raspberry Pi時,我有點畏縮,因為這是一個略有不同的價格點。一般來說,FPGA 並不便宜。

你知道,我們的銷售人員,我敢肯定——如果他們在聽這個——現在正在向我射飛鏢。但是自然...前幾天我聽到有人稱呼它的另一件事是 - FPGA是一個現場可程式設計門陣列,但它的另一個術語是一個靈活的,相當不錯的ASIC,對嗎?我喜歡這種方法和那個術語。ASIC的開發成本非常高,一旦開發出來,部署起來就非常便宜,對吧?

FPGA 以不同的方式做到這一點。開發仍然很困難,但它遠沒有ASIC開發那麼昂貴。但是設備本身的經常性成本要高得多。當您想開始擁有PCB和電源以及熱約束時,它們可能是相當昂貴的解決方案。他們...當你得到一個足夠大的東西,價格佔主導地位時,人們就會在ASIC上開車,這隻是一種更便宜的部署方式,市場已經證明瞭這一點。

因此,FPGA非常擅長做一些你無法以更具成本效益的方式做的事情。從這個意義上說,FPGA可以非常便宜,因為無論硬體(以及我們合作夥伴的IP)有多貴,如果你不能以其他方式解決它,並且你正在為你的市場增加巨大的價值並擴大你的可用市場 - 這是一個非常有效的支出。但成本通常不是我們獲勝的地方。

夏普

但Jeff還有其他方式可以讓FPGA帶來價值。我同意你剛才所說的話,但我必須經常指出,儘管FPGA增加了成本——儘管它們增加了複雜性和集成難度——但FPGA被用來卸載可能需要AMD和英特爾昂貴的重型內核的操作,否則同樣的工作。

而淨收益...儘管許多應用程式不會進入這個狀態,「我的工作是減少使用的內核數量。通常是:工作是解決特定的計算問題。但在此過程中,他們最終意識到,支援 FPGA 的解決方案(例如,可能是因為數據從網路移動到記憶體再到存儲的方式有些聰明)必須傳輸更少,並且需要更便宜的重鐵,尤其是在數據中心或本地情況下,而不是在對功耗更敏感的現場情況下......以及節省的成本,“好吧,我需要那麼弱得多的主機處理器來完成它”......是經常性的節省,可用於資助昂貴的FPGA開發和昂貴的電路板...

傑夫

這是一個總擁有成本的事情,我認為斯蒂芬在計算存儲中的應用與此特別相關,你知道,計算存儲解決方案,我認為沒有人會認為它便宜,但比替代品便宜。

布萊恩

我的意思是。。。讓我們談談計算存儲...我還想談談移動數據,對吧?你知道,從你這個人的角度來看——謝普和斯蒂芬。

所以,我不知道你們是否想先談談計算存儲,然後我們可以先返回或移動數據?

斯蒂芬

是的,我會跳到計算存儲。所以,計算存儲 - 正在發生的事情是,你知道,世界正在產生的數據量,它只是呈指數級增長,對吧。我認為企業已經意識到的另一件事是,除非你能分析它並從數據中開發商業智慧和聰明的商業決策,否則這些數據是無用的,對吧。

存儲數據就像,你知道,它沒有那麼多意義。從這些數據中獲得見解現在是關鍵。公司希望快速做到這一點,他們希望有效地做到這一點。因此,他們注意到的是,與其像Shep提到的那樣將一大堆數據放回英特爾或AMD CPU內核並運行軟體,不如將查詢推送到存儲層,並實際讓存儲層運行這些類型的任務。無論是資料庫查詢,還是對一堆感測器數據的AI推理,無論是分析資料庫中的某種業務指標。

因此,標準化正在我們稱之為計算存儲的領域發生。因此,除了擁有存儲數據的盒子或設備之外,我們還如何將計算查詢推送到這些盒子,無論是驅動器、SSD 還是裝滿它們的盒子——比如 NAS,對吧?因此,標準正在圍繞這一點發展,FPGA可以發揮很大的作用,因為就像Shep所提到的那樣,某些任務的效率更高,使用FPGA之類的東西更具成本效益。

但你也想要時間變化。如果查詢發生變化,您可能希望功能發生變化,這就是FPGA真正閃耀的地方:在時間“A”具有特定特性的能力,但您的工作負載可能會在一天中的不同時間發生變化,您實際上希望處理能力改變其特性。這在ASIC上真的很難做到,但用FPGA來說卻非常容易做到。

你知道,計算存儲...還涉及標準。就像我之前提到的,標準(在我看來)推動了市場採用,從而壓低了價格。這總是這樣,對吧?因此,購買一個 FPGA 可能會花費您很多。如果你進來要五十萬,你可能會得到一個更好的每單位價格。

傑夫

是的,還有一點...就像FPGA的其他一切一樣:功能範圍很廣,你可以在Raspberry Pi領域購買FPGA,定價明智,但其中一些,你知道,單晶元超過10,000美元(在極端情況下),BittWare同樣具有廣泛的動態選擇範圍。

因此,在Stephen的計算存儲應用程式中,當人們部署大量計算存儲加速器時,我們可以為我們知道用例的有限應用程式出售一千美元或更少的東西。我們還有其他400個演出的東西 - 這些東西接近數千美元的解決方案。

我們很快就會推出更多的東西,這些 HBM 等等。因此,成本範圍很廣。但是,當我們考慮邊緣和物聯網部署時,它只取決於您認為“很多”的含義。

布萊恩

那麼Shep,你想談談移動數據嗎?

夏普

確定。(笑)

尼科萊特

如果我們談論移動數據,我們可能會在這裡待一段時間,對吧?(笑聲)每個人都系好安全帶!

布萊恩

我們有25分鐘;我們很好,我們很好。

夏普

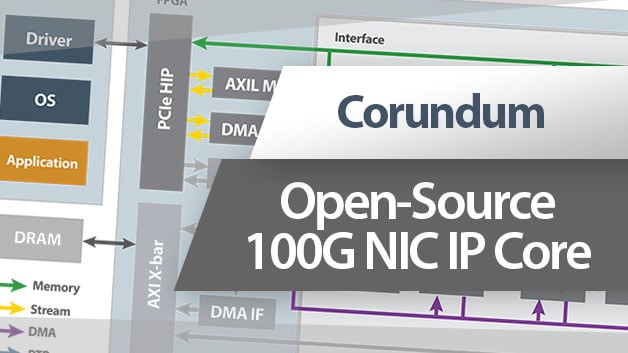

所以,謝謝你的提問。其中之一...我會說原子規則選框IP產品是一個叫Arkville的產品。Arkville是基於DPDK的數據行動器的Atomic Rules品牌。它是一個IP核,可以相對輕鬆地將大量數據從FPGA移動到主機記憶體,或者相反,而無需深入到我所說的基於平台的設計中的大部分較低級別,這對於同時實現高輸送量和相對低延遲至關重要。

這。。。從系統架構的角度來看,數據移動的整個概念非常簡單,對吧?例如,我在FPGA中有數據部分“A”想要獲取數據以將“B”放置在主機記憶體中。軟體工程師可能想打電話給memcpy,或者,你知道,移動數據並讓這種情況發生。

對於我們的客戶,我們的目標是讓這種體驗盡可能接近他們正在尋找的東西。數據從 FPGA 硬體進入使用者土地主機記憶體 — 無需提出任何問題。

是的,它比這複雜得多,但這就是我們的客戶正在購買的。他們認識到,為了完成這個簡單易描述的任務,在它下面,有硬體設計、軟體設計、API 設計、驅動程序設計、FPGA 時序收斂——所有這些部分,在很大程度上,原子規則提供了一個完整的解決方案,如果事實上,從 FPGA 到看起來像主機記憶體的東西的數據移動對你來說很重要,那麼這個解決方案就具有巨大的價值。

斯蒂芬

是的,也許只是為了跳進去補充一下。因此,Shep提到了DPDK,它是網路領域的主機軟體堆棧,旨在將流量從主機記憶體移動到網路或從記憶體移動到記憶體。我在存儲領域工作得更多,具有諷刺意味的是,存儲也與數據移動有關。磁碟上有數據,你想把它放到記憶體里,因為你想處理它,或者你在記憶體中有數據,你想進入磁碟,你想保證它的安全,因為它就像你愛你的貓的照片,你愛你的貓......

因此,有相當多的存儲標準也與數據移動有關。所以,我們和謝普做同樣的事情。我們在FPGA上的硬體中創建這些數據行動器,但隨後我們必須向主機和客戶提供API。我們使用以存儲為中心的產品,而 Shep 使用以網路為中心的產品。

所以對我們來說,它是像NVMe(NVM Express)這樣的東西,今天你的筆記型電腦或遊戲PC中的許多SSD都有NVMe驅動器。另一個是SDXI,這是一個專門為數據移動而出現的新標準。因此,這些允許我們在FPGA上(我稱之為軟體供應商)與主機端易於理解的堆疊集成(在Shep的情況下是DPDK,在我的例子中更像是......像NVM Express或SDXI這樣的東西)。

尼科萊特

好的夥計們,我想談談 CXL。所以,當我們昨天聊天時,你知道,傑夫,你提到這是這些天很流行的話。我認為對我們來說,只提及這一點很重要......談談與 CXL 合作的董事會議程,然後在 Steven 和 Shep 之後,您可以分享一些關於您的想像力將如何處理這樣的事情。

夏普

好的,傑夫?

傑夫

那麼CXL是...當然引起了大家的注意。再說一次,我認為高層次的承諾,如果你閱讀所有的媒體,你知道,有魔法仙塵讓每個人的問題都消失了。但事實並非如此,但它確實是抽象的(它是計算快速連結),它允許將IO /緩存/記憶體抽象和互連到一個單一的連貫域中,任何人都可以看到任何人的信息和數據。

並且有多種實施方式。其中一件事——雖然我確實認為它肯定會改變我們的行業,並極大地影響人們構建和部署解決方案的方式——但在我看來,目前還不完全清楚。我想沒有多少人說,「啊!我明白了——我現在知道如何做所有事情。它開闢了人們以前沒有能力思考的全新維度和能力。我認為會有斷斷續續的開始,人們會嘗試,“哦,讓我們以這種方式連接它。哦,等等,這不太好用。你知道,也許有更好的方法可以做到這一點。

另一件事是,從技術上講,它是伯爵日。因此,我們將在今年年底推向市場的FPGA,我們將支援CXL 1.1。會有...我認為 2 將在 2023 年晚些時候推出。然後 3.0 已經被記錄、計劃和發佈,這更像是 2024 年的時間框架。因此,在硬體級別,將會有演變,並且會演變,你知道,人們在使用 CXL 構建系統方面變得更加聰明。

斯蒂芬

是的,如果我只是跳進去,我的意思是...因此,對於那些不知道的人來說,CXL 是一種在與PCIe相同的布線上運行的協定。因此,如果您查看筆記型電腦、遊戲機或遊戲 PC(任何可以插入 PCIe 設備的地方),理論上,幾年後,您可以插入 CXL 設備。

現在下一個問題是「我為什麼要這樣做?好吧,PCIe 在數據移動方面有一些限制。最大的問題是它不是我們所說的緩存一致性。因此,將數據移動到圖形卡時必須小心一點,其中一些...或通過PCIe連接到網卡。我們的操作系統為我們解決了這個問題。

使用 CXL,它實際上是一個連貫的協定。因此,它使我們能夠做一些 PCIe 無法做的事情。現在,我們仍然可以使用PCIe做很多事情,我們使用PCIe做很多事情。但是,正如傑夫所暗示的那樣,CXL開闢了一些新的範式。

而且,就像他說的,我們不太確定我們要做什麼。但是,根據我在業界看到的情況,許多大型雲公司要做的第一件事就是記憶體分解。他們實際上會將一些記憶體從處理器上的DDR通道移動到CXL卡上,甚至是像超大規模企業(如Google)這樣的人的CXL架子。

現在我的看法是,如果你要這樣做,那麼也許你可以開始放置一些計算服務,這些服務可以在該記憶體上運行,就像我們處理計算存儲一樣。那麼,我們可以將計算推送到記憶體嗎?而且,為了做到這一點,我們可能需要一些靈活的演算法,所以FPGA開始引起我的共鳴。所以,我認為這是FPGA有很大的潛力的領域。

我認為需要注意的另一點是:我們真的不知道它將如何發展 - 所以我們需要靈活性。所以,我認為FPGA在早期就有機會,因為我們不是100%確定我們想要做什麼。因此,我們不會花費5000萬美元來流片ASIC。我們將對FPGA進行試驗。我們可能會以相當大的數量部署它們。我。。。不幸的是,你知道,如果應用程式足夠大,有人會說,好吧,我要在這個上面旋轉一個ASIC。

但我認為存在靈活性的機會,因為工作量確實會發生變化,我對這種潛力感到非常興奮。

夏普

所以,斯蒂芬,所以我有...我想我們許多一直關注 CXL 的人都聽說過記憶體分解將成為 CXL 的“啊哈!”時刻。但是我很難接受分解記憶體對這些記憶體載入和存儲到實際使用它的客戶端的延遲意味著什麼。

我想這是 CXL 必須應對的挑戰,因為你知道,您今天在當代主機處理器上談論的是數十納秒,比 CXL 現在希望克服的那種 SerDes 要達到數百納秒。所以,我個人...我不想打賭,但我不認為這種情況會立即發生。

就我們而言,在原子規則,我們正在做什麼來立即獲得 CXL......英特爾已經通過其 I 系列 Agilex 設備積極走出大門......我們之前在談論小晶元和瓷磚...相應的 R 磁貼(我們今天將其用作 Gen5 Arkville 的一部分......在阿克維爾 22.07 發貨)——我想說清楚,我們沒有 CXL——但支援 PCI Express 第五代的 R 磁貼......我們已經將英特爾並排使用 CXL 和 PCI 的能力,並採取了...如今,很少有客戶需要 Gen5 x16 的完整消防水帶。他們中的一些人當然想要這樣,我們肯定會為他們服務。但是,讓我們說,你知道,100千兆乙太網或多個百兆乙太網或100千兆管道今天比400千兆更受歡迎。

我們已經將這 100 GB 和 400 GB 流分開,這樣今天在英特爾的 I 系列 R 磁貼上,我們可以讓 Arkville 使用 gen5 x8 端點(可用頻寬的一半),並將另一半 R- 平鋪通道留給 CXL。需要明確的是,原子規則為零...目前零產品支援該 CXL 功能。

我們正在密切關注它,因為其他人非常密切,我們認為這需要一些學習。但。。。我們朝這個方向邁出的小動作是沒有採取任何會抑制 CXL 採用的舉措,例如,“你知道,如果你想使用原子規則,那麼你就會走上PCI的道路,你不能用 CXL。我們正好相反。如果您希望 CXL 與 PCI 混合使用,可以同時將它們兩者混合。

布萊恩

因此,這裡有另一個觀眾問題:「您是否預見到更高的光學 I/O(如具有 FPGA 對智慧網卡要求的聯合封裝光學器件)會增長到超出可程式設計可插拔接收器的能力?我想這就是他們的要求。收發器抱歉。

傑夫

答案是肯定的,我希望他們現在就在那裡。我講的一個小軼事是,當我在八十年代開始我的職業生涯時,我和一些人一起工作,他們談論,你知道,這些背板中的所有銅東西都是舊新聞。我們將在未來幾年內轉向光背板和光互連(請注意,這是在八十年代)。當然,這一切都沒有實現。

現在Molex在這方面做了很多工作——這不是我的專業領域,我不熟悉我們在那裡做什麼——但隨著我們越來越快地發出信號,肯定會有一種願望和舉措,將這些東西從晶元中取出到封裝中,從封裝到PCB再到連接器,更有效。

而做到這一點的最終方法在某個時候必須是光子學。這有兩個層次。一種是通過銅以某種方式將晶元連接到封裝中的光學引擎,然後將光學器件插入封裝中。人們談論和工作的另一種方式是將光學引擎集成到矽中。而且你只有一個鐳射...在你的骰子上射出,那是更遠的。我對此瞭解不多,但我希望這是真的......但我不會指望很快。

斯蒂芬

是的,我認為這是小晶元技術的另一個機會。這也是為什麼像UCIe這樣的東西讓我興奮,因為,你知道,矽光子學和類似的東西通常需要與FPGA柔性邏輯想要的完全不同的製造工藝......這也與ARM內核想要的不同......這與類比收發器想要的又不同。

因此,小晶元技術:我們實際上可以選擇不同的工藝,甚至可能選擇非矽基半導體(如果有意義的話),這在矽光子學中經常這樣做。但我同意傑夫的觀點。我敢肯定,Jeff的客戶今天想要最快的速度和饋送 - 這需要光學器件,尤其是晶元外光學器件 - 我們還沒有完全達到目標,但我們需要實現這一目標,因為數據洪流仍在繼續增長。

夏普

是的,但是...光子學有它的位置,如果我們要以這種方式展望未來,它肯定是你必須去的地方。我個人認為,我們正處於一個時代,在過去的幾十年裡,SerDes技術所取得的巨大、真正巨大的進步可以在我們舉手說我們已經完成了類比之前收穫。在這一點上,我們剛剛進入PAM4信令。而且,你知道...我們知道,我們看到了道路的盡頭。

但是有很多機會可以降低功耗,降低複雜性 - 使這些子系統對於 gen5 PCIe 和 CXL 等工作至關重要......工作更輕鬆,價格實惠,不需要 10,000 美元的 FPGA 來承載該基板。而且我認為市場可能會為無聊的老人找到機會......今天的32 GigSerDes,以找到一種方法來降低成本並將其放入更便宜的FPGA中,從而產生看起來更像當今解決方案的解決方案,但功耗更低,成本更低。

尼科萊特

好吧,讓我們回答這個問題。“需要什麼樣的技能才能將裸露的FPGA變成解決特定問題的東西?我怎樣才能利用你們的工作來使我的FPGA部署更加成功?所以我...斯蒂芬,也許你可以拿這個?我認為我們可以在這裡談談夥伴關係,這可能是一個很好的機會。

斯蒂芬

是的。我的意思是,我想,你知道,有幾件不同的事情。你知道,首先,對於任何正在聽這個網路研討會的人來說,“我有點想玩,我想趴下和弄髒FPGA。我會說,你知道,在工具方面已經有了驚人的發展,你知道,基於學術的平臺,用於學習如何使用FPGA。

現在有一個很大的驅動力,使更多的FPGA流程開源 - 供應商中立。有一些很棒的程式,如果你谷歌它們,可以做到這一點。還有一些驚人的在線學習。所以,如果你想學習——比如如果你想成為一個極客,你知道——那裡有非常好的東西,值得挖掘並開始玩。你可以買一個便宜的板...您可以將其連接到筆記型電腦或桌上型機。你可以上網——有YouTube視頻,有免費課程,你可以立即開始玩這些東西,這是一個很好的起點。

現在,如果你對部署FPGA來解決你的業務的特定問題更感興趣,如果你不想自己做,這就是你來找像Shep和我這樣的人的地方,要求軟體提高抽象水準,這樣你的工程師就不必談論FPGA語言。低級FPGA語言是Verilog,VHDL和SystemVerilog之類的東西 - 你知道,它們是計算機程式設計代碼,但它不是C,不是Python。它的水準要低得多。

而且,你知道,我們公司內部的團隊在使用這些語言方面非常有經驗,但這不僅僅是使用這些語言。從建築師的角度來看,這是理解這些東西將如何建造?

我一直認為FPGA就像,當它剛剛打開時,它幾乎就像一個建築工地。你擁有所有這些資源,比如木材,你知道,水泥等等。而傑夫的...

傑夫

別忘了我的管道!

斯蒂芬

...傑夫的公司提供了這一切。所以你出現了...我的公司來到建築工地,說:“好吧,我們有一個廢話(請原諒語言)一大堆材料。我們今天要建造什麼?右?我認為自己是我們公司的那種建築師。所以,我進來,我看看資源,我看看客戶想要什麼,我想,好吧,他們想要一個......他們想要一座摩天大樓。好吧。所以,它將開始看起來像這樣。

我會在我們需要這個塊的高層次上做一些事情。我們需要這個塊。然後團隊進來了,他們更像是......你知道——施工隊。我們團隊中有專家。所以,我們有相當於電工、水管工和腳手架的人。

因此,他們開始一起構建它。到最後,我們實際上在FPGA的網站上有一座建築,我很抱歉這個類比真的很糟糕,但是(笑聲)這就是我的想法。所以,你需要多種技能,對吧?你需要一個建築師...你需要建築工人、項目經理、電工和水管工。

通常,你知道,這些人是具有多年經驗的畢業生水準。我們有一大堆工具來簡化它。然後,最終,它使部署更容易的方式是我們提高抽象級別,我們向客戶提供一個API——無論是Shep的API,還是我們的API,還是像英特爾的oneAPI這樣的基於標準的API,因為它讓他們的生活更輕鬆。

布萊恩

現在,我知道當我們前幾天談論時,我們談論的是Arkville作為數據移動者。您能解釋一下數據行動器和 DMA 引擎之間的區別嗎?

夏普

確定。我們經常得到這個問題。DMA 引擎起源於在計算機上執行數據複製的實際硬體,可以追溯到早期的計算機體系結構:少數計數器、源位址、目標位址......軟體以計數開始,數據從一個地方移動到另一個地方。這幾乎總結了大多數硬體、軟體和系統工程師認為的DMA引擎。

但是,作為數據移動的解決方案,從FPGA到主機記憶體或相反,Arkville不僅包括記憶體緩衝區的低級移動,而且顯然,由於記憶體在FPGA上或記憶體在主機中,它們是抽象的,也許它們是流,也許是流,也許是消息。我們希望呈現像DMA一樣簡單的介面:「哦,這裡源,目的地在這裡,數一數然後去!但是,在這個更高的層次上。

對於硬體工程師來說,這意味著用於將數據傳入和傳出模組的標準行業API。在軟體方面,它意味著一個指向記憶體的標準虛擬指標,因此您可以生成它,也可以使用它。

在FPGA中生成數據並在主機中消費數據或相反的這兩個操作之間發生了什麼?我們不會說我們的客戶不關心那裡發生的事情,但他們希望為他們完成這項工作。他們想要的是運動是如何編排的,以及它是如何進行的。它需要高性能,從某種意義上說,它具有這樣那樣的輸送量,它必須具有這樣的延遲,並且它提供的價值是它是另一個平臺。為他們提供了數據移動平臺,他們可以繼續他們的應用程式。

當然,如果您的需求是專門的,而我們提供的模式不是正確的,正如 Stephen 剛剛所說,“這是一個 FPGA,去做你需要的任何事情;你有這種能力。

我們利用了我們在AXI介面中看到的一套標準,例如在硬體方面或DPDK作為標準的Linux基金會軟體API,並且已經取得了成功,因為有足夠多的人發現,“嘿,我不想自己做。我可以從Atomic Rules購買,也可以從BittWare/Molex購買該板,這對我們有用。

尼科萊特

所以,我們還有大約 4 分鐘的時間,我想知道我們是否可以在結束之前談談最後一件事。如果我們還沒有回答您的問題,請不要擔心BittWare和團隊會有您的問題,以便他們可以在活動結束後解決這些問題。

但我想很快談談開源,以及開源和開放標準對採用基於 FPGA 的解決方案的重要性。所以也許有什麼超級重要的標準,斯蒂芬,也許你可以接受這個?

斯蒂芬

當然,是的。我的意思是,在計算存儲領域,我們正在標準化我們所謂的NVMe(NVM Express)中的命令集 - 希望你們大多數人都聽說過,並且現在可能已經在大多數筆記型電腦中 - 談論計算和存儲。因此,如果我們想要一個可以將計算任務向下推送到 FPGA 的 API,我們將能夠利用這個非常開放的標準。

這樣做的好處是:我不再需要讓我的團隊在Linux或 Windows 中編寫驅動程式;NVMe 驅動器已存在。我知道今天發貨的每台伺服器,今天發貨的每台台式機都支援 NVMe,因為這為我們啟動操作系統並載入遊戲和其他東西的固態驅動器提供動力。

因此,這使我的生活變得更加輕鬆,並且還創建了一個生態系統,因為它不再只是關於Eideticom。這是關於在這個NVMe計算存儲空間中玩的任何人。所以這就產生了競爭,你知道,這不一定是一件好事,但我實際上認為這是一件好事。對我來說更重要的是,它創造了一個生態系統,生態系統推動了採用。採用壓低了價格,從而增加了採用率,你得到了良性迴圈。

所以,我非常相信開源和開放標準。我們在Linux內核和SPDK之類的東西上做了很多工作,SPDK相當於Shep之前所說的存儲(DPDK)。

再一次,我認為在社區內進行協作非常重要,讓許多不同的公司查看代碼,「我們如何讓它變得更好?我們如何使其更安全?我們如何提高工作效率?

再說一次,我認為這隻會帶來更好的採用。我喜歡這樣。

夏普

Stephen 剛才所說的一切——這太棒了——但我還想補充一點:以這樣一種方式回饋社區,使代碼經過審查並變得可信。當然,沒有人想要專有解決方案,所以在GitHub上放置一些在某個地方可用的東西很有趣。

但你知道什麼更有價值嗎?由 Linux 基金會及其各個團體審查您的代碼,以便您的開源部分受到整個社區的信任和審查。我知道Eideticom和Atomic Rules也這樣做了,這個過程對這一切至關重要,因為當信任圈包括業內巨頭時,這些開原始程式碼的價值就會被放大。

布萊恩

好吧,夥計們,我們的時代即將結束。我希望我們有...我們在這裡有很多很棒的問題。大家,感謝您加入我們今天的即時聊天。感謝我們的贊助商貿澤電子、BittWare 和 Molex。感謝我們出色的小組成員加入我們。

尼科萊特

是的,非常感謝。

布萊恩

祝大家有美好的一天。