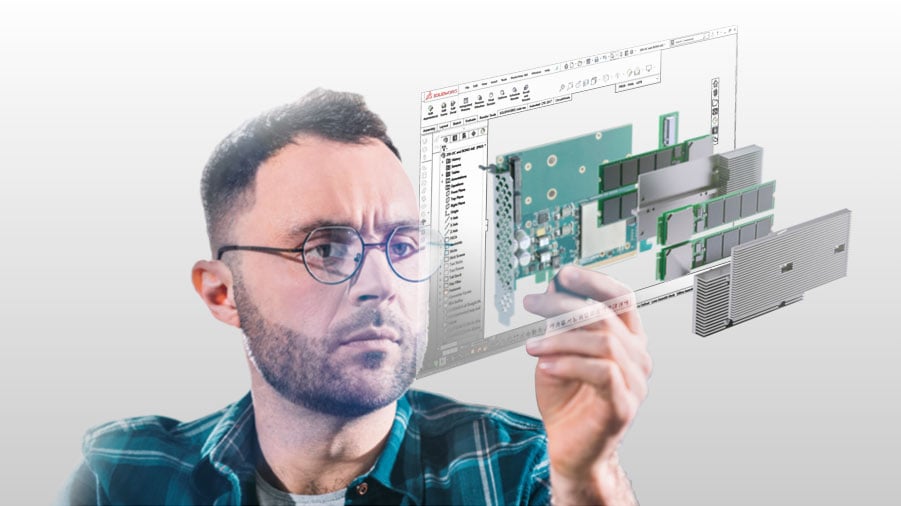

PCIe FPGA 卡

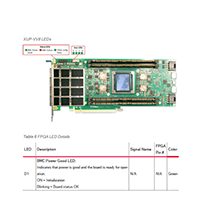

XUP-VV8

UltraScale+ FPGA PCIe 板,帶 4 個 QSFP-DD

8 個 100GbE 網路埠和 VU9P/13P FPGA

概述

XUP-VV8 在 3/4 長度的 PCIe 板中提供大型 AMD FPGA,該板具有 QSFP-DD(雙密度)籠,可實現最大埠密度。使用 Virtex UltraScale+ VU13P 或 VU9P FPGA,該板支援多達 8 個 100GbE 或 32 個 10/25GbE。

FPGA 提供 了 大量 邏輯 和記憶體 資源 — 高達 3.8M 個 邏輯 單元 和 455Mb 嵌入式 記憶體。該板還提供抖動清除器以支援同步乙太網。該板可以配置為單寬度,供 DIMM 上不需要外部記憶體的使用者使用。

主要特點

4 個 QSFP-DD ,最高可達 8 個 100GbE 連接埠

高達 512 GB DDR4 SDRAM

多達 3.8M個邏輯單元

現已推出:

超低延遲 VU9P SCD 4821

- AMD VU9P-3 超低延遲 SCD 4821 FPGA

- 高頻交易應用的理想選擇

- 收發器總延遲 (Rx + Tx) 為 15.54ns,而標準 VU9P 器件為 27.37ns

更快地進入市場 來自BittWare合作夥伴的IP和解決方案

框圖、數據表和規格

規格

FPGA

- Virtex UltraScale+

- 採用 D2104 封裝的 VU9P 或 VU13P

- 核心速度等級 - 2

- 聯繫BittWare獲取其他FPGA選項

板載閃光燈

- 用於引導 FPGA 的快閃記憶體

外部記憶體

- 4 個 DIMM 網站,每個網站支援:

- 高達 128 GB DDR4 x72 帶 ECC

- 高達 576 Mb 雙 QDR-II+ x18(2 個獨立的 288 Mbit 組)

主機介面

- x16 Gen3 介面直接連接到 FPGA

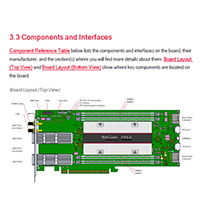

介面埠

- Micro USB:訪問BMC、FPGA JTAG和FPGA UART

時間戳

- 1 個 PPS 輸入和 10MHz 時鐘輸入

奧聯

- 後邊緣有 2 個 OCuLink,每個 OCuLink 通過 4 個 GTY 收發器連接到 FPGA

QSFP 保持架

- 前面板上有 4 個 QSFP-DD 保持架

- 每個都支援 2 個 100GbE、2 個 40GbE、8 個 25GbE 或 8 個 10GbE

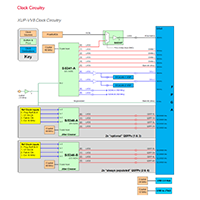

- 用於網路恢復時鐘的抖動清除器

電路板管理控制器

- 電壓、電流、溫度監控

- 電源排序和複位

- 現場升級

- FPGA 配置和控制

- 時鐘配置

- I2C 總線接入

- USB 2.0

- 電壓超控

冷卻

- 標準:雙寬無源散熱器

- 可選:單寬無源散熱器*

電氣

- 板載電源源自 12V PCIe 插槽和兩個 AUX 連接器(8 針)

- 功耗取決於應用

環境的

- 工作溫度 5°C 至 35°C

外形尺寸

- 3/4 長度、標準高度PCIe雙寬板

- 單寬選項*

- 254 x 111.15 毫米 (10 x 4.37 英寸)

開發工具

系統開發

- BittWorks II Toolkit - 用於BittWare硬體的主機,命令和調試工具

FPGA 開發

- FPGA 示例 - Vivado 專案示例,隨 BittWorks II Toolkit 一起提供

- AMD 工具 - Vivado® Design Suite

R0 V0

對定價或更多資訊感興趣?

我們的技術銷售團隊隨時準備提供可用性和配置資訊,或回答您的技術問題。

“*”表示必填欄位