採用英特爾敏捷 ® FPGA 的 IA-440i PCIe 加速器

IA-440i 400G + PCIe Gen5 單寬卡 緊湊型 400G 卡,具有 Agilex 的強大功能 英特爾敏捷x 7 I 系列 FPGA 針對應用進行了優化

我們的第一個合成流量生成器版本僅針對 BittWare的XUP-P3R 和 250-SoC 卡,容量為100 GbE。 我們在為 Achronix、AMD 和 Intel 推出的多速率乙太網硬塊做準備時創建了它。

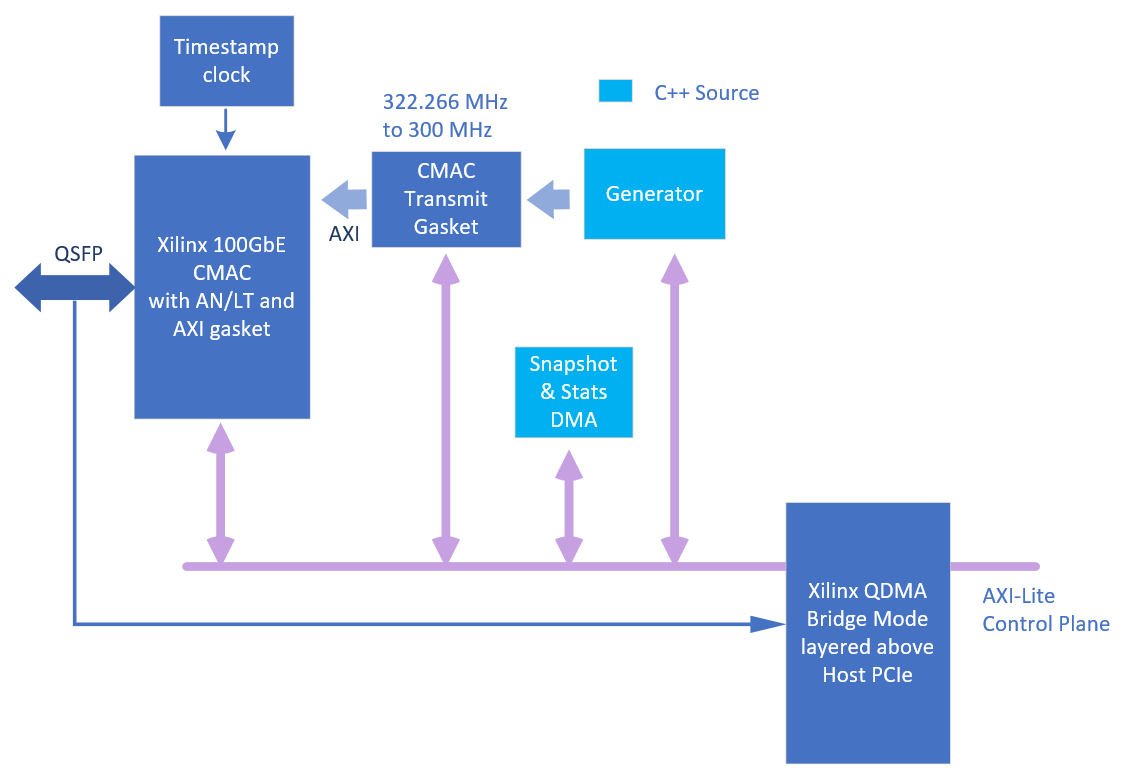

我們將發佈合成流量生成器作為數據捕獲體系結構概念的一部分,從 數據捕獲版本 2.0 開始。流量產生器擁有 QSFP 的傳輸端,數據捕獲擁有同一 QSFP 的接收端。這允許我們將 CMAC 置於本地環迴模式(或安裝環回電纜)以使用流量生成器來測試數據捕獲。它還允許我們使用普通的DAC或光纜將流量發送到其他設備。

BittWare的合成流量生成器在FPGA內創建乙太網數據包,並將其發射到連接的網路中。

如果需要,使用者可以部署BittWare單獨的 PCIe數據採集參考設計 來接收這些數據包。當然,這假設軟體將流量生成器配置為生成IP數據包。

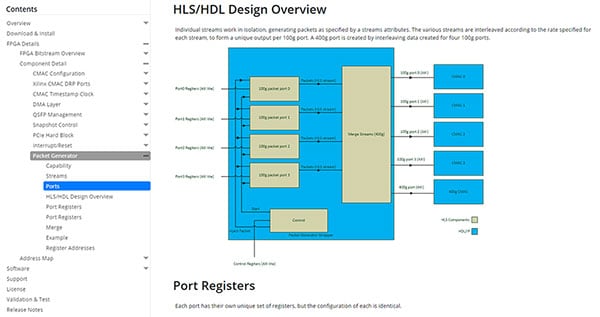

基本思想是長時間以線速創建各種大小的數據包。數據包標頭不會更改。您可以在有效負載中配置遞增的數據包序列號。

您最多可以交錯 32 個這樣的「數據包流」,這意味著您最多可以有 32 個不同的數據包標頭。我們需要此功能來測試將收到的數據包流劃分為多個「佇列」以使用多個主機 CPU 內核進行處理的目標。

您可以配置隨機大小的數據包,但在BittWare,我們傾向於以線速掃描設計,從無窮無盡的一系列小數據包開始,以驗證沒有丟棄,然後向有效載荷添加一個字節,並繼續測試,直到達到目標設計允許的最大有效載荷。

我們還允許使用者將他們想要的任何數據包的單個實例插入到正在進行的流中。這對於插入錯誤以查看發生的情況很有用。

數據包流不需要以線速啟動,因為我們可以定義更長的數據包間間隙,從而降低數據包速率。最後,有效載荷數據可以是零、隨機數、重複的64位元組模式或遞增序列(即0123456789101112...)。

這個合成流量生成器是在BittWare XUP-P3R卡 上創建和測試的,該卡包含AMD VU9P晶元,速度等級為2。流量產生器不使用任何外部記憶體。該設計應該移植到 任何帶有包含CMAC的AMD UltraScale+晶元的BittWare卡中,正如我們通過將數據採集和流量生成器的組合移植到250-SoC中所證明的那樣。

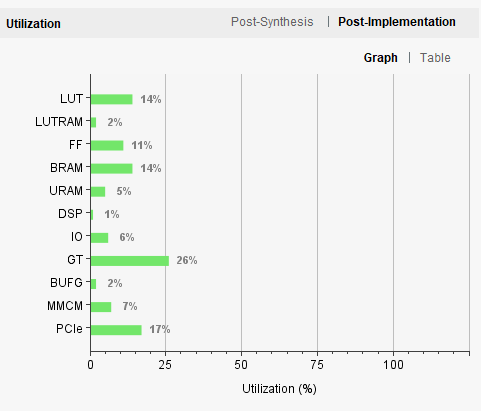

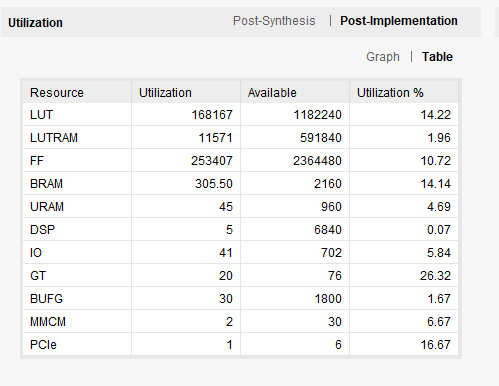

這些圖表顯示了數據採集參考設計候選 2.0.0 版本(2021 年 2 月)的 FPGA 資源利用率。這可能非常接近,如果不是完全是我們最終發佈的版本。

請注意,此位檔包括參考設計流量生成器和數據捕獲。

合成流量生成器集成了與BittWare更簡單的 環回示例所演示的相同DAC電纜功能。

另一個相關專案 StreamSurge不產生流量。相反,它會從本地記憶體緩衝區發送數據包。這些數據包來自主機,使StreamSurge成為更通用的工具。StreamSurge有兩個值得注意的限制。首先,其基於記憶體的設計需要 400 GbE 的專用硬體。具體來說,它需要一張同時具有400 GbE和HBM的卡。其次,構建StreamSurge源需要許可第三方DPDK IP塊。

對於全功能流量生成器,我們希望切換到 Siama PROVA-C 設備,因為它們具有很高的價值,並且使用100 GbE的BittWare硬體。

BittWare的數據捕獲參考設計包括使用此合成流量生成器,目前為100 Gb/s。我們希望分享其功能,包括能夠生成專有的感測器通信量。

要瞭解更多資訊,我們鼓勵您使用下面的表格請求應用說明,這是流量生成器的文檔。

您在此頁面上看到的是BittWare的合成流量生成器的介紹 。完整的應用說明中還有更多細節!填寫表格以請求訪問完整應用筆記的PDF版本。

“*”表示必填欄位

IA-440i 400G + PCIe Gen5 單寬卡 緊湊型 400G 卡,具有 Agilex 的強大功能 英特爾敏捷x 7 I 系列 FPGA 針對應用進行了優化

BittWare 合作夥伴 IP 查詢處理單元 (QPU) 構建 FPGA 驅動的加速器,以 PCIe Gen4 的速度查詢、分析或重新格式化存儲或流數據!艾迪康的查詢

PCIe FPGA 卡 520R-MX Stratix 10 FPGA 板,帶 HBM2 和 480Gbps 光輸入 針對具有大量實時數據攝取要求的感測器處理應用進行了優化