BittWare合作夥伴IP

NVMe 橋接平臺

NVMe 攔截 AXI 流沙盒 IP

計算儲存裝置 (CSD) 允許儲存端點提供計算儲存功能 (CSF),以減輕主機處理負擔並減少數據行動。eBPF 處理、加密、壓縮、文件系統管理和 RAID 等功能非常適合 IntelliProp 的 NVMe 橋接平臺 (NBP) IP 核。

IntelliProp IPC-NV171B-BR NVMe 橋接平臺 (NBP) 利用 IntelliProp NVMe Host Accelerator Core 和 IntelliProp NVMe Target Core 來創建 NVMe 協定橋接。該橋的架構使得命令提交、完成通知和數據傳輸可以不間斷地通過,也可以攔截以進行分析或修改。該架構使用 AXI 流協定連接到「沙箱」區域,以便 IntelliProp 客戶可以在橋中實現自己的自定義 RTL 和/或韌體。

主要特點

具有 AXI 流介面的可定製沙盒

高達 6200 MB/s PCIe Gen4x4

PCIe 交換機支援 多個固態硬碟

Marcus Weddle, BittWare

歡迎觀看我們的視頻,重點介紹 FPGA 加速存儲,重點介紹 IntelliProp 提供的稱為 NVMe 橋接平臺的框架。

今天和我在一起的是IntelliProp的首席執行官Hiren Patel。感謝您加入我!

IntelliProp首席執行官Hiren Patel

謝謝你,馬庫斯——很高興來到這裡。

馬庫斯

讓我們從簡單的構建塊開始。所以我們有SSD存儲 - 非常快的存儲 - 但不是將其插入主機PCIe總線,而是將FPGA放在中間。所以第一個問題是你為什麼要這樣做?

希倫

可能有幾個原因,但SSD前面的FPGA允許構建數據捕獲 - 數據採集系統 - 可以將數據存儲到SSD上,然後稍後通過PCIe從主機讀回。

但同樣,您可以預載入數據採集。你也可以,使用這座橋,你可以攻擊這個正在探索的新市場——它正在增長——它是計算存儲。

我們 能夠 將 某些 加速器 功能 直接 卸載 到 FPGA 中, 然後 FPGA 可以 從 SSD 檢索 數據, 處理 數據, 推 回 數據, 或 將 資料 推 回 主機。所以這可能是目前最大的兩個原因。

馬庫斯

對於數據採集或數據採集,使用 FPGA 有什麼獨特之處?因為。。。還有其他數據捕獲方法...那麼,使用FPGA然後使用這個橋接框架有什麼獨特之處呢?

希倫

是的,又是好問題。在 FPGA 中,將 FPGA 視為空白畫布,對嗎?因此,對於FPGA,我們有很多互連。我們有很多連接點,您可以開始放置其他類型的數據採集,溫度感測器等 - 您可以開始獲取這些數據並將其扔到SSD上。這是主要標準之一。

另一個標準是你在FPGA中內置了強大的處理能力,你現在有ARM內核,你可以放下多個處理器。您可以在數據到達SSD之前對其進行各種處理。

特別是一座橋——為什麼要使用這座橋?網橋主要允許數據通過,因此它可以允許寫入通過,它可以允許讀取通過。但它也可以攔截某些命令。它可以根據需要攔截數據,因此主機可以直接向FPGA發出命令,然後讓FPGA從SSD中檢索更多數據,執行搜索所需的操作,或某種加速功能,然後將數據推送回去。因此,FPGA有很多用途。

我想說的另一件事是,使用FPGA,因為它是如此可定製,你實際上可以使用單個FPGA並將其構建到多個產品中。您可以將 SSD 前面的 FPGA 作為空白產品,然後您可以攻擊不同的演算法或不同的加速度。

一種演算法可能是壓縮,另一種可能是解壓縮,可能是加密。您也可以執行搜索等操作。這些都是針對您特定需求的加速器功能,而不僅僅是一種尺寸。

馬庫斯

所以Hiren,你現在通過框架的橋接元件引入了這個概念,你讓這個主機CPU能夠看到SSD——即使它們直接連接到FPGA——而不是主機PCIe總線。現在,這樣做是有好處的,但這是否需要使用者運行特殊的API,或者他們是否必須修改他們的軟體才能使所有這些工作?

希倫

不,不是開箱即用的。開箱即用,只需在外殼中安裝橋接平臺,您就可以將我們插入主機PC和SSD之間。不,什麼都不需要改變。主機實際上將枚舉 SSD,就像它是直接連接的一樣。

現在,再一次,當您開始進入加速功能或數據捕獲時,您可能需要額外的驅動程式,或者您可以通過供應商的具體情況做所有事情。有一些 CLI 允許您將供應商特定的命令直接發送到橋中 — 橋可以截獲這些命令,然後根據需要處理數據。

馬庫斯

現在讓我們談談具體的BittWare硬體和性能。我認為重要的是要注意,市場上真的沒有那麼多FPGA卡可以直接將SSD連接到FPGA,就像我們在BittWare IA-840f上一樣,你可以在這裡看到。我們還擁有英特爾最新晶元的優勢,該卡上裝有 Agilex FPGA。那麼這些東西可以帶來哪些好處和指標呢?

希倫

是的,當然。顯然,這些較新的 FPGA 正在推動 PCIe 的生成速率越來越快。今天,我相信這些 Agilex 板可以進入第 4 代,而第 5 代即將推出。我認為這些董事會——這本身就是一個巨大的成就。

然後,再一次,通過橋接器,您可以讓第 4 代 x16 走向 PC,然後在背面 - 您有能力聚合多個 SSD。僅在Gen4 x4上使用四個SSD可以幫助飽和其中的一些。

我們還可以在第 3 代 x4 通道上放置八個驅動器來幫助飽和。

因此,我們可以有四個驅動器,八個驅動器回到那裡 - 我們可以有很多驅動器。但基本上所有的流量都通過FPGA,允許我們對其進行計算存儲或數據採集。

馬庫斯

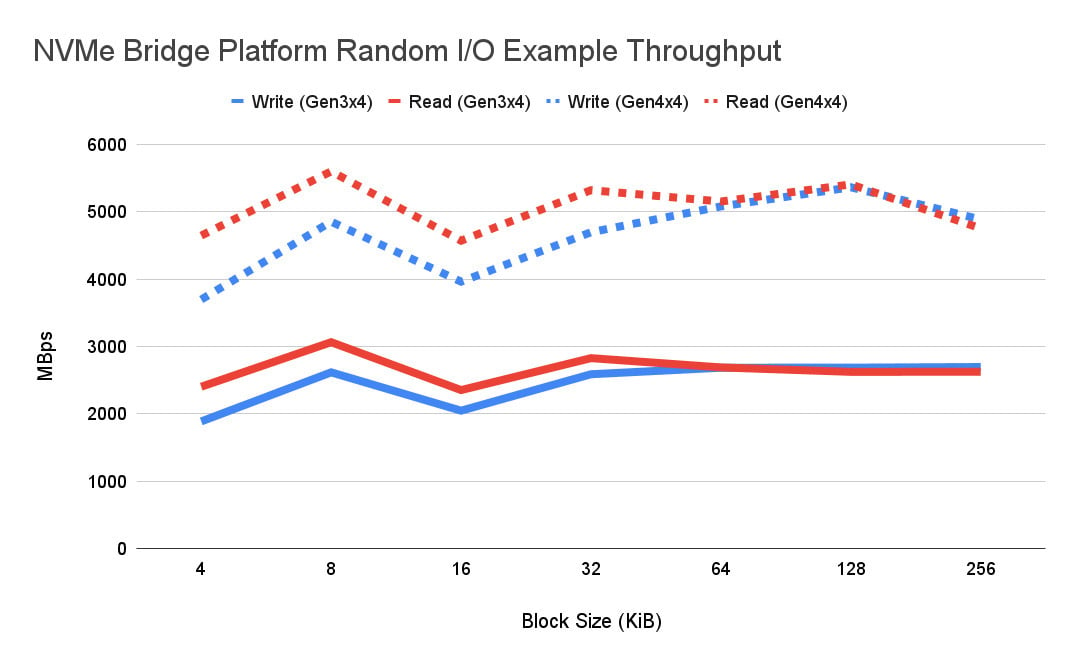

這些頻寬數位是多少?假設您有四個驅動器連接到 FPGA,甚至 FPGA 連接到具有八個驅動器的 PCIe 交換機,那麼在 Gen4 PCIe 級別可以預期哪些性能數據?

希倫

因此,在第 4 代級別,我懷疑它 - 只是在單個驅動器上 - 我懷疑我們應該接近每秒 6,000 兆位元組。在第 3 代速率下,我們已經能夠展示我們的網橋以超過 3,000 的速度運行,接近每秒 3,500 兆位元組。我預計第 4 代會翻一番。

馬庫斯

然後,部署FPGA的人們經常出現的另一個問題是,他們自己的IP與橋接IP一起可以容納多少自己的IP?換句話說,你給別人留了多少空間?所以你能簡單地談談嗎?

希倫

是的,聽起來很棒。在這個特定的板上,我認為那裡有一個AGF027部分。我想說,這部分可能有大約900,000個ALE/ALM。我們用大約 100,000 個作為我們的橋樑。這是針對單個驅動器連接。如果您有多個驅動器連接,則需要添加大約 4,000 個 ALM 來擴展它。

所以是的,還不錯。不過,只有大約10%。因此,客戶仍然有大量的邏輯可用於添加其加速功能。

馬庫斯

Hiren,您提到您可以將一個驅動器或多個驅動器直接連接到卡。現在,如果您想連接更多驅動器,並且該卡可以像八個驅動器一樣進行物理連接 - 具體如何完成?

希倫

我認為即使是一張卡,您也可以連接多個驅動器,然後您也可以將其擴展到可能具有PCIe交換機的背板,然後可以將您連接到其他驅動器。因此,可以將八個驅動器連接到PCIe交換機,然後將PCIe交換機連接到BittWare卡中。所以我認為這是一種可能的解決方案或拓撲,在這裡是可行的。

馬庫斯

讓我們回到我們討論過的第二組用例——這就是FPGA作為內聯加速器的地方。這是計算存儲加速的更大圖景的一部分,它在 CPU 卸載方面變得非常流行。您能告訴我一些用於計算儲存的內聯加速器的用例嗎?

希倫

是的,當然。因此,我們今天有很多客戶在做靜態數據加密。因此,我們的FPGA位於一個或多個SSD的前面,客戶使用我們稱之為沙箱區域或客戶加速區域作為靜態數據加密。但客戶也可以做搜尋引擎,搜索卸載,壓縮eBPF也是另一個增長領域。

因此,這些是客戶可以做的一些事情。如果我們以壓縮或解壓縮為例,您可以使用我們的網橋做一件事——您實際上可以讓伺服器或主機通過網橋將壓縮數據原封不動地發送到 SSD 上。

但是當檢索到這些數據時,你可以在FPGA中內置一個解壓縮硬體引擎。然後,解壓縮引擎可以在將數據發送回伺服器主機之前解壓縮數據,我認為這也是我們看到的一個用例。

其他用例,就像我說的,是eBPF,然後我知道Intelliprop正在研究一些參考設計,所以如果有的話,你知道這是我們看到的另一個用例:eBPF虛擬機。

馬庫斯

您之前提到的一個用例,但我想聽到更多,是讓主機發出搜索命令,然後將搜索本身卸載到 FPGA 和直接連接的 SSD。那麼這是如何工作的,你如何卸載搜索,因為它比卸載壓縮要複雜一些?

希倫

是的,這是一個很好的問題。我們去年11月在聖路易斯舉行的SuperCompute '21上展示的一件事是,我們展示了我們的內聯橋實際上卸載了搜尋引擎。所以我們讓CPU用一堆數據預載入SSD。我們讓伺服器將特定於供應商的命令發送到橋的中間,我們的 RTL 代碼在其中看到特定於供應商的命令,獲得一系列 LBA 或地址空間以進行特定的模式搜索 — 我們還從伺服器接收模式。一旦我們收到要搜索的 LBA 模式和範圍,我們就開始閱讀我們應該讀取的整個驅動器部分,查找特定的 32 位模式,找到它的所有實例(它們發生在哪些 LBA 上),我們將其打包併發送回伺服器主機。

通常,如果沒有我們的加速器,伺服器會將所有這些數據讀取到其系統記憶體中,完成搜索,然後丟棄數據。如果沒有所有這些數據移動,它只需要向我們發出命令,我們只需發回一個回應,說“這是我們找到它的所有位置。老實說,FPGA能夠做到這一點,而且速度要快得多,而且我們的圖表也顯示了這一點。

是的,所以現在我們正在看一些演示。上行顯示 CPU 負載在進行直接搜索時以大約 90% 的速度運行,但在兩者之間,FPGA 卸載版本當然要快很多倍,並且它正在卸載 CPU......我們在這裡使用哪種 FPGA?

所以,是的,視頻中的演示是在英特爾 Stratix 10 DX 上完成的。

人們如何識別何時需要將此特定框架IP與橋一起使用?人們如何識別他們何時特別需要該橋接元件?

是的,這是一個很好的問題。同樣,這是一個直通橋。我們所做的是消除了所有 NVMe 的複雜性 — 我們創建了一個 AXI 流介面,客戶可以將他們的邏輯放入其中。因此,客戶擅長執行加速功能——他們是這方面的專家——他們可能不是 NVMe 的專家,這就是框架真正閃耀的地方。我們將數據和命令以及所有這些作為控制和數據資訊通過AXI流直接呈現到中間,然後讓客戶決定他們想要使用該邏輯做什麼。

另一方面,我們還有一個控制和數據平面 - 再次是AXI流 - 繼續將數據移動到SSD上。

它在兩個方向上都有效,因此在易用性方面,它確實是我們發光的地方。作為客戶——他們的專業知識是加速功能——然後他們可以將其放入沙箱中,然後我們就可以走了。

上市時間要短得多。在BittWare董事會的説明下,我們實際上進一步縮短了這一時間。因為現在他們有了矽,他們實際上可以將沙盒橋插入 - NVMe 橋平臺 - 然後現在他們有一個平臺,他們可以繼續構建他們的加速功能。

馬庫斯

好的,在此基礎上 - 這是我的最後一個問題 - 對於考慮自己構建此NVMe橋接IP而不是使用IntelliProp的觀眾...IntelliProp實際上花了多長時間來做到這一點,現在你擁有使用它來構建應用程式有多容易?

希倫

是的,所以聽起來不錯。所以,這又是一個框架,我只想說我們已經推斷出或隱藏了你必須與NVMe交互的事實。您不必對 NVMe 一無所知。您只需要知道您獲得的位址和控制資訊。

這座橋本身可能花了我們,IntelliProp,大約一年半的時間來開發和正確 - 獲得我們想要的性能。最終,我們為客戶節省了時間。

舉個例子,回到我們做的SuperCompute '21演示,我們在大約一個月內完成了。如果沒有這座橋,我們會花更長的時間。僅僅有了橋,知道了控制資訊——我們得到的數據資訊,就花了我們一個月的時間才真正完成加速搜索功能和發回數據的能力。

所以再一次,它是一個框架,它都是預先構建的,它被沖洗掉了。你只需要專注於你的加速。

馬庫斯

好吧,太好了。謝謝你今天和我談論這一切,Hiren,我很感激。

希倫

謝謝。

馬庫斯

這就是NVMe橋接平臺,這是IntelliProp的一個框架,可以在BittWare FPGA卡上使用。具體來說,我們今天看看帶有直接連接 SSD 的 IA-840F。要瞭解更多資訊,請訪問BittWare網站並感謝您的觀看。

特徵

- 完全符合 NVM Express 1.4c 行業規範

- 使用PCIe硬塊自動初始化

- PCIe 交換機支援多個固態硬碟

- 自動提交和完成命令

- 可擴展的 I/O 佇列深度

- 分離的前端和後連接埠允許靈活的用戶邏輯和應用程式

- 靈活的數據緩衝區類型和大小

- AXI 流驅動命令和資料路徑

- 數據流包括內聯命令參數

- 支援從512位元組到4kB的塊大小

- 應用層介面允許處理器承擔控制或修改管理命令

- Verilog 和 VHDL 包裝器

NVMe 網橋平臺 I/O 輸送量

NVMe 橋接平臺 IP 核心事實

提供 核心

- 文件:全面的用戶文件

- 設計檔案格式:加密的Verilog

- 約束文件:根據 FPGA 提供

- 驗證:模型模擬驗證模型

- 實例化範本:Verilog(提供 VHDL 包裝器)

- 參考設計和應用筆記:綜合、放置和布線腳本

- 附加項目:參考設計

使用的模擬工具:

QuestaSim(聯繫IntelliProp以獲取支援的最新版本)

支援:

自交付之日起 6 個月內,將為完全許可的核心提供電話和電子郵件支援。

筆記:

其他模擬器也可用。請聯繫IntelliProp瞭解更多資訊。

框圖、數據表和產品詳細資訊

應用

NBP IP 可用於具有 PCIe Gen4 主機的計算儲存裝置 (CSD) 或計算記憶體陣列 (CSA),以及通過交換機或單獨的 PCIe 連接實現的多個 PCIe Gen4 SSD。

功能說明

IntelliProp NBP(IPC-NV171B-BR)通過IntelliProp NVMe Target Core接收和解析命令,並將其轉發到IntelliProp NVMe Host Accelerator Core以傳送到NVMe SSD端點,從而實現協定橋接。這兩個內核之間的可自定義橋接邏輯有助於命令管理,包括轉發和跟蹤未完成的命令以及適當地路由數據訪問,而使用「沙箱」區域可在緩衝區數據在主機和目標之間傳輸時提供可見性和靈活性。

橋接邏輯中的寄存器為固件提供了一種機制,用於控制數據移動、手動發出單個命令以及控制橋接功能的狀態和行為。處理器或其他管理代理程式應從 NVMe 目標核心接收並正確完成管理命令,而 I/O 命令由橋接邏輯自主執行。因此,NBP 在主機和端點 SSD 之間提供了透明度,同時為設計人員提供了命令和數據操作方面的靈活性。

空標題

空頭

塊描述

NVMe 目標核心

NVMe 目標核心是標準版本的 IntelliProp 核心 (IPC-NV163A-DT),定義了與 PCIe 核心配合使用的硬體,以實現相容的 NVMe 設備介面。NVMe 目標核心通過PCIe介面從系統主機檢索命令提交條目,並將該條目放入眾多命令FIFO之一中。有兩個數據 axi 流(全雙工),一個命令上下文流和一個完成上下文流。收到命令完成後,NVMe 目標核心會自動填充內部欄位並將完成發佈到主機系統。

NVMe 命令加速器

自動化內部狀態機與 NVMe 目標核心交互,以獲取提交佇列條目並提交完成佇列條目。數據和命令通過 4 個 AXI 流介面呈現給用戶邏輯。從 NVMe 目標核心收到 IO 命令後,NVMe 命令加速器通過 AXI 流轉發命令,然後與 PCIe 端點核心交互,以在使用者系統和 NVMe 主機之間行動數據。集成寄存器允許使用者控制系統配置和內核狀態。

NVMe 命令轉換器

通過 4 個 AXI 流介面與 NVMe 命令加速器協商 NVMe 命令、數據和完成。有兩個數據 AXI 流(全雙工),一個命令上下文流和一個完成上下文流。收到命令后,此塊會分配緩衝區空間以適應來自NVMe SSD的數據傳輸,然後將命令轉發到NVMe主機加速器以發佈到 SSD。從 SSD 傳回資料和 NVMe 完成後,此塊將完成返回到 NVMe 命令加速器並解除分配緩衝區空間。集成寄存器允許使用者控制系統配置和內核狀態。

沙箱

NBP 中的用戶邏輯空間允許用戶靈活地在 NVMe 命令加速器和命令轉換器之間插入自定義邏輯。此邏輯必須符合標準化的AXI流介面,才能傳輸命令、完成和數據。命令和完成可以直接傳遞,也可以在運行時修改(和內部跟蹤)。數據包含內聯命令參數,因此可以與相應的命令上下文分離。如果不限制數據排序或延遲,用戶邏輯可以採用多種形式,具體取決於應用程式。

NVMe 主機加速器核心

NVMe 主機加速器核心是標準版本的 IntelliProp 核心 (IPC-NV164A-HI),並實現硬體以在命令佇列中構建命令,並通過 PCIe 根複雜核心介面通知 NVMe SSD 可用命令。NVMe 主機加速器核心具有硬連線介面,用於設置命令和檢索完成。AXI 從機和 NVMe 主機加速器核心寄存器也可用於允許微處理器設置命令提交和檢索完成。

空標題

空標題

詳細功能清單

整體

- 完整的現成解決方案;開箱即用的操作

- 直接或透過隨附的PCIe交換機支援多個NVMe固態硬碟(或硬碟)

- PCIe Gen4 到主機,以及通過交換機或單獨的PCIe連接實現的多個PCIe Gen4固態硬碟

- 具有用於控制和數據的AXI流介面的沙箱

- 系統附加處理器,提高計算功能的靈活性

沙箱特定

- 四個 AXI 流介面提供命令、補全和數據(全雙工,包括邊帶元數據)

- 處理器連接帶來更多靈活性

- 實施選項包括用於加速的 RTL 或 FW

FPGA/硬體專用

- PCIe Gen4 硬塊預連接

- 最大輸送量為 6200 MB/s(Gen4x4 介面)

- 與英特爾 Quartus 21.3 Pro 工具整合

合成腳本和時序約束

空標題

空標題8

支援的 FPGA 元件

| 裝置 | 速度 | ALUTs | FF | M20k |

|---|---|---|---|---|

| Altera Agilex F 系列 | -2 | 31674 | 22136 | 190 |

| Altera Stratix 10 DX | -1 | 31589 | 20038 | 190 |

交付

核心包括成功實施所需的一切:

- 用於IP核定義的加密可合成 RTL 代碼

- 加密模型類比/探索模擬類比模型

- 全面的用戶文件

- 參考設計

- 範例簡單參考專案包括:

- NVMe 主機加速器IP核心實例

- NVMe 目標IP核心實例

- NVMe 命令加速器

- NVMe 命令轉換器

- 示例沙盒塊

- 處理器

- 記憶

- 合成和放置和路由腳本

- 參考內核控制固件

- 範例簡單參考專案包括:

條款與條件

修改: 通常不允許對IntelliProp的IP內核進行內核修改。請求的任何修改都必須提交給 IntelliProp,以確定集成此類更改的合理性。

支援: 自交付之日起 6 個月內,將為完全許可的核心提供電話和電子郵件支援。

對定價或更多資訊感興趣?

我們的技術銷售團隊隨時準備提供可用性和配置資訊,或回答您的技術問題。

“*”表示必填欄位