採用英特爾敏捷 ® FPGA 的 IA-440i PCIe 加速器

IA-440i 400G + PCIe Gen5 單寬卡 緊湊型 400G 卡,具有 Agilex 的強大功能 英特爾敏捷x 7 I 系列 FPGA 針對應用進行了優化

您可能已經知道 oneAPI™ 是一種更快、更簡單的硬體加速器開發方法,尤其是在 Altera FPGA 上。但是,並非每個應用程式都適用,並且通常需要一些初始開發才能建立基線性能。

您的應用程式能否從 oneAPI™ 中受益?

盯著我們的企業級加速卡是一個很好的選擇。下面顯示了我們支援 oneAPI 的卡片,以及説明您入門的詳細資訊。

想了解有關 oneAPI 的更多詳細資訊嗎?跳轉到我們的“關於 oneAPI 的更多資訊”部分。

準備好獲取硬體或有疑問了嗎?跳轉到我們的購買地點和聯繫方式部分。

憑藉 數十 年提供高級 FPGA 工具的經驗,我們從一開始就知道客戶需要什麼:快速評估設計中的 F-max 等關鍵性能指標。這就是為什麼我們的標準加速器支援包 (ASP) 針對高性能計算進行了優化。選擇支援oneAPI的BittWare加速卡作為起點的一些主要好處。

通過我們的 2D FFT 演示探索使用 oneAPI,而不是採用 HBM2 的 520N-MX 卡。請務必在頁面底部請求代碼下載!

我們推薦這些卡用於 oneAPI,因為我們有最新的工具支援,ASP(以 HPC 為重點),並且每個卡都有一個高性能的 Altera FPGA。

我們採用 Altera Agilex 器件的加速卡都是 oneAPI 支援 的候選 者,但是,如果不選擇推薦的卡,構建 ASP 以評估性能將是一個重要的開發專案。

因此,我們建議您從這些具有 HPC 優化 ASP 的卡開始。我們可以討論其他用於批量部署的平臺。

需要 HBM2 記憶體的強大功能來應用您的 oneAPI 應用嗎?我們的 IA-860m 將被添加到我們推薦的 oneAPI 開發卡中。 準備好后,請與我們聯繫以獲取更新。

在 oneAPI 術語中,ASP(以前稱為板級支援包或 BSP)是橋接 SYCL 代碼和卡硬體的內環。它使功能成為可能,定義了 oneAPI 在晶片上的物理位置(平面圖),並且實際上是特定加速器範圍內性能潛力的決定性元素。

加速支援包 (ASP) 在性能方面起著重要作用。

ASP(電路板供應商的特定 oneAPI 實現)定義了 oneAPI 代碼在晶片和卡級別如何與硬體資源交互。有許多變數可能導致性能降低或提高、矽資源使用量增加或減少,以及可用的 I/O 功能。

在選擇合適的 FPGA 時,考慮您的電路板供應商非常重要。這就是為什麼BittWare專注於高性能的oneAPI ASP開發作為基準--只根據需要添加功能。從性能較低(儘管可能具有更多功能)開始,ASP 可能會導致不太理想的結果,這可能會掩蓋 oneAPI 的實際性能。

客戶可以根據需要自定義更多功能。

如果您需要的功能比我們的 ASP 提供的更多,那麼您已經在使用具有可啟用的附加 I/O 的企業級硬體。可以使用 oneAPI 啟用這些資源,可以與您自己的團隊一起完成,或者 與我們討論 更多自定義選項。

聯繫我們 以獲取報價或建議,以獲得滿足您專案需求的定製 ASP。

您可能聽說過更多與 oneAPI 相關的術語,即開放式 FPGA 堆棧 (OFS) 和 FPGA 介面管理員 (FIM)、加速器功能單元 (AFU)。這些與加速器支援包 (ASP) 有何關係?為什麼您有時會看到對主板支援包 (BSP) 的引用?

OFS 是最高階的元件,但重要的是不要將 oneAPI 視為包含 OFS 提供的所有元件。這種實施既不節省資源,而且難以維持。最好將 OFS 視為一個廣泛的功能庫,而特定的 oneAPI 實現則提供其中的子集。

這就是為什麼在比較各種“支援 OFS”板時,這併不能為您提供有關實現哪些功能、性能或資源使用方式的太多資訊。您必須進一步深入研究 ASP(以前稱為 BSP)是如何實現的。

下一個「降級」由FIM(FPGA介面管理器)組成。這定義了硬體功能的特定介面,包括 FPGA 本身和 oneAPI 軟體上的介面。您可以將 FIM 視為基於 OFS 的 shell。如果您有 RTL 程式設計資源,則可以在 FIM 中添加/刪除功能。

在 FIM 的「內部」工作的是 AFU,即提供加速的實際演算法或處理單元。你可以把它看作是你的使用者應用程式空間,使用軟體工具進行開發,但硬體實例化的優勢。

最後,ASP 彙集了這些元件:硬體介面以及它們如何與 oneAPI 代碼以及用於開發的 Quartus 等主機軟體工具進行交互。您將看到對 BSP(板級支援包)和 oneAPI 的引用;這是 ASP 的類似術語。將 ASP 視為將 FIM(及其使用者應用程式 AFU 區域)轉換為 oneAPI 目標的元件。

下一步是什麼?從開發到部署的典型流程是什麼?

選擇具有優質 ASP 的正確卡。

並非所有您看到的帶有「oneAPI」廣告的卡片都適合評估。我們選擇在具有 Altera F 系列、I 系列以及即將推出的 M 系列 Agilex FPGA 的卡上實現我們的 ASP。查看我們 推薦的加速器板 清單,並準備好討論最適合您的加速器板。

獲取基礎知識。

有了硬體,您將使用 Altera Quartus 設計軟體(單獨出售)和 oneAPI 工具。通過BittWare,我們有我們的開發者網站來指導你,作為你購買加速器板的一部分。

使用 oneAPI 加快開發速度。

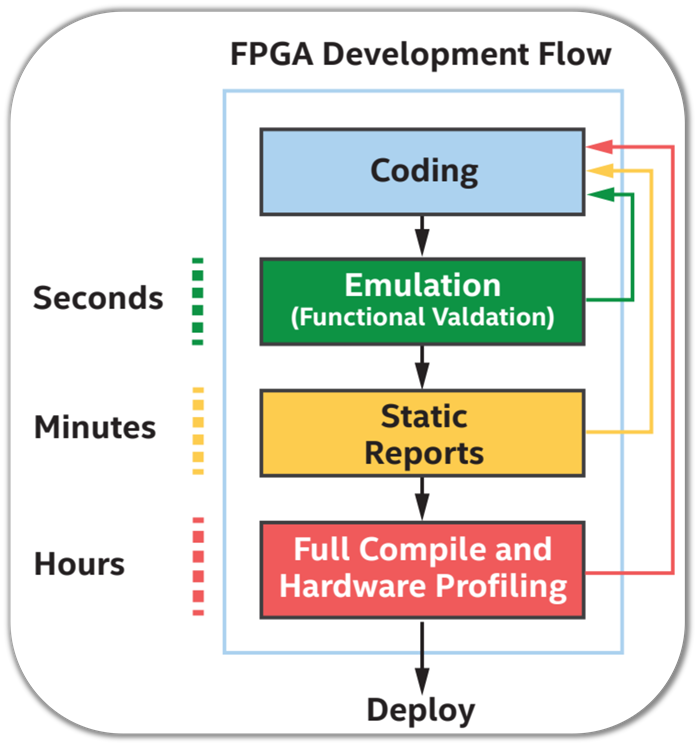

如果您習慣於原生 RTL 開發,那麼 oneAPI 將是一個受歡迎的改進,因為完整編譯運行減少了。借助測試台模擬和報告,這些步驟可在幾秒鐘/幾分鐘內完成。繼續進行完整編譯,您可以使用 Vtune 進一步完善您的專案。

如果你從BittWare加速器開始,這是個好消息。

通過從BittWare加速器開始,你的部署可以在你在開發中使用的同一張卡上!根據您的需求 與我們討論 數量要求。

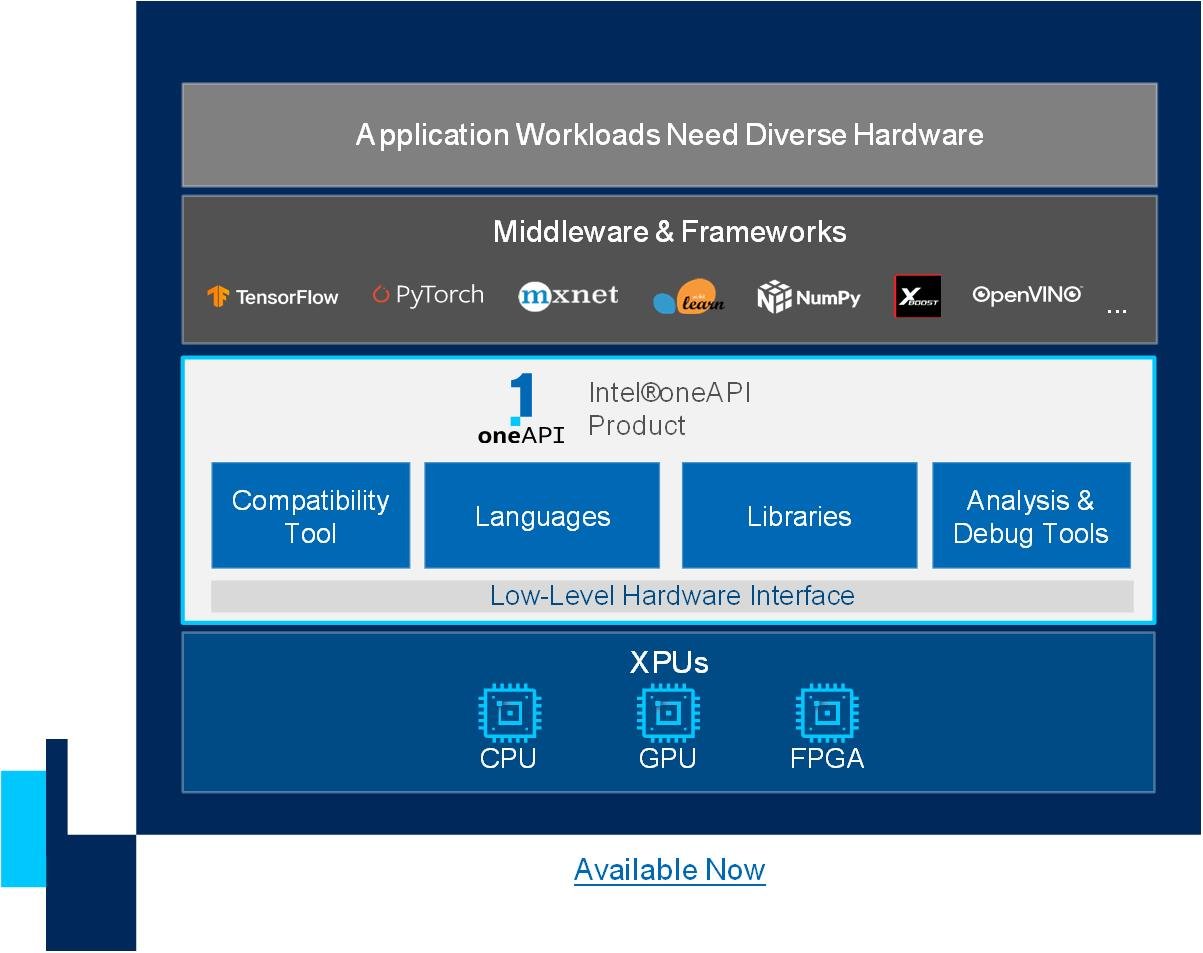

什麼是 oneAPI?

oneAPI 是一種跨行業、開放、基於標準的統一程式設計模型,可在加速器架構中提供通用的開發人員體驗,從而實現更快的應用程式性能、更高的生產力和更大的創新。oneAPI 行業倡議鼓勵在整個生態系統中就 oneAPI 規範和相容的 oneAPI 實現進行協作。

oneAPI 為計算和數據密集型域提供庫。它們包括深度學習、科學計算、視頻分析和媒體處理。

oneAPI 規範擴展了現有的開發人員程式設計模型,通過語言、一組庫 API 和低級硬體介面支援跨架構程式設計,從而實現多樣化的硬體集。為了提高相容性並支持開發人員的生產力和創新,oneAPI 規範建立在行業標準之上,並提供開放的跨平臺開發人員堆棧。

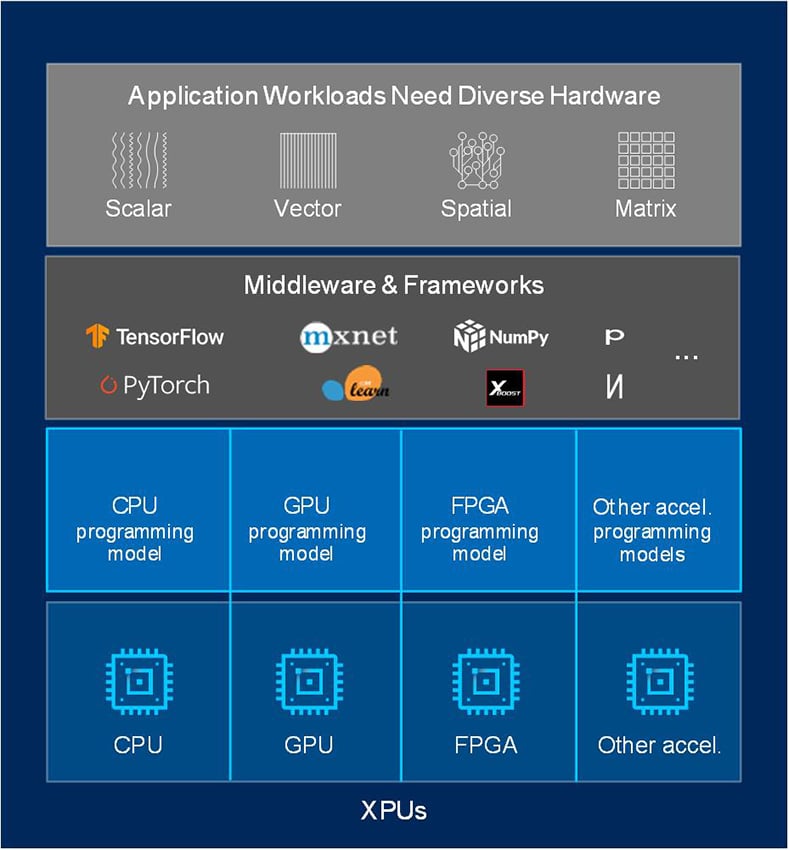

在當今的 HPC 環境中,有幾種硬體架構可用於運行工作負載 - CPU、GPU、FPGA 和專用加速器。沒有一種體系結構最適合每個工作負荷,因此混合使用體系結構可以在大多數方案中獲得最佳性能。但是,這種架構多樣性帶來了一些挑戰:

每個體繫結構都需要單獨的程式設計模型和工具鏈:

軟體開發的複雜性限制了架構選擇的自由度。

OneAPI 提供了一個 統一的程式設計模型 ,可簡化跨不同架構的開發。借助 oneAPI 程式設計模型,開發人員可以針對具有相同語言和庫的不同硬體平臺,並可以使用同一組調試和性能分析工具在不同平臺上開發和優化代碼 - 例如,通過 Vtune 分析器獲取其主機和加速器的運行時數據。

跨平臺和硬體架構使用相同的語言使原始程式碼更易於重用;即使將代碼移動到不同的硬體體系結構時仍需要特定於平臺的優化,也不再需要代碼轉換。使用通用語言和工具集可以更快地培訓新開發人員,加快調試速度並提高工作效率。

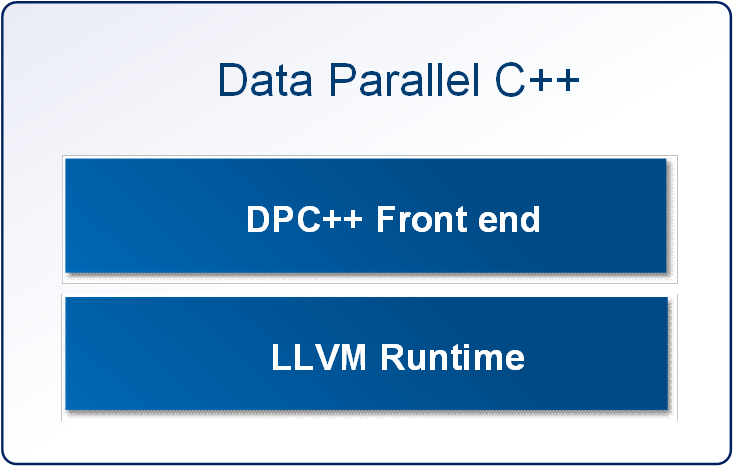

oneAPI 語言是數據並行C++,這是一種高級語言,專為並行程式設計效率而設計,基於 C++ 語言以實現廣泛的相容性。DPC++不是一種專有語言;它的發展是由開放的跨行業倡議推動的。

跨 CPU 和加速器提供不折不扣的並行程式設計效率和性能的語言:

基於C++:

推動語言增強的社區專案:

編譯 FPGA 代碼 時 一個 主要 問題 是 編譯 時間 – 將 DPC++ 代碼轉換為 實現 該 代碼 指定 的 硬體 架構 的 時序 封閉 FPGA 設計 所需 的 後端 編譯 過程 可能需要 數 小時 才能 完成。因此,FPGA 開發流程經過定製,可最大限度地減少完整的編譯運行。

我們的技術銷售團隊隨時準備提供可用性和配置資訊,或回答您的技術問題。

“*”表示必填欄位

IA-440i 400G + PCIe Gen5 單寬卡 緊湊型 400G 卡,具有 Agilex 的強大功能 英特爾敏捷x 7 I 系列 FPGA 針對應用進行了優化

PCIe FPGA 卡 250-SoC 直連加速器和 NVMe-over-Fabric 以低延遲和高輸送量可靠傳輸 NVMe 幀 需要報價?跳

BittWare 網路研討會 使用英特爾敏捷 FPGA 的阿克維爾 PCIe 第 4 代數據行動器網路研討會 來自原子規則的阿克維爾 IP 最近進行了更新,以支援英特爾®敏捷 ™

PCIe FPGA 卡 XUP-P3R AMD UltraScale+ 3/4 長 PCIe 主機板 4 個 100GbE 和高達 512GB 的 DDR4 需要報價嗎?跳轉到定價表已準備好